TPS63020-Q1

SLVSD52A - OCTOBER 2015 - REVISED JANUARY 2016

# TPS63020-Q1 High Efficiency Single Inductor Buck-Boost Converter With 4-A Switches

#### Features

- **Qualified for Automotive Applications**

- AEC-Q100 Qualified with the Following Results:

- Device Temperature Grade: -40°C to 125°C Operating Junction Temperature Range

- Device HBM ESD Classification Level H1B

- Device CDM ESD Classification Level C4A

- Input Voltage Range: 1.8 V to 5.5 V

- Up to 96% Efficiency

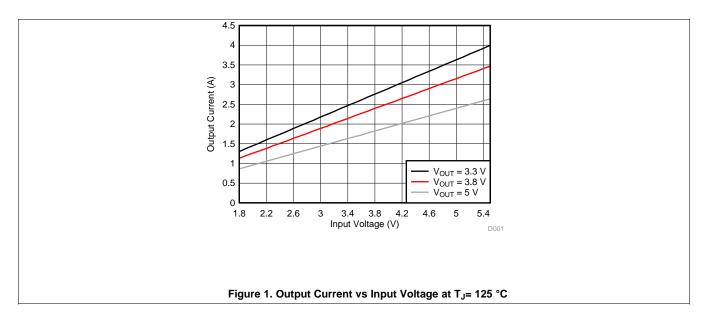

- 3 A Output Current at 3.3 V in Step Down Mode  $(V_{IN} > 3.6 V)$

- More than 2 A Output Current at 3.3 V in Boost Mode  $(V_{IN} > 2.5 V)$

- Automatic Transition Between Step Down and **Boost Mode**

- **Dynamic Input Current Limit**

- Device Quiescent Current less than 50 µA

- Adjustable Output Voltage Range from 1.2 V to

- Power Save Mode for Improved Efficiency at Low **Output Power**

- Forced Fixed Frequency Operation at 2.4 MHz and Synchronization Possible

- **Smart Power Good Output**

- Load Disconnect During Shutdown

- Overtemperature Protection

- Overvoltage Protection

- Available in a 3-mm × 4-mm, VSON-14 Package

## 2 Applications

- Infotainment

- Telematics/eCall

## Description

The TPS63020-Q1 device provides a power supply solution for products powered by either a two-cell or three-cell alkaline, NiCd or NiMH battery, or a onecell Li-Ion or Li-Polymer battery. Output currents can go as high as 3 A while using a single-cell Li-lon or Li-Polymer battery, and discharge it down to 2.5 V or lower. The buck-boost converter is based on a fixed frequency, pulse width modulation (PWM) controller using synchronous rectification to obtain maximum efficiency. At low load currents, the converter enters power save mode to maintain high efficiency over a wide load current range. The power save mode can be disabled, forcing the converter to operate at a fixed switching frequency. The maximum average current in the switches is limited to a typical value of 4 A. The output voltage is programmable using an external resistor divider. The converter can be disabled to minimize battery drain. During shutdown, the load is disconnected from the battery. The device is packaged in a 3 mm x 4 mm 14-pin VSON PowerPAD™ package (DSJ).

#### Device Information(1)

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |  |

|-------------|-----------|-------------------|--|

| TPS63020-Q1 | VSON (14) | 3.00 mm x 4.00 mm |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

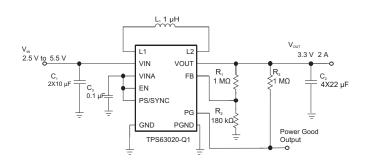

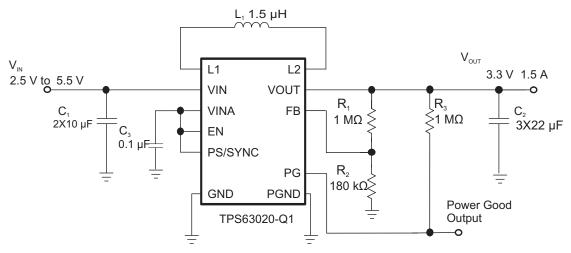

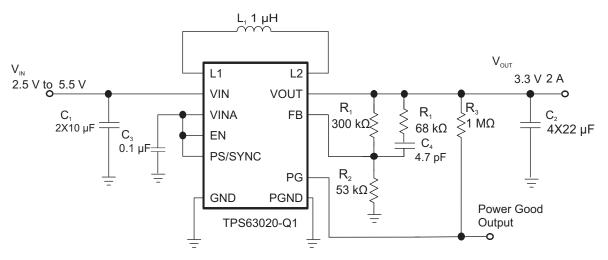

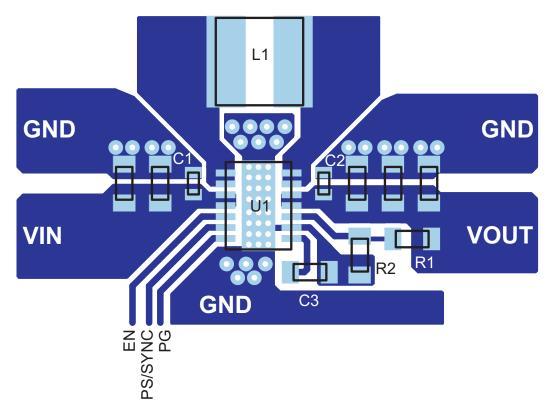

# **Typical Application Schematic**

# **Table of Contents**

| 1 | Features 1                           |    | 9.4 Device Functional Modes                      | 9  |

|---|--------------------------------------|----|--------------------------------------------------|----|

| 2 | Applications 1                       | 10 | Application and Implementation                   | 12 |

| 3 | Description 1                        |    | 10.1 Application Information                     | 12 |

| 4 | Typical Application Schematic 1      |    | 10.2 Typical Application                         | 12 |

| 5 | Revision History2                    |    | 10.3 System Examples                             | 17 |

| 6 | Device Comparison Table              | 11 | Power Supply Recommendations                     | 18 |

| 7 | Pin Configuration and Functions      | 12 | Layout                                           | 18 |

| 8 | Specifications                       |    | 12.1 Layout Guidelines                           | 18 |

| U | 8.1 Absolute Maximum Ratings         |    | 12.2 Layout Example                              | 18 |

|   | 8.2 ESD Ratings                      |    | 12.3 Thermal Considerations                      | 19 |

|   | 8.3 Recommended Operating Conditions | 13 | Device and Documentation Support                 | 20 |

|   | 8.4 Thermal Information              |    | 13.1 Device Support                              | 20 |

|   | 8.5 Electrical Characteristics       |    | 13.2 Documentation Support                       | 20 |

|   | 8.6 Typical Characteristics          |    | 13.3 Community Resources                         | 20 |

| 9 | Detailed Description 7               |    | 13.4 Trademarks                                  | 20 |

| 3 | 9.1 Overview                         |    | 13.5 Electrostatic Discharge Caution             | 20 |

|   | 9.2 Functional Block Diagram         |    | 13.6 Glossary                                    | 20 |

|   | 9.3 Feature Description              | 14 | Mechanical, Packaging, and Orderable Information | 20 |

# **5** Revision History

| CI | Changes from Original (October 2015) to Revision A Page                                  |    |  |  |  |

|----|------------------------------------------------------------------------------------------|----|--|--|--|

| •  | Changed Feature list item Device CDM ESD Classification Level from C4B to C4A            | 1  |  |  |  |

| •  | Changed device number to TPS63020-Q1 in the graphic entities throughout data sheet       | 1  |  |  |  |

| •  | Deleted Eff. vs Input Volt. graph with Power Save Disabled for TPS63021 - not applicable | 15 |  |  |  |

Submit Documentation Feedback

# 6 Device Comparison Table

| PART NUMBER | V <sub>OUT</sub> |

|-------------|------------------|

| TPS63020-Q1 | Adjustable       |

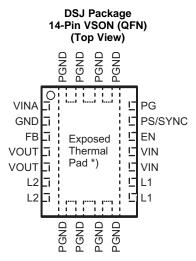

# 7 Pin Configuration and Functions

NOTE: \*) The exposed thermal pad is connected to PGND. See *TPS63020-Q1 Pin FMEA* Application Report SLVA736

### **Pin Functions**

| PIN                    |        | 1/0 | DESCRIPTION                                                                                                    |  |  |

|------------------------|--------|-----|----------------------------------------------------------------------------------------------------------------|--|--|

| NAME                   | NO.    | 1/0 | DESCRIPTION                                                                                                    |  |  |

| EN                     | 12     | 1   | Enable input (1 enabled, 0 disabled), must not be left open                                                    |  |  |

| FB                     | 3      | 1   | Voltage feedback of adjustable versions.                                                                       |  |  |

| GND                    | 2      |     | Control/logic ground                                                                                           |  |  |

| L1                     | 8, 9   | 1   | Connection for inductor                                                                                        |  |  |

| L2                     | 6, 7   | 1   | Connection for inductor                                                                                        |  |  |

| PG                     | 14     | 0   | Output power good (1 good, 0 failure; open drain)                                                              |  |  |

| PGND                   |        |     | Power ground                                                                                                   |  |  |

| PS/SYNC                | 13     | I   | Enable/disable power save mode (1 disabled, 0 enabled, clock signal for synchronization), must no be left open |  |  |

| VIN                    | 10, 11 | 1   | Supply voltage for power stage                                                                                 |  |  |

| VINA                   | 1      | I   | Supply voltage for control stage                                                                               |  |  |

| VOUT                   | 4, 5   | 0   | Buck-boost converter output                                                                                    |  |  |

| Exposed<br>Thermal Pad |        |     | The exposed thermal pad is connected to PGND.                                                                  |  |  |

Copyright © 2015–2016, Texas Instruments Incorporated

## 8 Specifications

### 8.1 Absolute Maximum Ratings

Over operating junction temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                |                                              | MIN  | MAX | UNIT |

|------------------------------------------------|----------------------------------------------|------|-----|------|

| Voltage (2)                                    | VIN, VINA, L1, L2, VOUT, PS/SYNC, EN, FB, PG | -0.3 | 7   | V    |

| Operating junction temperature, T <sub>J</sub> |                                              |      | 150 | °C   |

| Storage temperature, T <sub>stg</sub>          |                                              |      | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 8.2 ESD Ratings

|                    |                                        |                                                         | Value | UNIT |

|--------------------|----------------------------------------|---------------------------------------------------------|-------|------|

| .,                 | Electrostatic discharge <sup>(1)</sup> | Human body model (HBM), per AEC Q100-002 <sup>(2)</sup> | ±1000 | \/   |

| V <sub>(ESD)</sub> |                                        | Charged device model (CDM), per AEC Q100-011            | ±500  | V    |

<sup>(1)</sup> Electrostatic discharge (ESD) measures device sensitivity and immunity to damage caused by assembly line electrostatic discharges

### 8.3 Recommended Operating Conditions

Over operating junction temperature range (unless otherwise noted)

|                                                      | MIN | NOM MAX | UNIT |

|------------------------------------------------------|-----|---------|------|

| Supply voltage at VIN, VINA                          | 1.8 | 5.5     | V    |

| Operating junction temperature range, T <sub>J</sub> | -40 | 125     | °C   |

#### 8.4 Thermal Information

|                      |                                              | TPS63020-Q1 |      |  |

|----------------------|----------------------------------------------|-------------|------|--|

|                      | THERMAL METRIC <sup>(1)</sup>                | DSJ (VSON)  | UNIT |  |

|                      |                                              | 14 PINS     |      |  |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 41.8        | °C/W |  |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 47          | °C/W |  |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 17          | °C/W |  |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.9         | °C/W |  |

| ΨЈВ                  | Junction-to-board characterization parameter | 16.8        | °C/W |  |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 3.6         | °C/W |  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> All voltages are with respect to network ground terminal.

<sup>(2)</sup> JAEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification

## 8.5 Electrical Characteristics

$V_{IN}$  = 1.8 V to 5.5 V,  $T_J$  = -40°C to 125°C, typical values are at  $T_A$  = 25°C (unless otherwise noted)

|                  |                                | PARAMETER                | TEST CONDITIONS                                                                                                        | MIN  | TYP  | MAX  | UNIT |

|------------------|--------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| DC/DC            | STAGE                          |                          |                                                                                                                        |      |      |      |      |

|                  | Input voltage                  | range                    |                                                                                                                        | 1.8  |      | 5.5  | V    |

| $V_{IN}$         | Minimum inp                    | ut voltage for startup   | 0°C ≤ T <sub>A</sub> ≤ 85°C                                                                                            | 1.5  | 1.8  | 1.9  | V    |

|                  | Minimum inp                    | ut voltage for startup   |                                                                                                                        | 1.5  | 1.8  | 2.0  | V    |

| V <sub>OUT</sub> | TPS63020 o                     | utput voltage range      |                                                                                                                        | 1.2  |      | 5.5  | V    |

|                  | Duty cycle in                  | step down conversion     |                                                                                                                        | 20%  |      |      |      |

| $V_{FB}$         | TPS63020 fe                    | edback voltage           | PS/SYNC = VIN                                                                                                          | 495  | 500  | 505  | mV   |

| $V_{FB}$         | TPS63020 fe                    | edback voltage           | PS/SYNC = GND referenced to 500 mV                                                                                     | 0.6% |      | 5%   |      |

|                  | Maximum lin                    | e regulation             |                                                                                                                        |      | 0.5% |      |      |

|                  | Maximum loa                    | ad regulation            |                                                                                                                        |      | 0.5% |      |      |

| f                | Oscillator fre                 | quency                   |                                                                                                                        | 2200 | 2400 | 2600 | kHz  |

|                  | Frequency ra                   | inge for synchronization | 2.0 V ≤ V <sub>IN</sub> ≤ 5.5 V                                                                                        | 2200 | 2400 | 2600 | kHz  |

| I <sub>SW</sub>  | Average swit                   | ch current limit         | $V_{IN} = V_{INA} = 3.6 \text{ V}, T_J = 25^{\circ}\text{C}$                                                           | 3500 | 4000 | 4500 | mA   |

|                  | High side switch on resistance |                          | V <sub>IN</sub> = V <sub>INA</sub> = 3.6 V                                                                             |      | 50   |      | mΩ   |

|                  | Low side swi                   | tch on resistance        | V <sub>IN</sub> = V <sub>INA</sub> = 3.6 V                                                                             |      | 50   |      | mΩ   |

|                  | Quiescent                      | VIN and VINA             | $I_{O} = 0 \text{ mA}, V_{EN} = V_{IN} = V_{INA} = 3.6 \text{ V},$                                                     |      | 25   | 50   | μA   |

| Iq               | current                        | VOUT                     | $I_{O} = 0$ mA, $V_{EN} = V_{IN} = V_{INA} = 3.6$ V, $V_{OUT} = 3.3$ V, $-40^{\circ}$ C $\leq T_{J} \leq 85^{\circ}$ C |      | 5    | 10   | μA   |

| Is               | Shutdown cu                    | rrent                    | $V_{EN} = 0 \text{ V}, V_{IN} = V_{INA} = 3.6 \text{ V}, -40^{\circ}\text{C} \le T_{J} \le 85^{\circ}\text{C}$         |      | 0.1  | 1    | μΑ   |

| CONTR            | ROL STAGE                      |                          |                                                                                                                        |      |      | ·    |      |

| 111/1/0          | Under voltag                   | e lockout threshold      | V <sub>INA</sub> voltage decreasing                                                                                    | 1.4  | 1.5  | 1.6  | V    |

| UVLO             | Under voltag                   | e lockout hysteresis     |                                                                                                                        |      | 200  |      | mV   |

| V <sub>IL</sub>  | EN, PS/SYN                     | C input low voltage      |                                                                                                                        |      |      | 0.4  | V    |

| V <sub>IH</sub>  | EN, PS/SYN                     | C input high voltage     |                                                                                                                        | 1.2  |      |      | V    |

|                  | EN, PS/SYNC input current      |                          | Clamped to GND or VINA                                                                                                 |      | 0.01 | 0.2  | μΑ   |

|                  | PG output low voltage          |                          | $V_{OUT} = 3.3 \text{ V}, I_{PGL} = 10 \mu\text{A}$                                                                    |      | 0.04 | 0.4  | V    |

|                  | PG output leakage current      |                          |                                                                                                                        |      | 0.01 | 0.1  | μΑ   |

|                  | Output overvoltage protection  |                          |                                                                                                                        | 5.5  |      | 7    | V    |

|                  | Overtempera                    | ture protection          |                                                                                                                        |      | 140  |      | °C   |

|                  | Overtempera                    | ture hysteresis          |                                                                                                                        |      | 20   |      | °C   |

Submit Documentation Feedback

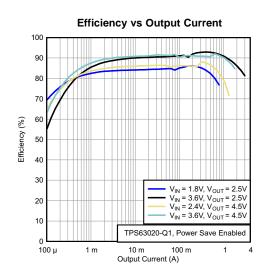

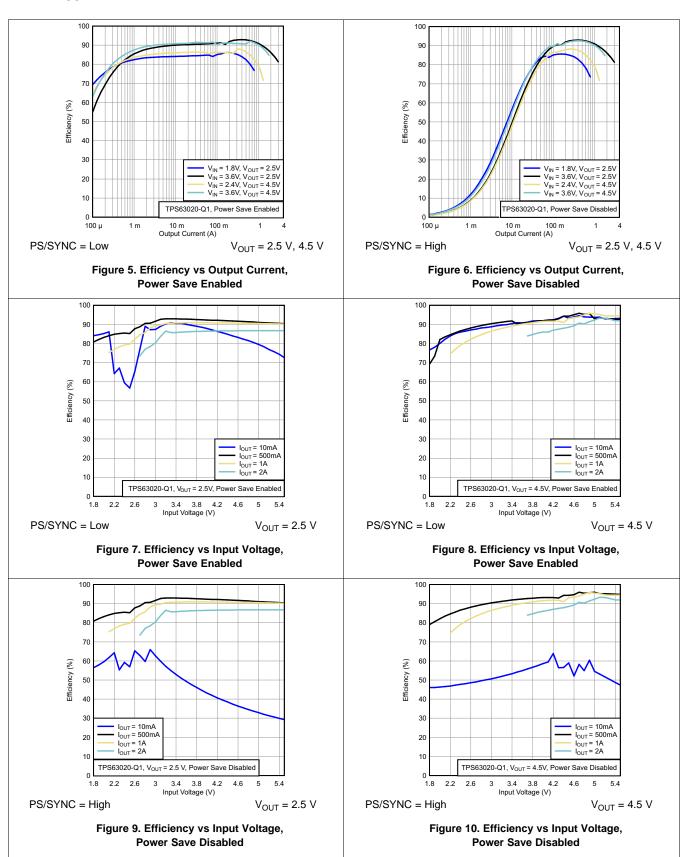

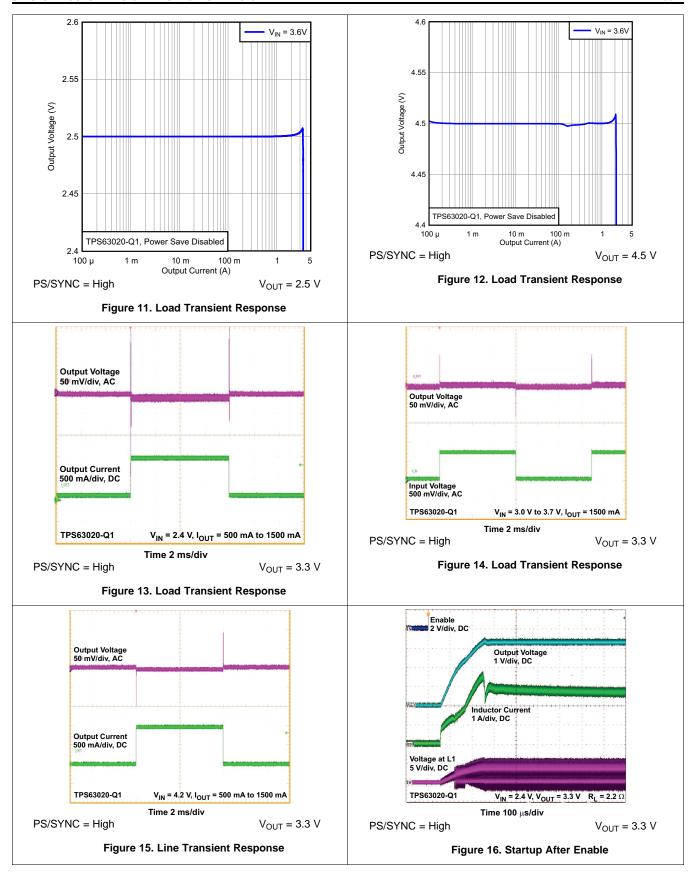

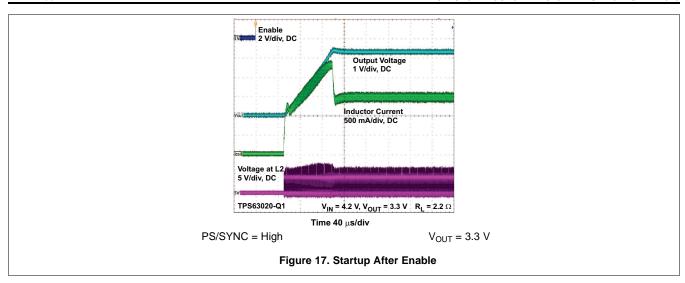

# 8.6 Typical Characteristics

### 9 Detailed Description

#### 9.1 Overview

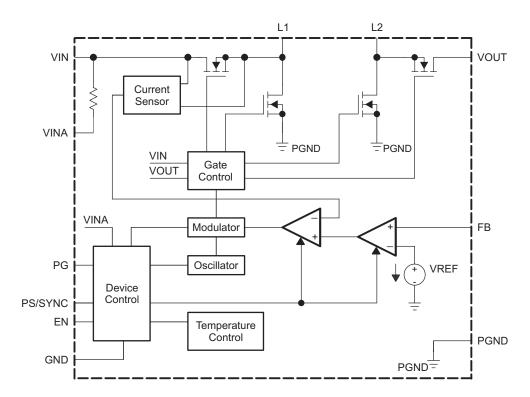

The controller circuit of the device is based on an average current mode topology. The controller also uses input and output voltage feedforward. Changes of input and output voltage are monitored and immediately can change the duty cycle in the modulator to achieve a fast response to those errors. The voltage error amplifier gets its feedback input from the FB pin. At adjustable output voltages, a resistive voltage divider must be connected to that pin. At fixed output voltages, FB must be connected to the output voltage to directly sense the voltage. Fixed output voltage versions use a trimmed internal resistive divider. The feedback voltage will be compared with the internal reference voltage to generate a stable and accurate output voltage.

The device uses 4 internal N-channel MOSFETs to maintain synchronous power conversion at all possible operating conditions. This enables the device to keep high efficiency over a wide input voltage and output power range. To avoid ground shift problems due to the high currents in the switches, two separate ground pins GND and PGND are used. The reference for all control functions is the GND pin. The power switches are connected to PGND. Both grounds must be connected on the PCB at only one point, ideally, close to the GND pin. Due to the 4-switch topology, the load is always disconnected from the input during shutdown of the converter. To protect the device from overheating an internal temperature sensor is implemented.

### 9.2 Functional Block Diagram

## 9.3 Feature Description

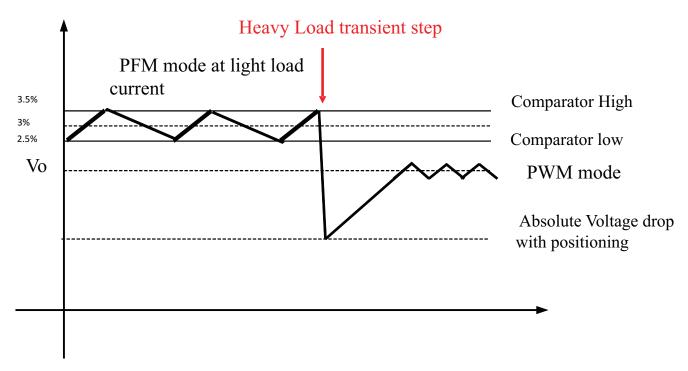

### 9.3.1 Dynamic Voltage Positioning

As detailed in Figure 3, the output voltage is typically 3% above the nominal output voltage at light load currents, as the device is in power save mode. This gives additional headroom for the voltage drop during a load transient from light load to full load. This allows the converter to operate with a small output capacitor and still have a low absolute voltage drop during heavy load transient changes. See Figure 3 for detailed operation of the power save mode.

Product Folder Links: TPS63020-Q1

Submit Documentation Feedback

### **Feature Description (continued)**

#### 9.3.2 Dynamic Current Limit

To protect the device and the application, the average inductor current is limited internally on the IC. At nominal operating conditions, this current limit is constant. The current limit value can be found in the electrical characteristics table. If the supply voltage at VIN drops below 2.3 V, the current limit is reduced. This can happen when the input power source becomes weak. Increasing output impedance, when the batteries are almost discharged, or an additional heavy pulse load is connected to the battery can cause the VIN voltage to drop. The dynamic current limit has its lowest value when reaching the minimum recommended supply voltage at VIN. At this voltage, the device is forced into burst mode operation trying to stay active as long as possible even with a weak input power source.

If the die temperature increases above the recommended maximum temperature, the dynamic current limit becomes active. Similar to the behavior when the input voltage at VIN drops, the current limit is reduced with temperature increasing.

#### 9.3.2.1 Device Enable

The device is put into operation when EN is set high. It is put into a shutdown mode when EN is set to GND. In shutdown mode, the regulator stops switching, all internal control circuitry is switched off, and the load is disconnected from the input. This means that the output voltage can drop below the input voltage during shutdown. During start-up of the converter, the duty cycle and the peak current are limited in order to avoid high peak currents flowing from the input.

#### 9.3.2.2 Power Good

The device has a built in power good function to indicate whether the output voltage is regulated properly. As soon as the average inductor current gets limited to a value below the current the voltage regulator demands for maintaining the output voltage the power good output gets low impedance. The output is open drain, so its logic function can be adjusted to any voltage level the connected logic is using, by connecting a pull up resistor to the supply voltage of the logic. By monitoring the status of the current control loop, the power good output provides the earliest indication possible for an output voltage break down and leaves the connected application a maximum time to safely react.

#### 9.3.2.3 Overvoltage Protection

If, for any reason, the output voltage is not fed back properly to the input of the voltage amplifier, control of the output voltage will not work anymore. Therefore overvoltage protection is implemented to avoid the output voltage exceeding critical values for the device and possibly for the system it is supplying. The implemented overvoltage protection circuit monitors the output voltage internally as well. In case it reaches the overvoltage threshold the voltage amplifier regulates the output voltage to this value.

#### 9.3.2.4 Undervoltage Lockout

An undervoltage lockout function prevents device start-up if the supply voltage at VINA is lower than approximately its threshold (see *Electrical Characteristics* table). When in operation, the device automatically enters the shutdown mode if the voltage at VINA drops below the undervoltage lockout threshold. The device automatically restarts if the input voltage recovers to the minimum operating input voltage.

## 9.3.2.5 Overtemperature Protection

The device has a built-in temperature sensor which monitors the internal IC temperature. If the temperature exceeds the programmed threshold (see *Electrical Characteristics* table) the device stops operating. As soon as the IC temperature has decreased below the programmed threshold, it starts operating again. There is a built-in hysteresis to avoid unstable operation at IC temperatures at the overtemperature threshold.

#### 9.4 Device Functional Modes

#### 9.4.1 Softstart and Short Circuit Protection

After being enabled, the device starts operating. The average current limit ramps up from an initial 400 mA following the output voltage increasing. At an output voltage of about 1.2 V, the current limit is at its nominal value. If the output voltage does not increase, the current limit will not increase. There is no timer implemented. Thus, the output voltage overshoot at startup, as well as the inrush current, is kept at a minimum. The device ramps up the output voltage in a controlled manner even if a large capacitor is connected at the output. When the output voltage does not increase above 1.2 V, the device assumes a short circuit at the output, and keeps the current limit low to protect itself and the application. At a short on the output during operation, the current limit also is decreased accordingly.

#### 9.4.2 Buck-Boost Operation

To regulate the output voltage at all possible input voltage conditions, the device automatically switches from step down operation to boost operation and back as required by the configuration. It always uses one active switch, one rectifying switch, one switch permanently on, and one switch permanently off. Therefore, it operates as a step down converter (buck) when the input voltage is higher than the output voltage, and as a boost converter when the input voltage is lower than the output voltage. There is no mode of operation in which all 4 switches are permanently switching. Controlling the switches this way allows the converter to maintain high efficiency at the most important point of operation, when input voltage is close to the output voltage. The RMS current through the switches and the inductor is kept at a minimum, to minimize switching and conduction losses. For the remaining 2 switches, one is kept permanently on and the other is kept permanently off, thus causing no switching losses.

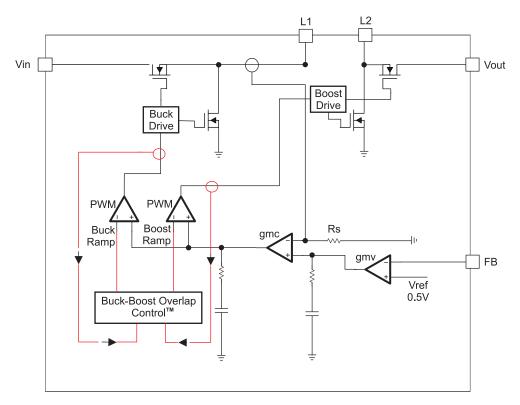

### 9.4.3 Control Loop

The controller circuit of the device is based on an average current mode topology. The average inductor current is regulated by a fast current regulator loop which is controlled by a voltage control loop. Figure 2 shows the control loop.

The non inverting input of the transconductance amplifier, gmv, is assumed to be constant. The output of gmv defines the average inductor current. The inductor current is reconstructed by measuring the current through the high side buck MOSFET. This current corresponds exactly to the inductor current in boost mode. In buck mode the current is measured during the on time of the same MOSFET. During the off time, the current is reconstructed internally starting from the peak value at the end of the on time cycle. The average current and the feedback from the error amplifier gmv forms the correction signal gmc. This correction signal is compared to the buck and the boost sawtooth ramp giving the PWM signal. Depending on which of the two ramps the gmc output crosses either the Buck or the Boost stage is initiated. When the input voltage is close to the output voltage, one buck cycle is always followed by a boost cycle. In this condition, no more than three cycles in a row of the same mode are allowed. This control method in the buck-boost region ensures a robust control and the highest efficiency.

The Buck-Boost Overlap Control<sup>TM</sup> makes sure that the classical buck-boost function, which would cause two switches to be on every half a cycle, is avoided. Thanks to this block whenever all switches becomes active during one clock cycle, the two ramps are shifted away from each other, on the other hand when there is no switching activities because there is a gap between the ramps, the ramps are moved closer together. As a result the number of classical buck-boost cycles or no switching is reduced to a minimum and high efficiency values has been achieved.

### **Device Functional Modes (continued)**

Figure 2. Average Current Mode Control

#### 9.4.4 Power Save Mode and Synchronization

The PS/SYNC pin can be used to select different operation modes. Power save mode is used to improve efficiency at light load. To enable power-save, PS/SYNC must be set low. If PS/SYNC is set low then power save mode is entered when the average inductor current gets lower then about 100 mA. At this point the converter operates with reduced switching frequency and with a minimum quiescent current to maintain high efficiency.

During the power save mode, the output voltage is monitored with a comparator by the threshold comp low and comp high. When the device enters power save mode, the converter stops operating and the output voltage drops. The slope of the output voltage depends on the load and the value of output capacitance. As the output voltage falls below the comp low threshold set to 2.5% typical above  $V_{OUT}$ , the device ramps up the output voltage again, by starting operation using a programmed average inductor current higher than required by the current load condition. Operation can last one or several pulses. The converter continues these pulses until the comp high threshold, set to typically 3.5% above  $V_{OUT}$  nominal, is reached and the average inductance current gets lower than about 100 mA. When the load increases above the minimum forced inductor current of about 100 mA, the device will automatically switch to PWM mode.

The power save mode can be disabled by programming high at the PS/SYNC. Connecting a clock signal at PS/SYNC forces the device to synchronize to the connected clock frequency.

Synchronization is done by a PLL, so synchronizing to lower and higher frequencies compared to the internal clock works without any issues. The PLL can also tolerate missing clock pulses without the converter malfunctioning. The PS/SYNC input supports standard logic thresholds.

Submit Documentation Feedback

# **Device Functional Modes (continued)**

Figure 3. Power Save Mode Thresholds and Dynamic Voltage Positioning

Submit Documentation Feedback

## 10 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 10.1 Application Information

The TPS63020-Q1 is a high efficiency, low quiescent current buck-boost converter suitable for applications where the input voltage is higher or lower than the output voltage. Continuous output current can go as high as 2 A in boost mode and as high as 4 A in buck mode. The maximum average current in the switches is limited to a typical value of 4 A.

## 10.2 Typical Application

Figure 4. Application Circuit

### 10.2.1 Design Requirements

The design guidelines provide a component selection to operate the device within the operating conditions specified on the Application Circuit schematic.

Table 1 shows the list of components for the Application Characteristic Curves.

**Table 1. List of Components**

| REFERENCE | DESCRIPTION                           | MANUFACTURER               |

|-----------|---------------------------------------|----------------------------|

|           | TPS63020-Q1                           | Texas Instruments          |

| L1        | 1.5 µH, 4 mm x 4 mm x 2 mm            | XFL4020-152ML, Coilcraft   |

| C1        | 2 x 10 μF 6.3V, 0603, X5R ceramic     | GRM188R60J106ME84D, Murata |

| C2        | 3 x 22 μF 6.3V, 0603, X5R ceramic     | GRM188R60J226MEAOL Murata  |

| C3        | 0.1 μF, X5R or X7R ceramic            |                            |

| R1        | Depending on the output voltage at TF | PS63020                    |

| R2        | Depending on the output voltage at TF | S63020                     |

| R3        | 1 ΜΩ                                  |                            |

### 10.2.2 Detailed Design Procedure

The TPS63020-Q1 series of buck-boost converter has internal loop compensation. Therefore, the external L-C filter has to be selected to work with the internal compensation. As a general rule of thumb, the product L x C should not move over a wide range when selecting a different output filter. However, when selecting the output filter a low limit for the inductor value exists to avoid subharmonic oscillation which could be caused by a far too fast ramp up of the amplified inductor current. For the TPS63020-Q1 series the minimum inductor value should be kept at 1 uH.

In particular either 1  $\mu$ H or 1.5  $\mu$ H is recommended working at output current between 1.5 A and 2 A. If operating with lower load current is also possible to use 2.2  $\mu$ H.

Selecting a larger output capacitor value is less critical because the corner frequency moves to lower frequencies.

#### 10.2.2.1 Inductor Selection

For high efficiencies, the inductor should have a low dc resistance to minimize conduction losses. Especially at high-switching frequencies, the core material has a high impact on efficiency. When using small chip inductors, the efficiency is reduced mainly due to higher inductor core losses. This needs to be considered when selecting the appropriate inductor. The inductor value determines the inductor ripple current. The larger the inductor value, the smaller the inductor ripple current and the lower the conduction losses of the converter. Conversely, larger inductor values cause a slower load transient response. To avoid saturation of the inductor, the peak current for the inductor in steady state operation is calculated using Equation 6. Only the equation which defines the switch current in boost mode is shown, because this provides the highest value of current and represents the critical current value for selecting the right inductor.

Duty Cycle Boost

$$D = \frac{V_{OUT} - V_{IN}}{V_{OUT}}$$

$$I_{PEAK} = \frac{Iout}{\eta \times (1 - D)} + \frac{Vin \times D}{2 \times f \times L}$$

(1)

where

- D =Duty Cycle in Boost mode

- f = Converter switching frequency (typical 2.5MHz)

- L = Inductor value

- η = Estimated converter efficiency (use the number from the efficiency curves or 0.90 as an assumption)

- Note: The calculation must be done for the minimum input voltage possible in boost mode

Calculating the maximum inductor current using the actual operating conditions gives the minimum saturation current of the inductor needed. It's recommended to choose an inductor with a saturation current 20% higher than the value calculated using Equation 2. Possible inductors are listed in Table 2.

Table 2. Inductor Selection(1)

| VENDOR    | INDUCTOR SERIES |

|-----------|-----------------|

| Coilcraft | XFL4020         |

| Toko      | FDV0530S        |

(1) See Third-party Products Disclaimer

## 10.2.2.2 Capacitor Selection

## 10.2.2.2.1 Input Capacitor

At least a 10  $\mu$ F input capacitor is recommended to improve transient behavior of the regulator and EMI behavior of the total power supply circuit. A ceramic capacitor placed as close as possible to the VIN and PGND pins of the IC is recommended.

Product Folder Links: TPS63020-Q1

(2)

#### 10.2.2.2.2 Output Capacitor

For the output capacitor, use of a small ceramic capacitors placed as close as possible to the VOUT and PGND pins of the IC is recommended. If, for any reason, the application requires the use of large capacitors which can not be placed close to the IC, use a smaller ceramic capacitor in parallel to the large capacitor. The small capacitor should be placed as close as possible to the VOUT and PGND pins of the IC. The recommended typical output capacitor value is  $30~\mu\text{F}$  with a variance that depends on the specific application requirements.

There is also no upper limit for the output capacitance value. Larger capacitors will cause lower output voltage ripple as well as lower output voltage drop during load transients.

When choosing input and output capacitors, it needs to be kept in mind, that the value of capacitance experiences significant losses from their rated value depending on the operating temperature and the operating DC voltage. It is not uncommon for a small surface mount ceramic capacitor to lose 50% and more of its rated capacitance. For this reason it could be important to use a larger value of capacitance or a capacitor with higher voltage rating in order to ensure the required capacitance at the full operating voltage.

#### 10.2.2.2.3 Bypass Capacitor

To make sure that the internal control circuits are supplied with a stable low noise supply voltage, a capacitor can be connected between VINA and GND. Using a ceramic capacitor with a value of 0.1  $\mu$ F is recommended. The value of this capacitor should not be higher than 0.22  $\mu$ F.

### 10.2.2.3 Setting the Output Voltage

The feedback resistor divider must be connected between VOUT, FB and GND. When the output voltage is regulated, the typical value of the voltage at the FB pin is 500 mV. The maximum recommended value for the output voltage is 8 V. The current through the resistive divider should be about 100 times greater than the current into the FB pin. The typical current into the FB pin is 0.01  $\mu$ A, and the voltage across the resistor between FB and GND, R<sub>2</sub>, is typically 500 mV. Based on these two values, the recommended value for R2 should be lower than 500 k $\Omega$ , in order to set the divider current at 1  $\mu$ A or higher. It is recommended to keep the value for this resistor in the range of 200 k $\Omega$ . From that, the value of the resistor connected between VOUT and FB, R<sub>1</sub>, depending on the needed output voltage (V<sub>OUT</sub>), can be calculated using Equation 3:

$$R1 = R2 \times \left(\frac{V_{OUT}}{V_{FB}} - 1\right)$$

(3)

### 10.2.3 Application Curves

Submit Documentation Feedback

Copyright © 2015–2016, Texas Instruments Incorporated

## 10.3 System Examples

## 10.3.1 2-A Load Current

Figure 18. Application Circuit for 2-A Load Current

Capacitor C4 and resistor R1 are added for improved load transient performance.

## 11 Power Supply Recommendations

The TPS63020-Q1 device has no special requirements for its input power supply.

The output current of the power supply must be rated according to the supply voltage, output voltage and output current of the TPS63020-Q1.

## 12 Layout

## 12.1 Layout Guidelines

For all switching power supplies, the layout is an important step in the design, especially at high peak currents and high switching frequencies. If the layout is not carefully done, the regulator could show stability problems as well as EMI problems. Therefore, use wide and short traces for the main current path and for the power ground tracks. The input capacitor, output capacitor, and the inductor should be placed as close as possible to the IC. Use a common ground node for power ground and a different one for control ground to minimize the effects of ground noise. Connect these ground nodes at any place close to one of the ground pins of the IC.

The feedback divider should be placed as close as possible to the control ground pin of the IC. To lay out the control ground, short traces are recommended as well, separation from the power ground traces. This avoids ground shift problems, which can occur due to superimposition of power ground current and control ground current.

## 12.2 Layout Example

Figure 19. PCB Layout Suggestion

Submit Documentation Feedback

#### 12.3 Thermal Considerations

Implementation of integrated circuits in low-profile and fine-pitch surface-mount packages typically requires special attention to power dissipation. Many system-dependent issues such as thermal coupling, airflow, added heat sinks and convection surfaces, and the presence of other heat-generating components affect the power-dissipation limits of a given component.

Three basic approaches for enhancing thermal performance are listed below:

- Improving the power dissipation capability of the PCB design

- · Improving the thermal coupling of the component to the PCB by soldering the exposed thermal pad

- · Introducing airflow in the system

For more details on how to use the thermal parameters, see the application notes: *Thermal Characteristics Application Note* (SZZA017), and *Semiconductor and IC Package Thermal Metrics Application Note* (SPRA953).

## 13 Device and Documentation Support

### 13.1 Device Support

### 13.1.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

### 13.2 Documentation Support

### 13.2.1 Related Documentation

For related documentation see the following:

- Thermal Characteristics Application Note, (SZZA017)

- IC Package Thermal Metrics Application Note, (SPRA953)

### 13.3 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community TI's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 13.4 Trademarks

PowerPAD, E2E are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

#### 13.5 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### 13.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

# 14 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

## PACKAGE OPTION ADDENDUM

10-Dec-2020

#### **PACKAGING INFORMATION**

www.ti.com

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| TPS63020QDSJRQ1  | ACTIVE | VSON         | DSJ                | 14   | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | 63020Q                  | Samples |

| TPS63020QDSJTQ1  | ACTIVE | VSON         | DSJ                | 14   | 250            | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | 63020Q                  | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE OPTION ADDENDUM**

10-Dec-2020

#### OTHER QUALIFIED VERSIONS OF TPS63020-Q1:

● Catalog: TPS63020

www.ti.com

NOTE: Qualified Version Definitions:

• Catalog - TI's standard catalog product

PACKAGE MATERIALS INFORMATION

www.ti.com 9-Feb-2016

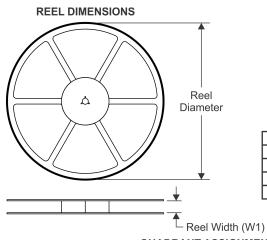

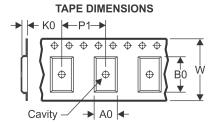

## TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

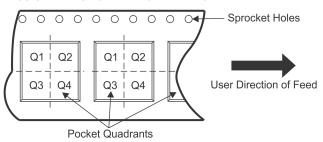

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| 7 til dillionolollo alo nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|---------------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                          | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| TPS63020QDSJRQ1                 | VSON            | DSJ                | 14 | 3000 | 330.0                    | 12.4                     | 3.3        | 4.3        | 1.1        | 8.0        | 12.0      | Q1               |

| TPS63020QDSJTQ1                 | VSON            | DSJ                | 14 | 250  | 180.0                    | 12.4                     | 3.3        | 4.3        | 1.1        | 8.0        | 12.0      | Q1               |

www.ti.com 9-Feb-2016

#### \*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| TPS63020QDSJRQ1 | VSON         | DSJ             | 14   | 3000 | 367.0       | 367.0      | 35.0        |  |

| TPS63020QDSJTQ1 | VSON         | DSJ             | 14   | 250  | 210.0       | 185.0      | 35.0        |  |

4208212-3/C 06/11

DSJ (R-PVSON-N14) PLASTIC SMALL OUTLINE NO-LEAD В PIN 1 INDEX AREA TOP AND BOTTOM 1,00 0,80 -0,20 REF. SEATING PLANE 0,08 0,05 0,00 C 14X  $\frac{0,50}{0,30}$ THERMAL PAD SIZE AND SHAPE SHOWN ON SEPARATE SHEET 14 ♦ 0,10 M C A B 3,00

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M—1994.

- B. This drawing is subject to change without notice.

- C. Quad Flatpack, No-Leads (QFN) package configuration.

- D. The package thermal pad must be soldered to the board for thermal and mechanical performance.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

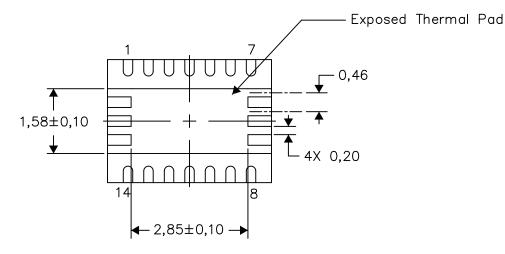

# DSJ (R-PVSON-N14)

PLASTIC SMALL OUTLINE NO-LEAD

## THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No-Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Bottom View

Exposed Thermal Pad Dimensions

4208549-3/G 04/15

NOTE: All linear dimensions are in millimeters

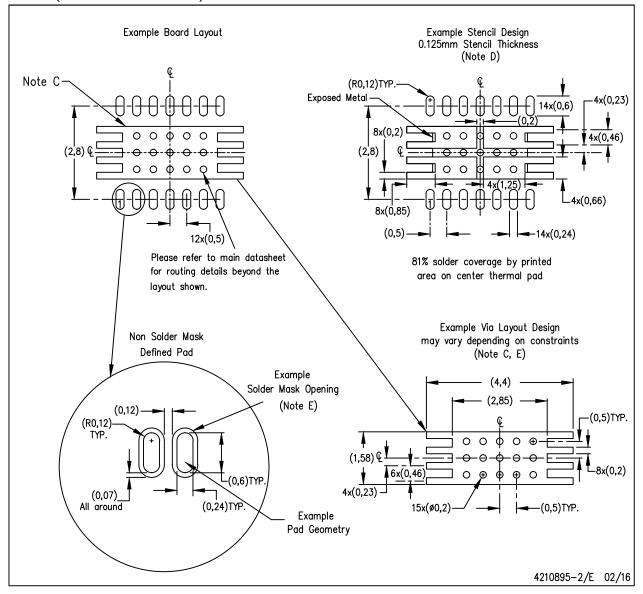

# DSJ (R-PVSON-N14)

# PLASTIC SMALL OUTLINE NO-LEAD

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, Quad Flat—Pack Packages, Texas Instruments Literature No. SCBA017, SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- E. Customers should contact their board fabrication site for minimum solder mask web tolerances between signal pads.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

Tl's products are provided subject to Tl's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such Tl products. Tl's provision of these resources does not expand or otherwise alter Tl's applicable warranties or warranty disclaimers for Tl products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated