LM2623-Q1

SNVSAO5-OCTOBER 2017

## LM2623-Q1 Automotive Gated-Oscillator-Based DC-DC Boost Converter

#### 1 Features

- AEC-Q100 Qualified for Automotive Applications:

- Device Temperature Grade 1: –40°C to 125°C

Ambient Operating Temperature

- Device HBM ESD Classification Level 2

- Device CDM ESD Classification Level C4A

- Good Efficiency Over a Very Wide Load Range

- Very Low Output Voltage Ripple

- Up to 2-MHz Switching Frequency

- 0.9-V to 14-V Operating Voltage

- 1.1-V Start-Up Voltage

- 1.24-V to 14-V Adjustable Output Voltage

- 0.17-Ω Internal MOSFET

- Up to 90% Regulator Efficiency

- 80-µA Typical Operating Current (Into V<sub>DD</sub> Pin of Supply)

- Low Shutdown Current ( $I_Q < 2.5 \mu A$ )

- 4-mm x 4-mm Thermally Enhanced WSON Package Option

## 2 Applications

- Automotive Camera

- Automotive Radar

- Automotive GPS

- Flash Memory Programming

- White-LED Drive

## 3 Description

The LM2623-Q1 is a high-efficiency, general-purpose, step-up DC-DC switching regulator for automotive systems. The device accepts an input voltage between 0.9 V and 14 V and converts it into a regulated output voltage between 1.24 V and 14 V.

In order to adapt to a number of applications, the LM2623-Q1 allows the designer to program the output voltage, the operating frequency (300 kHz to 2 MHz), and duty cycle (17% to 90%) to optimize performance. The selected values can be fixed or can vary with input voltage or input-to-output voltage ratio. The LM2623-Q1 uses a very simple, on/off regulation mode to produce good efficiency and stable operation over a wide operating range. The device normally regulates by skipping switching cycles when it reaches the regulation limit (pulse frequency modulation (PFM)).

Refer to *Non-Linear Effect* and *Choosing the Correct* C3 Capacitor to resolve any design challenges before board design is finalized.

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| LM2623-Q1   | WSON (14) | 4.00 mm × 4.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

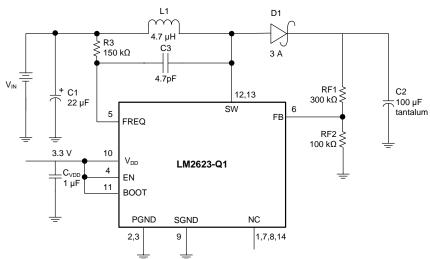

## **Typical Application**

Copyright © 2017, Texas Instruments Incorporated

## **Table of Contents**

| 1 | Features 1                             | 8 Applications and Implementation 11                    |

|---|----------------------------------------|---------------------------------------------------------|

| 2 | Applications 1                         | 8.1 Application Information 11                          |

| 3 | Description 1                          | 8.2 Typical Application 11                              |

| 4 | Revision History2                      | 9 Power Supply Recommendations 13                       |

| 5 | Pin Configuration and Functions 3      | 10 Layout 14                                            |

| 6 | Specifications4                        | 10.1 Layout Guidelines 14                               |

| • | 6.1 Absolute Maximum Ratings           | 10.2 Layout Example 15                                  |

|   | 6.2 ESD Ratings                        | 10.3 WSON Package Devices 15                            |

|   | 6.3 Recommended Operating Conditions 4 | 11 Device And Documentation Support 16                  |

|   | 6.4 Thermal Information                | 11.1 Device Support                                     |

|   | 6.5 Electrical Characteristics5        | 11.2 Documentation Support                              |

|   | 6.6 Typical Characteristics            | 11.3 Receiving Notification of Documentation Updates 16 |

| 7 | Detailed Description 8                 | 11.4 Community Resources 16                             |

| - | 7.1 Overview 8                         | 11.5 Trademarks 16                                      |

|   | 7.2 Functional Block Diagram           | 11.6 Electrostatic Discharge Caution                    |

|   | 7.3 Feature Description                | 11.7 Glossary 16                                        |

|   | 7.4 Device Functional Modes            | 12 Mechanical, Packaging, And Orderable Information     |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| DATE         | REVISION | NOTES           |

|--------------|----------|-----------------|

| October 2017 | *        | Initial release |

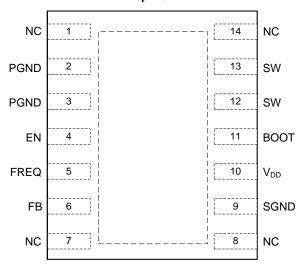

## **5 Pin Configuration and Functions**

### NHL Package 14-Pin WSON Top View

## **Pin Functions**

|        | PIN             | TYPE    | DESCRIPTION                                                                                                                      |  |  |  |  |

|--------|-----------------|---------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NO.    | NAME            | ITPE    | DESCRIPTION                                                                                                                      |  |  |  |  |

| 1      | NC              | _       | No connect                                                                                                                       |  |  |  |  |

| 2, 3   | PGND            | GND     | Power ground (pins 2 and 3 must be shorted together)                                                                             |  |  |  |  |

| 4      | EN              | Digital | Active-low shutdown input                                                                                                        |  |  |  |  |

| 5      | FREQ            | Analog  | Frequency adjust; connect an external resistor between this pin and a voltage sou sets the switching frequency of the LM2623-Q1. |  |  |  |  |

| 6      | FB              | Analog  | Output voltage feedback                                                                                                          |  |  |  |  |

| 7      | NC              | _       | No connect                                                                                                                       |  |  |  |  |

| 8      | NC              | _       | No connect                                                                                                                       |  |  |  |  |

| 9      | SGND            | GND     | Signal ground                                                                                                                    |  |  |  |  |

| 10     | V <sub>DD</sub> | Power   | Power supply for internal circuitry                                                                                              |  |  |  |  |

| 11     | BOOT            | Analog  | Bootstrap supply for the gate drive of internal MOSFET power switch                                                              |  |  |  |  |

| 12, 13 | SW              | Analog  | Drain of the internal MOSFET power switch (pins 12 and 13 <i>must</i> be shorted together)                                       |  |  |  |  |

| 14     | NC              | _       | No connect                                                                                                                       |  |  |  |  |

| DAP    | DAP             | Thermal | Solder to board for enhanced thermal dissipation; must be electrically isolated/floating.                                        |  |  |  |  |

Copyright © 2017, Texas Instruments Incorporated

## 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1) (2)

|                        |                                           | MIN  | MAX  | UNIT |

|------------------------|-------------------------------------------|------|------|------|

|                        | SW pin voltage                            | -0.5 | 14.5 | V    |

| Input pins             | BOOT, VDD, EN, and FB pins                | -0.5 | 10   | V    |

|                        | FREQ pin                                  |      | 100  | μA   |

| Power dissipation      | on (T <sub>A</sub> = 25°C) <sup>(3)</sup> |      | 500  | mW   |

| T <sub>J_MAX</sub> (3) |                                           |      | 150  | °C   |

| Storage temper         | ature, T <sub>stg</sub>                   | -55  | 150  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                   |                           | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------------|---------------------------|-------|------|

|                    |                         | Human body model (HBM), per       | All pins except 12 and 13 | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | AEC Q100-002 <sup>(1)</sup>       | Pins 12 and 13            | ±1000 | V    |

|                    |                         | Charged device model (CDM), per A | AEC Q100-011              | ±500  |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|              |                                           | MIN | NOM MAX  | UNIT |

|--------------|-------------------------------------------|-----|----------|------|

|              | V <sub>DD</sub> pin                       | 3   | 5        | V    |

| Input pins   | FB and EN pins                            | 0   | $V_{DD}$ | V    |

|              | BOOT pin                                  | 0   | 10       | V    |

| Operating ju | unction temperature range, T <sub>J</sub> | -40 | 125      | °C   |

#### 6.4 Thermal Information

|                      |                                              | LM2623-Q1  |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | NHL (WSON) | UNIT |

|                      |                                              | 14 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 37.6       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 26.9       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 15.0       | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.3        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 4.7        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Product Folder Links: LM2623-Q1

<sup>(2)</sup> If Military/Aerospace specified devices are required, contact the Texas Instruments Sales Office / Distributors for availability and specifications.

<sup>(3)</sup> The maximum power dissipation must be derated at elevated temparters and is dictated by T<sub>J-MAX</sub> (maximum junction temperature), R<sub>Θ,JA</sub> (junction to ambient thermal resistance), and T<sub>A</sub> (ambient temperature). The maximum allowable power dissipation at any temperature is P<sub>D-MAX</sub> = (T<sub>J-MAX</sub> - T<sub>A</sub>)/R<sub>Θ,JA</sub> or the number given in the Absolute Maximum Rating, whichever is lower.

## 6.5 Electrical Characteristics

Limits apply for  $T_J = 25^{\circ}C$  and  $V_{DD} = V_{OUT} = 3.3 \text{ V}$ , unless otherwise specified

|                     | PARAMETER                                       | TEST CONDITIONS                                                                | MIN                 | TYP  | MAX                  | UNIT |  |  |

|---------------------|-------------------------------------------------|--------------------------------------------------------------------------------|---------------------|------|----------------------|------|--|--|

| GENERA              | L                                               |                                                                                |                     |      |                      |      |  |  |

| V <sub>DD_ST</sub>  | Start-up supply voltage 25°C                    | $I_{LOAD} = 0 \text{ mA}^{(1)}$                                                |                     |      | 1.1                  | V    |  |  |

| V <sub>IN_OP</sub>  | Minimum operating supply voltage (once started) | I <sub>LOAD</sub> = 0 mA                                                       |                     | 0.65 | 0.9                  | V    |  |  |

|                     |                                                 |                                                                                |                     | 1.24 |                      |      |  |  |

| $V_{FB}$            | FB pin voltage                                  | -40°C to 85°C                                                                  | 1.2028              |      | 1.2772               | V    |  |  |

|                     |                                                 | -40°C to 125°C                                                                 | 1.2028              |      | 1.2772               |      |  |  |

| V <sub>OUT_MA</sub> | Maximum output voltage                          |                                                                                |                     | 14   |                      | V    |  |  |

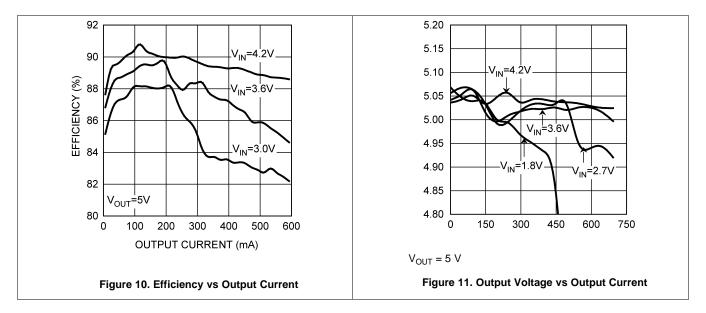

|                     |                                                 | V <sub>IN</sub> = 3.6 V; V <sub>OUT</sub> = 5 V, I <sub>LOAD</sub> = 500 mA    |                     | 87%  |                      |      |  |  |

| η                   | Efficiency                                      | $V_{IN} = 2.5 \text{ V; } V_{OUT} = 3.3 \text{ V, } I_{LOAD} = 200 \text{ mA}$ |                     | 87%  |                      |      |  |  |

| D                   | Switch duty cycle                               |                                                                                |                     | 17%  |                      |      |  |  |

|                     |                                                 | FB pin > 1.3 V, EN pin at V <sub>DD</sub>                                      |                     | 80   |                      |      |  |  |

| I <sub>DD</sub>     | Operating quiescent current <sup>(2)</sup>      | FB pin > 1.3 V, EN pin at $V_{DD}$ , $-40^{\circ}C$ to 85°C                    |                     |      | 110                  | μA   |  |  |

|                     |                                                 | FB pin > 1.3 V, EN pin at V <sub>DD</sub> , -40°C to 125°C                     |                     |      | 110                  |      |  |  |

|                     | Shutdown quiescent current <sup>(3)</sup>       | V <sub>DD</sub> , BOOT, and SW pins at 5 V, EN pin < 200 mV                    |                     | 0.01 |                      |      |  |  |

| I <sub>SD</sub>     |                                                 | V <sub>DD</sub> , BOOT, and SW pins at 5 V, EN pin < 200 mV, -40°C to 85°C     |                     |      | 2.5                  | μΑ   |  |  |

|                     |                                                 | V <sub>DD</sub> , BOOT, and SW pins at 5 V, EN pin < 200 mV, -40°C to 125°C    |                     |      | 2.5                  | †    |  |  |

| I <sub>CL</sub>     | Switch peak current limit                       |                                                                                | 2.2                 | 2.85 |                      | Α    |  |  |

|                     |                                                 |                                                                                |                     | 0.17 |                      |      |  |  |

| R <sub>DSON</sub>   | MOSFET switch on resistance                     | -40°C to 85°C                                                                  |                     |      | 0.26                 | Ω    |  |  |

|                     |                                                 | -40°C to 125°                                                                  |                     |      | 0.26                 |      |  |  |

| ENABLE              | SECTION                                         |                                                                                |                     |      |                      |      |  |  |

| V                   | EN pin voltage low <sup>(4)</sup>               | -40°C to 85°C                                                                  |                     |      | 0.15 V <sub>DD</sub> | V    |  |  |

| V <sub>EN_LO</sub>  | Liv pili voltage low ·                          | -40°C to 125°C                                                                 |                     |      | 0.15 V <sub>DD</sub> | ٧    |  |  |

| V                   | EN pin voltage high <sup>(4)</sup>              | -40°C to 85°C                                                                  | 0.7 V <sub>DD</sub> |      |                      | V    |  |  |

| V <sub>EN_HI</sub>  | EN PIT VOILAGE HIGH                             | -40°C to 125°C                                                                 | 0.7 V <sub>DD</sub> |      |                      |      |  |  |

V<sub>DD</sub> tied to BOOT and EN pins. Frequency pin tied to V<sub>DD</sub> through 121-KΩ resistor. V<sub>DD\_ST</sub> = V<sub>DD</sub> when start-up occurs. V<sub>IN</sub> is V<sub>DD</sub> + D1 voltage (usually 10 mV to 50 mV at start-up).

This is the current into the V<sub>DD</sub> pin.

This is the total current into pins V<sub>DD</sub>, BOOT, SW, and FREQ.

When the EN pin is below V<sub>EN\_LO</sub>, the regulator is shut down; when it is above V<sub>EN\_HI</sub>, the regulator is operating.

Copyright © 2017, Texas Instruments Incorporated

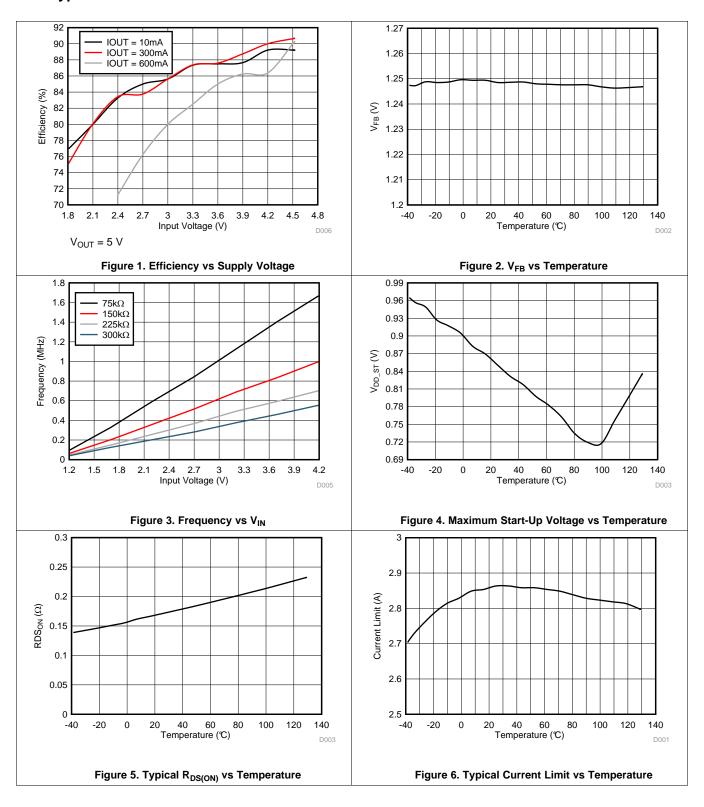

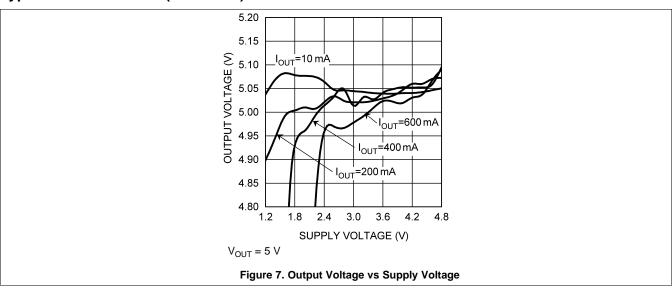

## 6.6 Typical Characteristics

## **Typical Characteristics (continued)**

# TEXAS INSTRUMENTS

## 7 Detailed Description

#### 7.1 Overview

The LM2623-Q1 device is designed to provide step-up DC-DC voltage regulation in battery-powered and low-input voltage systems. The device combines a step-up switching regulator, N-channel power MOSFET, built-in current limit, thermal limit, and voltage reference in a single 14-pin WSON package (see *Functional Block Diagram*). The switching DC-DC regulator boosts an input voltage between 0.9 V and 14 V to a regulated output voltage between 1.24 V and 14 V. The LM2623-Q1 starts from a low 1.1-V input and remains operational down to below 0.9 V. A high-efficiency gated-oscillator topology offers an output of up to 2 A at low step-up ratios.

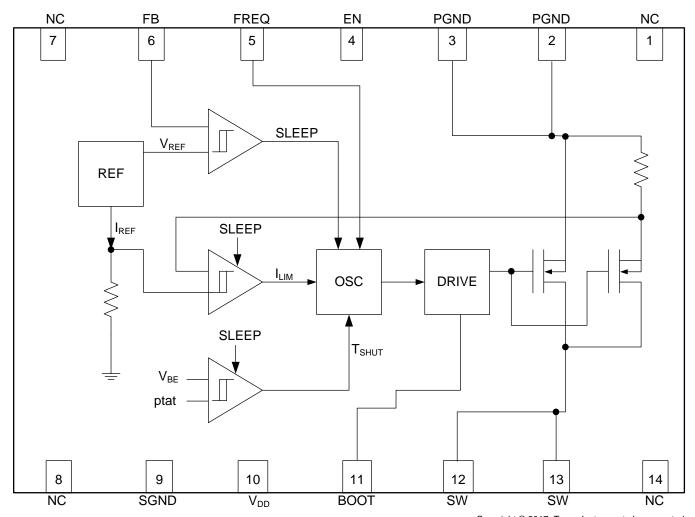

## 7.2 Functional Block Diagram

Copyright © 2017, Texas Instruments Incorporated

### 7.3 Feature Description

#### 7.3.1 Gated Oscillator Control Scheme

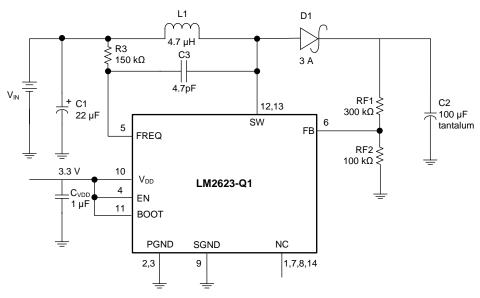

The on/off regulation mode of the LM2623-Q1, along with its ultra-low quiescent current, results in good efficiency over a very wide load range. The internal oscillator frequency can be programmed using an external resistor to be constant or vary with the battery voltage. Adding a capacitor to program the frequency allows the designer to adjust the duty cycle and optimize it for the application. Adding a resistor in addition to the capacitor allows the duty cycle to dynamically compensate for changes to the input/output voltage ratio. This is called a ratio-adaptive gated-oscillator circuit. See the Typical Application for a sample application circuit. Using the correct RC components to adjust the oscillator allows the device to run with low ripple and high efficiency over a wide range of loads and input/output voltages.

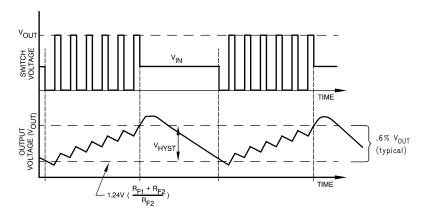

Figure 8. Typical Step-Up Regulator Waveforms

#### 7.3.2 Cycle-To-Cycle PFM

When the load does not vary over a wide range, ratio adaptive circuit techniques can be used to achieve cycle to cycle PFM regulation and lower ripple (or smaller output capacitors). The key to success is matching the duty cycle of the circuit closely to what is required by the input-to-output voltage ratio. This ratio then must be dynamically adjusted for input voltage changes (usually caused by batteries running down). The chosen ratio must allow most of the energy in each switching cycle to be delivered to the load and only a small amount to be stored. When the regulation limit is reached, the overshoot is small, and the system settles at an equilibrium point where it adjusts the off time in each switching cycle to meet the current requirements of the load. The off-time adjustment is done by exceeding the regulation limit during each switching cycle and waiting until the voltage drops below the limit again to start the next switching cycle. The current in the coil never goes to zero like it frequently does in the hysteretic operating mode of circuits with wide load variations or duty cycles that are not matched to the input/output voltage ratio. Optimizing the duty cycle for a given set of input/output voltages conditions can be done by referencing the circuit values in AN-1221 LM2623 General Purpose, Boost Converter Circuit.

#### 7.3.3 Shutdown

The LM2623-Q1 features a shutdown mode that reduces the quiescent current to less than an ensured 2.5  $\mu$ A over temperature. This extends the life of the battery in battery-powered applications. During shutdown, all feedback and control circuitry is turned off. The output voltage of the regulator drops to one diode drop below the input voltage. Entry into the shutdown mode is controlled by the active-low logic input pin EN (pin 4). When the logic input to this pin is pulled below 0.15  $V_{DD}$ , the device goes into shutdown mode. The logic input to this pin must be above 0.7  $V_{DD}$  for the device to work in normal step-up mode. If EN is pulled above 0.7  $V_{DD}$  the SW pin switches continuously for experimentally tested 5  $\mu$ s period, regardless of the output voltage. Once this time period is expired the feedback and gated oscillator scheme take over to regulate the output voltage.

Copyright © 2017, Texas Instruments Incorporated

# TEXAS INSTRUMENTS

#### **Feature Description (continued)**

#### 7.3.4 Internal Current Limit and Thermal Protection

An internal cycle-by-cycle current limit serves as a protection feature. This is set high enough (2.85 A typical, approximately 4 A maximum) so it does not come into effect during normal operating conditions. An internal thermal protection circuit disables the MOSFET power switch when the junction temperature (T<sub>J</sub>) exceeds about 160°C. The switch is re-enabled when T<sub>I</sub> drops below approximately 135°C.

#### 7.4 Device Functional Modes

#### 7.4.1 Pulse Frequency Modulation (PFM)

Pulse frequency modulation is typically accomplished by switching continuously until the voltage limit is reached and skipping cycles after that to just maintain it. This results in a somewhat hysteretic mode of operation. The coil stores more energy each cycle as the current ramps up to high levels. When the voltage limit is reached, the system usually overshoots to a higher voltage than required, due to the stored energy in the coil (see Figure 8). The system also undershoots somewhat when it starts switching again because it has depleted all the stored energy in the coil and must store more energy to reach equilibrium with the load. Larger output capacitors and smaller inductors reduce the ripple in these situations. The frequency being filtered, however, is not the basic switching frequency. It is a lower frequency determined by the load, the input/output voltage and the circuit parameters. This mode of operation is useful in situations where the load variation is significant. Power-managed computer systems, for instance, may vary from zero to full load while the system is on, and this is usually the preferred regulation mode for such systems.

#### 7.4.2 Low Voltage Start-Up

The LM2623-Q1 can start up from voltages as low as 1.1 V. On start-up, the control circuitry switches the N-channel MOSFET continuously until the output reaches 3 V. After this output voltage is reached, the normal step-up regulator feedback and gated oscillator control scheme take over. Once the device is in regulation, it can operate down to 0.9 V input, because the internal power for the device can be boot-strapped from the output using the  $V_{DD}$  pin.

0

Product Folder Links: LM2623-Q1

## 8 Applications and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

The LM2623-Q1 is suitable for automotive applications, and supports shutdown mode for low quiescent current when EN input is low. Output voltage level can be adjusted by changing feedback resistor divider values from 1.24-V to 14-V range. The maximum switching frequency is 2MHz.

## 8.2 Typical Application

Copyright © 2017, Texas Instruments Incorporated

Figure 9. LM2623-Q1 Typical Application

### 8.2.1 Design Requirements

The LM2623-Q1 allows the designer to vary output voltage, operating frequency and duty cycle to optimize device performance (see *Detailed Design Procedure* for details).

For typical boost-converter applications, use the parameters listed in Table 1.

**Table 1. Design Parameters**

| DESIGN PARAMETER | EXAMPLE VALUE               |

|------------------|-----------------------------|

| Input voltage    | 0.9 V to 14 V               |

| Output voltage   | 1.24 V to 14 V (adjustable) |

| Output current   | 2 A (maximum)               |

Product Folder Links: LM2623-Q1

#### 8.2.2 Detailed Design Procedure

#### 8.2.2.1 Non-Linear Effect

The LM2623-Q1 takes advantage of a non-linear effect, allowing for the duty cycle to be programmable. C3 in Figure 9 allows for the duty cycle to be programable.

#### 8.2.2.2 Choosing the Correct C3 Capacitor

The duty cycle of the internal oscillator is programmable with the C3 capacitor. Choosing the correct C3 capacitor to obtain the appropriate duty cycle for a particular application circuit is a trial-and-error process. The non-linear effect that C3 produces is dependent on the input voltage and output voltage values. The correct C3 capacitor for specific input and output voltage values cannot be calculated. Choosing the correct C3 capacitance is best done by trial and error, in conjunction with the checking of the inductor peak current to make sure it is not too close to the current limit of the device. As the C3 capacitor value increases, so does the duty cycle; conversely, as the C3 capacitor value decreases, the duty cycle decreases. An incorrect choice of the C3 capacitor can result in the device prematurely tripping the current limit and/or double pulsing, which could lead to the output voltage not being stable. Optimizing the duty cycle for a given set of input/output voltages conditions can be done by referencing the component values in *AN-1221 LM2623 General Purpose*, *Boost Converter Circuit*.

#### 8.2.2.3 Setting the Output Voltage

The output voltage of the step-up regulator can be set by connecting a feedback resistive divider made of  $R_{F1}$  and  $R_{F2}$ . The resistor values are selected as follows:

$$R_{F1} = R_{F2} \times [(V_{OUT} / 1.24) - 1]$$

(1)

A value of 50 k $\Omega$  to 100 k $\Omega$  is suggested for R<sub>F2</sub>. R<sub>F1</sub> can be selected using Equation 1.

## 8.2.2.4 V<sub>DD</sub> Supply

The  $V_{DD}$  supply must be between 3 V to 5 V for the LM2623-Q1 device. This voltage can be bootstrapped from a much lower input voltage by simply connecting the  $V_{DD}$  pin to  $V_{OUT}$ . In the event that the  $V_{DD}$  supply voltage is not a low-ripple voltage source (less than 200 mV), it may be advisable to use an RC filter to clean it up. Excessive ripple on  $V_{DD}$  may reduce the efficiency.

#### 8.2.2.5 Setting the Switching Frequency

The switching frequency of the oscillator is selected by choosing an external resistor (R3) connected between  $V_{IN}$  and the FREQ pin. See Figure 3 in the *Typical Characteristics* for choosing the R3 value to achieve the desired switching frequency. A high switching frequency allows the use of very small surface mount inductors and capacitors and results in a very small solution size. TI recommends a switching frequency between 300 kHz and 2 MHz.

#### 8.2.2.6 Output Diode Selection

Use a Schottky diode for the output diode. The forward current rating of the diode must be higher than the peak input current, and the reverse voltage rating must be higher than the output voltage. Do not use ordinary rectifier diodes, because slow switching speeds and long recovery times cause the efficiency and the load regulation to suffer.

#### 8.2.3 Application Curves

## 9 Power Supply Recommendations

The LM2623-Q1 can start up from voltages as low as 1.1 V. On start-up, the control circuitry switches the N-channel MOSFET continuously until the output reaches 3 V. After this output voltage is reached, the normal step-up regulator feedback and gated oscillator control scheme take over. Once the device is in regulation, it can operate down to below 0.9 V input, because the internal power for the device can be boot-strapped from the output using the  $V_{DD}$  pin.

# TEXAS INSTRUMENTS

## 10 Layout

## 10.1 Layout Guidelines

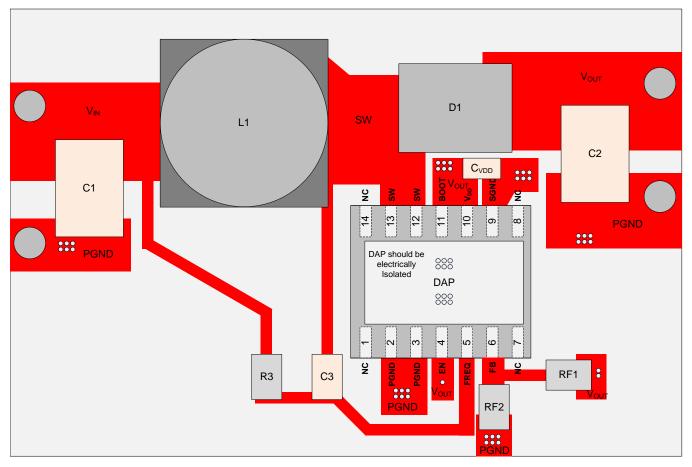

Figure 12 follows proper layout guidelines — use as a guide for laying out the LM2623-Q1 circuit. The LM2623-Q1 inductive boost converter sees a high switched voltage at the SW pin and a step current through the Schottky diode and output capacitor each switching cycle. The high switching voltage can create interference into nearby nodes due to electric field coupling ( $I = C \times dV/dt$ ). The large step current through the diode and the output capacitor can cause a large voltage spike at the SW and BOOST pins due to parasitic inductance in the step current conducting path ( $V = L \times di/dt$ ). Board layout guidelines are geared towards minimizing this electric field coupling and conducted noise.

Boost Output Capacitor Placement, Schottky Diode Placement, and Boost Input / V<sub>DD</sub> Capacitor Placement detail the main (layout sensitive) areas of the LM2623-Q1 inductive boost converter in order of decreasing importance:

#### 10.1.1 Boost Output Capacitor Placement

Because the output capacitor is in the path of the inductor current discharge path, it experiences a high-current step from 0 A to the peak inductor current each time the switch turns off, and the Schottky diode turns on. Any inductance along this series path from the diodes cathode, through  $C_{OUT}$ , and back into the LM2623-Q1 GND pin contributes to voltage spikes at SW. These spikes can potentially overvoltage the SW and BOOST pins, or feed through to GND. To avoid this, COUT+ must be connected as close as possible to the cathode of the Schottky diode, and COUT- must be connected as close as possible to the LM2623-Q1 GND bumps. The best placement for  $C_{OUT}$  is on the same layer as the LM2623-Q1 to avoid any vias that can add excessive series inductance.

#### 10.1.2 Schottky Diode Placement

In the LM2623-Q1 device boost circuit the Schottky diode is in the path of the inductor current discharge. As a result the Schottky diode detects a high-current step from 0 A to the peak inductor current each time the switch turns off, and the diode turns on. Any inductance in series with the diode causes a voltage spike at SW. This can potentially overvoltage the SW pin, or feed through to VOUT and through the output capacitor, into GND. Connecting the anode of the diode as close as possible to the SW pin, and connecting the cathode of the diode as close as possible to C<sub>OUT</sub> reduces the parasitic inductance and minimizes these voltage spikes.

### 10.1.3 Boost Input / V<sub>DD</sub> Capacitor Placement

The LM2623-Q1 input capacitor filters the inductor current ripple and the internal MOSFET driver currents. The inductor current ripple can add input voltage ripple due to any series resistance in the input power path. The MOSFET driver currents can add voltage spikes on the input due to the inductance in series with the VIN/ $V_{DD}$  and the input capacitor. Place the input capacitor close to the inductor and minimize the current-loop area. Close placement of the  $V_{DD}$  capacitor to the  $V_{DD}$  and GND pins is critical because any series inductance can create voltage spikes that could appear on the VIN/ $V_{DD}$  supply line.

## 10.2 Layout Example

Figure 12. LM2623-Q1 Layout Example

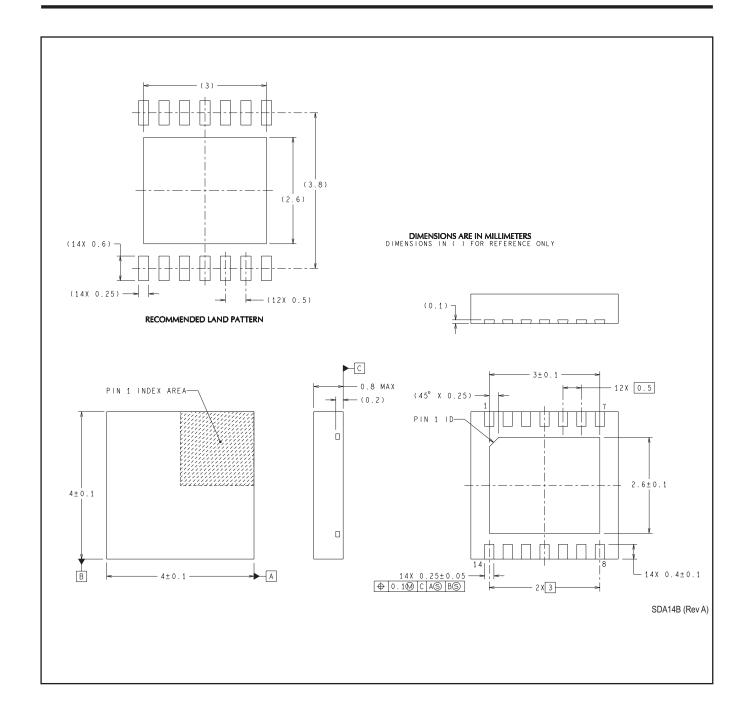

## 10.3 WSON Package Devices

The LM2623-Q1 is offered in the 14-pin WSON surface mount package — for details of the thermal performance as well as mounting and soldering specifications, refer to *Leadless Leadframe Package (LLP)*.

## 11 Device And Documentation Support

#### 11.1 Device Support

## 11.1.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

#### 11.2 Documentation Support

#### 11.2.1 Related Documentation

For related documentation, see the following:

- AN-1187 Leadless Leadframe Package (LLP)

- AN-1221 LM2623 General Purpose, Boost Converter Circuit

- AN-1258 LM2623 Boost Converter A Simple Supply

## 11.3 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

#### 11.4 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community TI's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 11.5 Trademarks

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

## 11.6 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### 11.7 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 12 Mechanical, Packaging, And Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

## PACKAGE OPTION ADDENDUM

10-Dec-2020

#### PACKAGING INFORMATION

www.ti.com

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| LM2623QNHLRQ1    | ACTIVE     | WSON         | NHL                | 14   | 4500           | RoHS & Green | SN                            | Level-2-260C-1 YEAR | -40 to 125   | 2623Q1                  | Samples |

| LM2623QNHLTQ1    | ACTIVE     | WSON         | NHL                | 14   | 250            | RoHS & Green | SN                            | Level-2-260C-1 YEAR | -40 to 125   | 2623Q1                  | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## **PACKAGE OPTION ADDENDUM**

10-Dec-2020

#### OTHER QUALIFIED VERSIONS OF LM2623-Q1:

NOTE: Qualified Version Definitions:

• Catalog - TI's standard catalog product

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

Tl's products are provided subject to Tl's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such Tl products. Tl's provision of these resources does not expand or otherwise alter Tl's applicable warranties or warranty disclaimers for Tl products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated