LMH6601, LMH6601-Q1

SNOSAK9F-JUNE 2006-REVISED JUNE 2015

## LMH6601 and LMH6601-Q1 250-MHz, 2.4-V CMOS Operational Amplifier With Shutdown

#### Features

- LMH6601-Q1 Qualified for Automotive **Applications**

- AEC-Q100 Grade 3

- -40°C to 85°C Ambient Operating Temperature Range

- $V_S = 3.3 \text{ V}, T_A = 25^{\circ}\text{C}, A_V = 2 \text{ V/V}, R_1 = 150 \Omega \text{ to}$ V<sup>-</sup>, Unless Specified

- 125 MHz -3 dB Small Signal Bandwidth

- 75 MHz -3 dB Large Signal Bandwidth

- 30 MHz Large Signal 0.1-dB Gain Flatness

- 260 V/µs Slew Rate

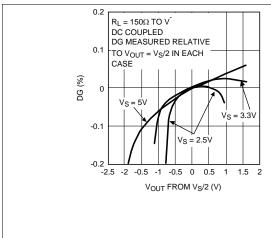

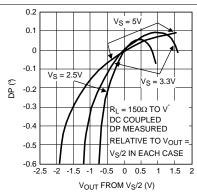

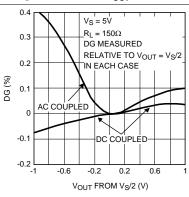

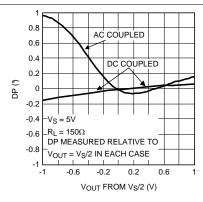

- 0.25%/0.25° Differential Gain and Differential Phase

- Rail-to-Rail Output

- 2.4-V to 5.5-V Single-Supply Operating Range

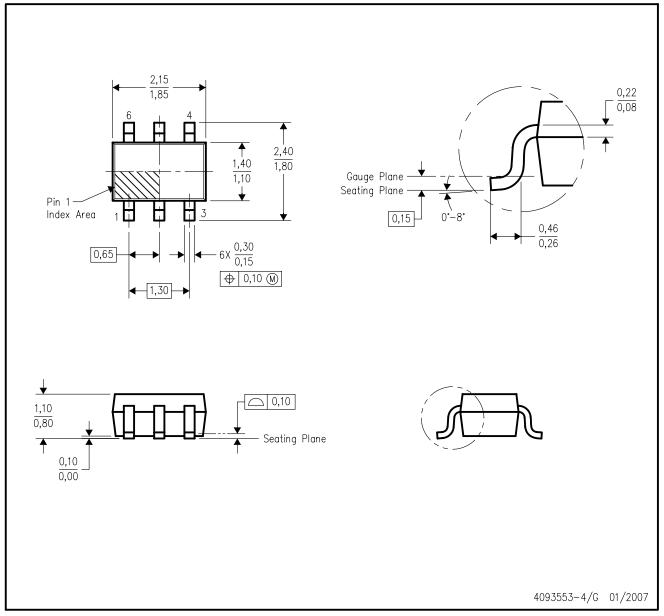

- 6-Pin SC70 Package

## **Applications**

- Video Amplifiers

- Charge Amplifiers

- Set-Top Boxes

- Sample and Holds

- Transimpedance Amplifiers

- Line Drivers

- High-Impedance Buffers

- Automotive

## 3 Description

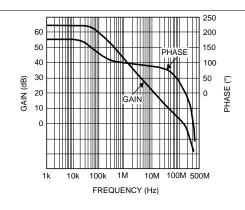

The LMH6601 device is a low-voltage (2.4 V to 5.5 V), high-speed voltage feedback operational amplifier suitable for use in a variety of consumer and industrial applications. With a bandwidth of 125 MHz at a gain of +2 and ensured high-output current of 100 mA, the LMH6601 is an ideal choice for video line driver applications, including HDTV. Low-input bias current (50 pA maximum), rail-to-rail output, and low current noise allow the use of the LMH6601 in industrial applications various transimpedance amplifiers, active filters, or highimpedance buffers. The LMH6601 is an attractive solution for systems which require high performance at low supply voltages. The LMH6601 is available in a 6-pin SC70 package, and includes a micropower shutdown feature.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE  | BODY SIZE (NOM)   |  |  |

|-------------|----------|-------------------|--|--|

| LMH6601     | 0070 (6) | 2.00 mm 1.25 mm   |  |  |

| LMH6601-Q1  | SC70 (6) | 2.00 mm × 1.25 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

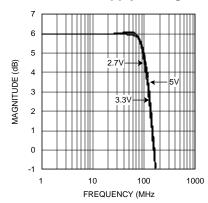

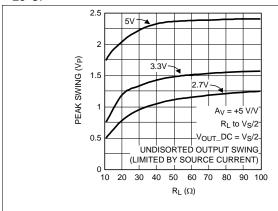

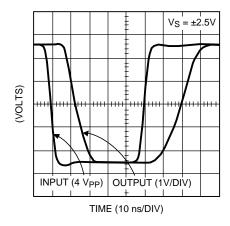

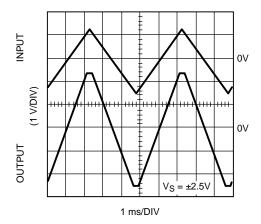

#### Response at a Gain of +2 for Various Supply Voltages

## **Table of Contents**

| 1 | Features 1                            |    | 7.1 Overview                         | 20               |

|---|---------------------------------------|----|--------------------------------------|------------------|

| 2 | Applications 1                        |    | 7.2 Feature Description              | 20               |

| 3 | Description 1                         |    | 7.3 Device Functional Modes          | <mark>2</mark> 1 |

| 4 | Revision History2                     | 8  | Application and Implementation       | 23               |

| 5 | Pin Configuration and Functions3      |    | 8.1 Application Information          | 23               |

| 6 | Specifications                        |    | 8.2 Typical Application              | 29               |

| U | 6.1 Absolute Maximum Ratings          | 9  | Power Supply Recommendations         | 32               |

|   | 6.2 ESD Ratings - for LMH6601         | 10 | Layout                               | 32               |

|   | 6.3 ESD Ratings - for LMH6601-Q1      |    | 10.1 Layout Guidelines               | 32               |

|   | 6.4 Recommended Operating Conditions  |    | 10.2 Layout Examples                 | 32               |

|   | 6.5 Thermal Information               | 11 | Device and Documentation Support     | 33               |

|   | 6.6 Electrical Characteristics, 5 V   |    | 11.1 Documentation Support           | 33               |

|   | 6.7 Electrical Characteristics, 3.3 V |    | 11.2 Related Links                   | 33               |

|   | 6.8 Electrical Characteristics, 2.7 V |    | 11.3 Community Resources             | 33               |

|   | 6.9 Switching Characteristics, 5 V    |    | 11.4 Trademarks                      | 33               |

|   | 6.10 Switching Characteristics, 3.3 V |    | 11.5 Electrostatic Discharge Caution | 33               |

|   | 6.11 Switching Characteristics, 2.7 V |    | 11.6 Glossary                        | 33               |

|   | 6.12 Typical Characteristics          | 12 | Mechanical, Packaging, and Orderable |                  |

| 7 | Detailed Description                  |    | Information                          | 33               |

| - |                                       |    |                                      |                  |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI       | hanges from Revision E (March 2013) to Revision F                                                                                                                                                                                                                                                                            | Page |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •        | Added Pin Configuration and Functions section, ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section |      |

| •        | Removed I <sub>OS</sub> over temperature limit in <i>Electrical Characteristics</i> , 2.7 V                                                                                                                                                                                                                                  | 8    |

| •        | Moved the SAG Compensation section to the Typical Application section.                                                                                                                                                                                                                                                       | 25   |

| <u>•</u> | Changed section titled Other Applications to Charge Preamplifier                                                                                                                                                                                                                                                             | 28   |

| CI       | hanges from Revision D (March 2013) to Revision E                                                                                                                                                                                                                                                                            | Page |

| •        | Changed layout of National Data Sheet to TI format                                                                                                                                                                                                                                                                           | 1    |

Submit Documentation Feedback

Copyright © 2006–2015, Texas Instruments Incorporated

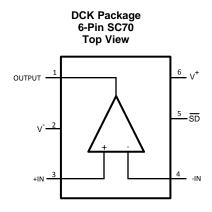

## 5 Pin Configuration and Functions

#### Pin Functions

| PIN |                | 1/0 | DESCRIPTION        |

|-----|----------------|-----|--------------------|

| NO. | NAME           | I/O | DESCRIPTION        |

| 1   | OUTPUT         | 0   | Output             |

| 2   | V <sup>-</sup> | I   | Negative supply    |

| 3   | +IN            | 1   | Noninverting input |

| 4   | -IN            | I   | Inverting input    |

| 5   | SD             | I   | Shutdown           |

| 6   | V <sup>+</sup> | I   | Positive supply    |

## 6 Specifications

## 6.1 Absolute Maximum Ratings<sup>(1)</sup>

|                                                   |                                  | MIN | MAX                            | UNIT |  |

|---------------------------------------------------|----------------------------------|-----|--------------------------------|------|--|

| V <sub>IN</sub> Differential                      |                                  |     | ±2.5                           | V    |  |

| Input Current <sup>(2)</sup>                      | ±10                              |     | mA                             |      |  |

| Output Current                                    |                                  |     | 200 mA <sup>(3)</sup>          | mA   |  |

| Supply Voltage (V <sup>+</sup> – V <sup>-</sup> ) | $(V^+ - V^-)$ 6                  |     | V                              |      |  |

| Voltage at Input/Output Pins                      | oltage at Input/Output Pins      |     | V++0.5,<br>V <sup>-</sup> −0.5 | V    |  |

| Junction Temperature                              |                                  |     | 150                            | °C   |  |

| Coldoring Information                             | Infrared or Convection (20 sec.) |     | 235                            |      |  |

| Soldering Information                             | Wave Soldering (10 sec.)         |     | 260                            | °C   |  |

| Storage Temperature                               |                                  | -65 | 150                            | °C   |  |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings - for LMH6601

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000 | V    |

<sup>(1)</sup> Human Body Model, applicable std. MIL-STD-883, Method 3015.7.

<sup>(2)</sup> Negative input current implies current flowing out of the device.

<sup>(3)</sup> The maximum continuous output current (I<sub>OUT</sub>) is determined by device power dissipation limitations.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.3 ESD Ratings - for LMH6601-Q1

|                                            |                                              |                                                         | VALUE | UNIT |

|--------------------------------------------|----------------------------------------------|---------------------------------------------------------|-------|------|

| V                                          | Flootrootatio disaborge                      | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> | ±2000 |      |

| V <sub>(ESD)</sub> Electrostatic discharge | Charged-device model (CDM), per AEC Q100-011 | ±1000                                                   | V     |      |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 6.4 Recommended Operating Conditions<sup>(1)</sup>

|                                                   | MIN | MAX | UNIT |

|---------------------------------------------------|-----|-----|------|

| Supply Voltage (V <sup>+</sup> – V <sup>-</sup> ) | 2.4 | 5.5 | V    |

| Operating Temperature                             | -40 | 85  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.5 Thermal Information

| (4)                                                     | LMH6601,<br>LMH6601-Q1 |      |

|---------------------------------------------------------|------------------------|------|

| THERMAL METRIC <sup>(1)</sup>                           | DCK (SC70)             | UNIT |

|                                                         | 6 PINS                 |      |

| R <sub>θJA</sub> Junction-to-ambient thermal resistance | 414                    | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

#### 6.6 Electrical Characteristics, 5 V

Single-Supply with  $V_S = 5 \text{ V}$ ,  $A_V = +2$ ,  $R_F = 604 \Omega$ ,  $\overline{SD}$  tied to  $V^+$ ,  $V_{OUT} = V_S/2$ ,  $R_I = 150 \Omega$  to  $V^-$  unless otherwise specified. (1)

|                  | PARAMETER                     | TEST CONDITIONS                                                                                   | MIN <sup>(2)</sup> | TYP <sup>(2)</sup> | MAX <sup>(2)</sup> | UNIT    |

|------------------|-------------------------------|---------------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|---------|

| FREQUENCY        | Y DOMAIN RESPONSE             |                                                                                                   |                    |                    |                    |         |

| SSBW             | O JD Dood width Occall O'coal | $V_{OUT} = 0.25 V_{PP}$                                                                           |                    | 130                |                    | N.41.1- |

| SSBW_1           | -3-dB Bandwidth Small Signal  | $V_{OUT} = 0.25 V_{PP}, A_V = +1$                                                                 |                    | 250                |                    | MHz     |

| Peak             | Peaking                       | $V_{OUT} = 0.25 V_{PP}, A_V = +1$                                                                 |                    | 2.5                |                    | dB      |

| Peak_1           | Peaking                       | $V_{OUT} = 0.25 V_{PP}$                                                                           |                    | 0                  |                    | dB      |

| LSBW             | -3-dB Bandwidth Large Signal  | V <sub>OUT</sub> = 2 V <sub>PP</sub>                                                              |                    | 81                 |                    | MHz     |

| Peak_2           | Peaking                       | V <sub>OUT</sub> = 2 V <sub>PP</sub>                                                              |                    | 0                  |                    | dB      |

| 0.1 dB BW        | 0.1-dB Bandwidth              | V <sub>OUT</sub> = 2 V <sub>PP</sub>                                                              |                    | 30                 |                    | MHz     |

| GBWP_1k          | Onia Banda idib Banda d       | Unity Gain, $R_L = 1 \text{ k}\Omega \text{ to } V_S/2$                                           |                    | 155                |                    | N.41.1- |

| GBWP_150         | Gain Bandwidth Product        | Unity Gain, $R_L = 150 \Omega$ to $V_S/2$                                                         |                    | 125                |                    | MHz     |

| A <sub>VOL</sub> | Large Signal Open-Loop Gain   | 0.5 V < V <sub>OUT</sub> < 4.5 V                                                                  | 56                 | 66                 |                    | dB      |

| PBW              | Full Power BW                 | $-1$ dB, $A_V = +4$ , $V_{OUT} = 4.2 V_{PP}$ , $R_L = 150 \Omega$ to $V_S/2$                      |                    | 30                 |                    | MHz     |

| DG               | Differential Gain             | 4.43 MHz, 1.7 V $\leq$ V <sub>OUT</sub> $\leq$ 3.3 V,<br>R <sub>L</sub> = 150 Ω to V <sup>-</sup> |                    | 0.06%              |                    |         |

| DP               | Differential Phase            | 4.43 MHz, 1.7 V $\leq$ V <sub>OUT</sub> $\leq$ 3.3 V R <sub>L</sub> = 150 Ω to V <sup>-</sup>     |                    | 0.10               |                    | deg     |

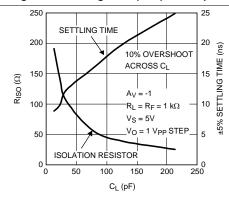

| TIME DOMA        | IN RESPONSE                   |                                                                                                   |                    |                    |                    |         |

| OS               | Overshoot                     | 0.25-V Step                                                                                       |                    | 10%                |                    |         |

| C <sub>L</sub>   | Capacitor Load Tolerance      | $A_V = -1$ , 10% Overshoot, 75 $\Omega$ in Series                                                 |                    | 50                 |                    | pF      |

<sup>(1)</sup> Electrical Characteristics, 5 V values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that T<sub>J</sub> = T<sub>A</sub>. No specification of parametric performance is indicated in the electrical tables under conditions of internal self-heating where T<sub>J</sub> > T<sub>A</sub>.

<sup>(2)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

## **Electrical Characteristics, 5 V (continued)**

Single-Supply with  $V_S = 5 \text{ V}$ ,  $A_V = +2$ ,  $R_F = 604 \Omega$ ,  $\overline{SD}$  tied to  $V^+$ ,  $V_{OUT} = V_S/2$ ,  $R_L = 150 \Omega$  to  $V^-$  unless otherwise specified. (1)

|                  | PARAMETER                                 | TEST C                                                   | ONDITIONS                   | MIN <sup>(2)</sup>    | TYP <sup>(2)</sup> | MAX <sup>(2)</sup>   | UNIT               |

|------------------|-------------------------------------------|----------------------------------------------------------|-----------------------------|-----------------------|--------------------|----------------------|--------------------|

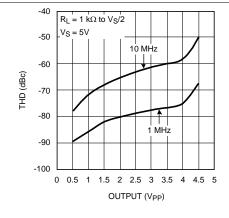

| DISTORTION       | N and NOISE PERFORMANCE                   |                                                          |                             |                       |                    |                      |                    |

| HD2              |                                           | 2 V <sub>PP</sub> , 10 MHz                               |                             |                       | -56                |                      |                    |

| HD2_1            | Harmonic Distortion (2 <sup>nd</sup> )    | 4 V <sub>PP</sub> , 10 MHz, R <sub>L</sub>               | = 1 kΩ to V <sub>S</sub> /2 |                       | -61                |                      | dBc                |

| HD3              |                                           | 2 V <sub>PP</sub> , 10 MHz                               |                             |                       | -73                |                      |                    |

| HD3_1            | Harmonic Distortion (3 <sup>rd</sup> )    | 4 V <sub>PP</sub> , 10 MHz, R <sub>L</sub>               | = 1 kΩ to V <sub>S</sub> /2 |                       | -64                |                      | dBc                |

| THD              | Total Harmonic Distortion                 | 4 V <sub>PP</sub> , 10 MHz, R <sub>L</sub>               |                             |                       | -58                |                      |                    |

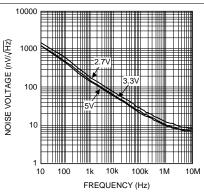

| V <sub>N1</sub>  |                                           | >10 MHz                                                  | <del>-</del>                |                       | 7                  |                      |                    |

| V <sub>N2</sub>  | Input Voltage Noise                       | 1 MHz                                                    |                             |                       | 10                 |                      | nV/√ <del>Hz</del> |

| I <sub>N</sub>   | Input Current Noise                       | >1 MHz                                                   |                             |                       | 50                 |                      | fA/√Hz             |

| STATIC, DC       | PERFORMANCE                               | 1                                                        |                             |                       |                    |                      |                    |

| .,               |                                           |                                                          |                             |                       | ±1                 | ±2.4                 | .,                 |

| $V_{IO}$         | Input Offset Voltage                      | At temperature extr                                      | emes                        |                       |                    | ±5                   | mV                 |

| DV <sub>IO</sub> | Input Offset Voltage Average Drift        | See (3)                                                  |                             |                       | -5                 |                      | μV/°C              |

| I <sub>B</sub>   | Input Bias Current                        | See (4)                                                  |                             |                       | 5                  | 50                   | pА                 |

| Ios              | Input Offset Current                      | See (4)                                                  |                             |                       | 2                  | 25                   | pА                 |

| R <sub>IN</sub>  | Input Resistance                          | $0 \text{ V} \le \text{V}_{\text{IN}} \le 3.5 \text{ V}$ |                             |                       | 10                 |                      | ΤΩ                 |

| C <sub>IN</sub>  | Input Capacitance                         |                                                          |                             |                       | 1.3                |                      | pF                 |

|                  | Davids and Davids Occupated Davids of the |                                                          |                             | 55                    | 59                 |                      |                    |

| +PSRR            | Positive Power Supply Rejection Ratio     | DC                                                       | At temperature extremes     | 51                    |                    |                      | dB                 |

|                  | Negative Dawer Cumply Dejection           |                                                          |                             | 53                    | 61                 |                      |                    |

| -PSRR            | Negative Power Supply Rejection Ratio     | DC                                                       | At temperature extremes     | 50                    |                    |                      | dB                 |

|                  |                                           |                                                          |                             | 56                    | 68                 |                      |                    |

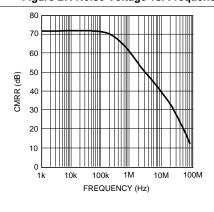

| CMRR             | Common-Mode Rejection Ratio               | DC                                                       | At temperature extremes     | 53                    |                    |                      | dB                 |

| CMVR             | Input Voltage Range                       | CMRR > 50 dB (At extremes)                               | temperature                 | V <sup>-</sup> – 0.20 | -                  | V <sup>+</sup> – 1.5 | V                  |

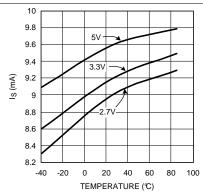

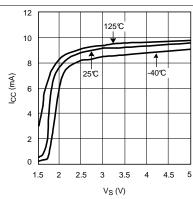

|                  |                                           | Normal Operation                                         |                             |                       | 9.6                | 11.5                 |                    |

| I <sub>cc</sub>  | Supply Current                            | Normal Operation<br>V <sub>OUT</sub> = V <sub>S</sub> /2 | At temperature extremes     |                       |                    | 13.5                 | mA                 |

|                  |                                           | Shutdown<br>SD tied to ≤ 0.5 V (                         | 5)                          |                       | 100                |                      | nA                 |

|                  |                                           |                                                          |                             | -210                  | -190               |                      |                    |

| VOH1             |                                           | $R_L = 150 \Omega \text{ to V}^-$                        | At temperature extremes     | -480                  |                    |                      |                    |

| VOH2             | Output High Voltage                       | $R_L = 75 \Omega \text{ to } V_S/2$                      | <del>'</del>                |                       | -190               |                      | mV                 |

|                  | (Notative to v )                          |                                                          |                             | -60                   | -12                |                      |                    |

| VOH3             | (Relative to V <sup>+</sup> )             | $R_L = 10 \text{ k}\Omega \text{ to V}^-$                | At temperature extremes     | -110                  |                    |                      |                    |

Drift determined by dividing the change in parameter at temperature extremes by the total temperature change. This parameter is ensured by design and/or characterization and is not tested in production.

SD logic is CMOS compatible. To ensure proper logic level and to minimize power supply current, SD should typically be less than 10% of total supply voltage away from either supply rail.

#### **Electrical Characteristics, 5 V (continued)**

Single-Supply with  $V_S = 5 \text{ V}$ ,  $A_V = +2$ ,  $R_F = 604 \Omega$ ,  $\overline{SD}$  tied to  $V^+$ ,  $V_{OUT} = V_S/2$ ,  $R_L = 150 \Omega$  to  $V^-$  unless otherwise specified. (1)

|                          | PARAMETER                                           | TEST CO                                                    | ONDITIONS               | MIN <sup>(2)</sup> | TYP <sup>(2)</sup> | MAX <sup>(2)</sup> | UNIT |

|--------------------------|-----------------------------------------------------|------------------------------------------------------------|-------------------------|--------------------|--------------------|--------------------|------|

|                          |                                                     |                                                            |                         |                    | 5                  | 45                 |      |

| VOL1                     |                                                     | $R_L = 150 \Omega \text{ to V}^-$                          | At temperature extremes |                    |                    | 125                |      |

| VOL2                     | Output Low Voltage<br>(Relative to V <sup>-</sup> ) | $R_L = 75 \Omega \text{ to } V_S/2$                        |                         |                    | 120                |                    | mV   |

|                          | (relative to v)                                     |                                                            |                         |                    | 5                  | 45                 |      |

| VOL3                     |                                                     | $R_L = 10 \text{ k}\Omega \text{ to V}^-$                  | At temperature extremes |                    |                    | 125                |      |

|                          |                                                     | V <sub>OUT</sub> < 0.6 V from                              | Source                  |                    | 150                |                    |      |

| Io                       | Output Current                                      | Respective Supply                                          | Sink                    |                    | 180                |                    | mA   |

| I <sub>O</sub> _1        | - Culput Current                                    | $V_{OUT} = V_{S}/2,$<br>$V_{ID} = \pm 18 \text{ mV}^{(6)}$ |                         | ±100               |                    |                    | IIIZ |

| Load                     | Output Load Rating                                  | THD < $-30$ dBc, f = $R_L$ tied to $V_S/2$ , $V_{OL}$      | ,                       |                    | 20                 |                    | Ω    |

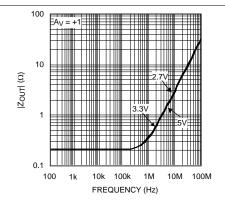

| R <sub>O</sub> _Enabled  | Output Resistance                                   | Enabled, A <sub>V</sub> = +1                               |                         |                    | 0.2                |                    | Ω    |

| R <sub>O</sub> _Disabled | Output Resistance                                   | Shutdown                                                   |                         |                    | >100               |                    | МΩ   |

| C <sub>O</sub> _Disabled | Output Capacitance                                  | Shutdown                                                   |                         |                    | 5                  |                    | pF   |

| MISCELLANE               | EOUS PERFORMANCE                                    | •                                                          |                         | ·                  |                    | ·                  |      |

| VDMAX                    | Voltage Limit for Disable (Pin 5)                   | See (5) (At tempera                                        | ture extremes)          | 0                  |                    | 0.5                | V    |

| VDMIN                    | Voltage Limit for Enable (Pin 5)                    | See (5) (At tempera                                        | ture extremes)          | 4.5                |                    | 5                  | V    |

| Ii                       | Logic Input Current (Pin 5)                         | <del>SD</del> = 5 V <sup>(5)</sup>                         |                         |                    | 10                 |                    | pА   |

| V_glitch                 | Turnon Glitch                                       |                                                            |                         |                    | 2.2                |                    | V    |

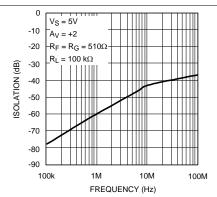

| Isolation <sub>OFF</sub> | Off Isolation                                       | 1 MHz, $R_L = 1 k\Omega$                                   |                         |                    | 60                 |                    | dB   |

<sup>(6) &</sup>quot;V<sub>ID</sub>" is input differential voltage (input overdrive).

#### 6.7 Electrical Characteristics, 3.3 V

Single-Supply with  $V_S = 3.3 \text{ V}$ ,  $A_V = +2$ ,  $R_F = 604\Omega$ ,  $\overline{SD}$  tied to  $V^+$ ,  $V_{OUT} = V_S/2$ ,  $R_L = 150 \Omega$  to  $V^-$  unless otherwise specified. (1)

|                  | PARAMETER                    | TEST CONDITIONS                                                                                                     | MIN <sup>(2)</sup> TYP <sup>(2)</sup> MAX <sup>(2)</sup> | UNIT   |

|------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------|

| FREQUENCY        | DOMAIN RESPONSE              |                                                                                                                     |                                                          |        |

| SSBW             | 2 dD Dondwidth Cmall Cianal  | V <sub>OUT</sub> = 0.25 V <sub>PP</sub>                                                                             | 125                                                      | NAL I- |

| SSBW_1           | -3-dB Bandwidth Small Signal | $V_{OUT} = 0.25 V_{PP}, A_V = +1$                                                                                   | 250                                                      | MHz    |

| Peak             | Peaking                      | $V_{OUT} = 0.25 V_{PP}, A_V = +1$                                                                                   | 3                                                        | dB     |

| Peak_1           | Peaking                      | $V_{OUT} = 0.25 V_{PP}$                                                                                             | 0.05                                                     | dB     |

| LSBW             | -3-dB Bandwidth Large Signal | V <sub>OUT</sub> = 2 V <sub>PP</sub>                                                                                | 75                                                       | MHz    |

| Peak_2           | Peaking                      | V <sub>OUT</sub> = 2 V <sub>PP</sub>                                                                                | 0                                                        | dB     |

| 0.1 dB BW        | 0.1-dB Bandwidth             | V <sub>OUT</sub> = 2 V <sub>PP</sub>                                                                                | 30                                                       | MHz    |

| GBWP_1k          | Caia Baadhiidth Baadhat      | Unity Gain, $R_L = 1 \text{ k}\Omega$ to $V_S/2$                                                                    | 115                                                      | N41.1- |

| GBWP_150         | Gain Bandwidth Product       | Unity Gain, $R_L = 150 \Omega$ to $V_S/2$                                                                           | 105                                                      | MHz    |

| A <sub>VOL</sub> | Large Signal Open-Loop Gain  | 0.3 V < V <sub>OUT</sub> < 3 V                                                                                      | 56 67                                                    | dB     |

| PBW              | Full Power BW                | -1 dB, A <sub>V</sub> = +4, V <sub>OUT</sub> = 2.8 V <sub>PP</sub> ,<br>R <sub>L</sub> = 150 Ω to V <sub>S</sub> /2 | 30                                                       | MHz    |

| DG               | Differential Gain            | 4.43 MHz, 0.85 V $\leq$ V <sub>OUT</sub> $\leq$ 2.45 V,<br>R <sub>L</sub> = 150 Ω to V <sup>-</sup>                 | 0.06%                                                    |        |

| DP               | Differential Phase           | 4.43 MHz, 0.85 V $\leq$ V <sub>OUT</sub> $\leq$ 2.45 V R <sub>L</sub> = 150 Ω to V <sup>-</sup>                     | 0.23                                                     | deg    |

<sup>(1)</sup> Electrical Characteristics, 3.3 V values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that T<sub>J</sub> = T<sub>A</sub>. No specification of parametric performance is indicated in the electrical tables under conditions of internal self-heating where T<sub>J</sub> > T<sub>A</sub>.

Submit Documentation Feedback

Copyright © 2006–2015, Texas Instruments Incorporated

<sup>(2)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

## **Electrical Characteristics, 3.3 V (continued)**

Single-Supply with  $V_s = 3.3 \text{ V}$ ,  $A_{V_s} = +2$ ,  $R_E = 604\Omega$ ,  $\overline{\text{SD}}$  tied to  $V^+$ ,  $V_{OUT} = V_s/2$ ,  $R_L = 150 \Omega$  to  $V^-$  unless otherwise specified. (1)

|                  | PARAMETER                                         | TEST C                                                                              | ONDITIONS                  | MIN <sup>(2)</sup>    | TYP <sup>(2)</sup> | MAX <sup>(2)</sup>   | UNIT    |

|------------------|---------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------|-----------------------|--------------------|----------------------|---------|

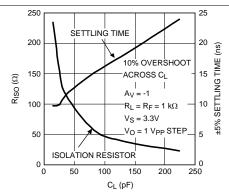

| TIME DOMA        | IN RESPONSE                                       |                                                                                     |                            |                       |                    |                      |         |

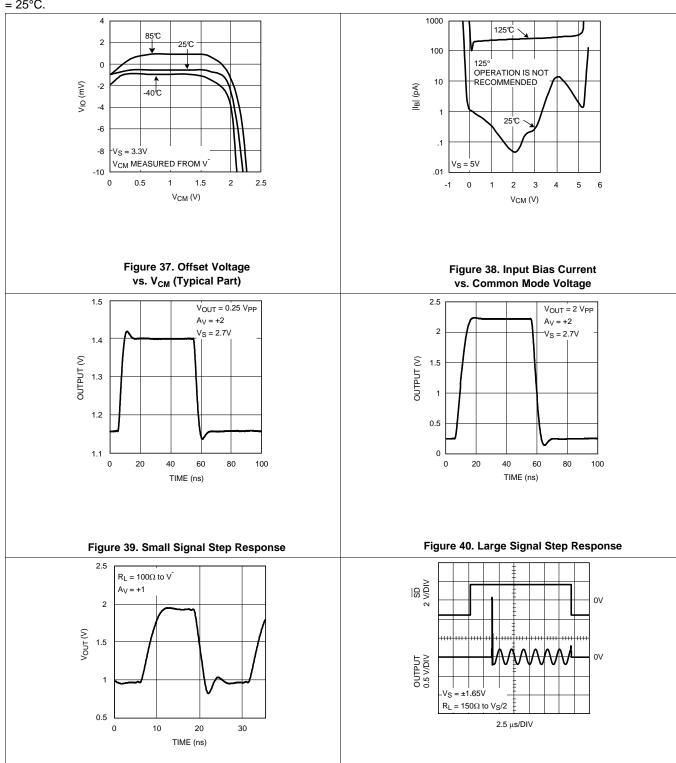

| OS               | Overshoot                                         | 0.25-V Step                                                                         |                            |                       | 10%                |                      |         |

| C <sub>L</sub>   | Capacitor Load Tolerance                          | $A_V = -1$ , 10% Ove                                                                | rshoot, 82 Ω in Series     |                       | 50                 |                      | pF      |

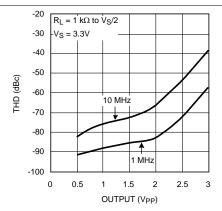

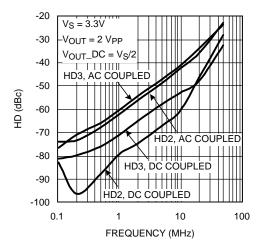

| DISTORTIO        | N and NOISE PERFORMANCE                           | 1                                                                                   |                            |                       |                    |                      | -       |

| HD2              |                                                   | 2 V <sub>PP</sub> , 10 MHz                                                          |                            |                       | -61                |                      |         |

| HD2_1            | Harmonic Distortion (2 <sup>nd</sup> )            | 2 V <sub>PP</sub> , 10 MHz<br>R <sub>L</sub> = 1 k $\Omega$ to V <sub>S</sub> /2    |                            |                       | -79                |                      | dBc     |

| HD3              |                                                   | 2 V <sub>PP</sub> , 10 MHz                                                          |                            |                       | -53                |                      |         |

| HD3_2            | Harmonic Distortion (3 <sup>rd</sup> )            | $2 \text{ V}_{PP}$ , $10 \text{ MHz}$<br>$R_L = 1 \text{ k}\Omega \text{ to V}_S/2$ |                            |                       | -69                |                      | dBc     |

| THD              | Total Harmonic Distortion                         | 2 $V_{PP}$ , 10 MHz<br>$R_L = 1 k\Omega$ to $V_S/2$                                 |                            |                       | -66                |                      | dBc     |

| V <sub>N1</sub>  | Innut Valta an Nainn                              | >10 MHz                                                                             |                            |                       | 7                  |                      | >//:/\_ |

| V <sub>N2</sub>  | Input Voltage Noise                               | 1 MHz                                                                               |                            |                       | 10                 |                      | nV/√Hz  |

| I <sub>N</sub>   | Input Current Noise                               | >1 MHz                                                                              |                            |                       | 50                 |                      | fA/√Hz  |

| STATIC, DO       | PERFORMANCE                                       |                                                                                     |                            |                       |                    |                      |         |

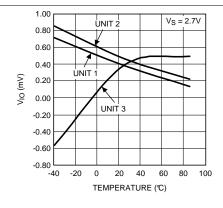

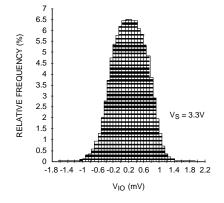

|                  | Langet Office t Mallage                           |                                                                                     |                            |                       | ±1                 | ±2.6                 |         |

| $V_{IO}$         | Input Offset Voltage                              | At temperature extremes                                                             |                            |                       |                    | ±5.5                 | mV      |

| DV <sub>IO</sub> | Input Offset Voltage Average Drift                | See (3)                                                                             |                            |                       | -4.5               |                      | μV/°C   |

| I <sub>B</sub>   | Input Bias Current                                | See (4)                                                                             |                            |                       | 5                  | 50                   | pА      |

| Ios              | Input Offset Current                              | See (4)                                                                             |                            |                       | 2                  | 25                   | pА      |

| R <sub>IN</sub>  | Input Resistance                                  | 0 V ≤ V <sub>IN</sub> ≤ 1.8 V                                                       |                            |                       | 15                 |                      | ΤΩ      |

| C <sub>IN</sub>  | Input Capacitance                                 |                                                                                     |                            |                       | 1.4                |                      | pF      |

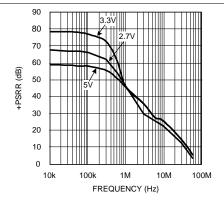

| 0000             | Positive Power Supply Rejection                   | DC                                                                                  |                            | 61                    | 80                 |                      |         |

| +PSRR            | Ratio                                             | At temperature extremes                                                             |                            | 51                    |                    |                      | dB      |

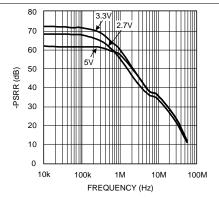

| 0000             | Negative Power Supply Rejection                   | DC                                                                                  |                            | 57                    | 72                 |                      |         |

| -PSRR            | Ratio                                             | At temperature ext                                                                  | remes                      | 52                    |                    |                      | dB      |

| OMBB             | 0 11 1 2 1 1 2 1                                  | DC                                                                                  |                            | 58                    | 73                 |                      |         |

| CMRR             | Common-Mode Rejection Ratio                       | At temperature ext                                                                  | remes                      | 55                    |                    |                      | dB      |

| CMVR             | Input Voltage                                     | CMRR > 50 dB (At extremes)                                                          | temperature                | V <sup>-</sup> - 0.20 |                    | V <sup>+</sup> – 1.5 | ٧       |

|                  |                                                   | Name of One section                                                                 |                            |                       | 9.2                | 11                   |         |

| I <sub>CC</sub>  | Supply Current                                    | Normal Operation $V_{OUT} = V_{S}/2$                                                | At temperature extremes    |                       |                    | 13                   | mA      |

|                  |                                                   | Shutdown: SD tied                                                                   | to ≤ 0.33 V <sup>(5)</sup> |                       | 100                |                      | nA      |

|                  |                                                   |                                                                                     |                            | -210                  | -190               |                      |         |

| VOH1             |                                                   | $R_L = 150 \Omega \text{ to V}^-$                                                   | At temperature extremes    | -360                  |                    |                      |         |

| VOH2             | Output High Voltage (Relative to V <sup>+</sup> ) | $R_L = 75 \Omega \text{ to } V_S/2$                                                 |                            |                       | -190               |                      | mV      |

|                  | (Iverative to v )                                 |                                                                                     |                            | -50                   | -10                |                      |         |

| VOH3             |                                                   | $R_L = 10 \text{ k}\Omega \text{ to V}^-$                                           | At temperature extremes    | -100                  |                    |                      |         |

Drift determined by dividing the change in parameter at temperature extremes by the total temperature change. This parameter is ensured by design and/or characterization and is not tested in production.

SD logic is CMOS compatible. To ensure proper logic level and to minimize power supply current, SD should typically be less than 10% of total supply voltage away from either supply rail.

#### **Electrical Characteristics, 3.3 V (continued)**

Single-Supply with  $V_S = 3.3 \text{ V}$ ,  $A_V = +2$ ,  $R_F = 604\Omega$ ,  $\overline{SD}$  tied to  $V^+$ ,  $V_{OUT} = V_S/2$ ,  $R_L = 150 \Omega$  to  $V^-$  unless otherwise specified. (1)

|                          | PARAMETER                                           | TEST C                                                                                                            | ONDITIONS               | MIN <sup>(2)</sup> | TYP <sup>(2)</sup> | MAX <sup>(2)</sup> | UNIT |

|--------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------|--------------------|--------------------|------|

|                          |                                                     |                                                                                                                   |                         |                    | 4                  | 45                 |      |

| VOL1                     |                                                     | $R_L = 150 \Omega \text{ to V}^-$                                                                                 | At temperature extremes |                    |                    | 125                |      |

| VOL2                     | Output Low Voltage<br>(Relative to V <sup>-</sup> ) |                                                                                                                   |                         |                    | 105                |                    | mV   |

|                          | (itolauvo to 1)                                     |                                                                                                                   |                         |                    | 4                  | 45                 |      |

| VOL3                     |                                                     | $R_L = 10 \text{ k}\Omega \text{ to V}^-$                                                                         | At temperature extremes |                    |                    | 125                |      |

|                          |                                                     | V <sub>OUT</sub> < 0.6 V from                                                                                     | Source                  |                    | 50                 |                    |      |

| lo                       | Output Current                                      | Respective<br>Supply                                                                                              | Sink                    |                    | 75                 |                    | mA   |

| I <sub>O</sub> _1        |                                                     | $V_{OUT} = V_S/2, V_{ID} =$                                                                                       | ±18 mV <sup>(6)</sup>   | ±75                |                    |                    |      |

| Load                     | Output Load Rating                                  | THD < $-30$ dBc, f = 200 kHz,<br>R <sub>L</sub> tied to V <sub>S</sub> /2, V <sub>OUT</sub> = 2.6 V <sub>PP</sub> |                         |                    | 25                 |                    | Ω    |

| R <sub>O</sub> _Enabled  | Output Resistance                                   | Enabled, A <sub>V</sub> = +1                                                                                      |                         |                    | 0.2                |                    | Ω    |

| R <sub>O</sub> _Disabled | Output Resistance                                   | Shutdown                                                                                                          |                         |                    | >100               |                    | МΩ   |

| C <sub>O</sub> _Disabled | Output Capacitance                                  | Shutdown                                                                                                          |                         |                    | 5.6                |                    | pF   |

| MISCELLANE               | OUS PERFORMANCE                                     |                                                                                                                   |                         |                    |                    |                    |      |

| VDMAX                    | Voltage Limit for Disable (Pin 5)                   | See (5) (At tempera                                                                                               | ature extremes)         | 0                  |                    | 0.33               | V    |

| VDMIN                    | Voltage Limit for Enable (Pin 5)                    | See <sup>(5)</sup> (At temperature extremes)                                                                      |                         | 2.97               |                    | 3.3                | V    |

| li                       | Logic Input Current (Pin 5)                         | $\overline{SD} = 3.3 \text{ V}^{(5)}$                                                                             |                         |                    | 8                  |                    | рА   |

| V_glitch                 | Turnon Glitch                                       |                                                                                                                   |                         |                    | 1.6                | _                  | V    |

| Isolation <sub>OFF</sub> | Off Isolation                                       | 1 MHz, $R_L = 1 k\Omega$                                                                                          |                         |                    | 60                 |                    | dB   |

<sup>(6) &</sup>quot;V<sub>ID</sub>" is input differential voltage (input overdrive).

#### 6.8 Electrical Characteristics, 2.7 V

Single-Supply with  $V_S = 2.7$  V,  $A_V = +2$ ,  $R_F = 604$   $\Omega$ ,  $\overline{SD}$  tied to V<sup>+</sup>,  $V_{OUT} = V_S/2$ ,  $R_L = 150$   $\Omega$  to V<sup>-</sup> unless otherwise specified. (1)

|                  | PARAMETER                    | TEST CONDITIONS                                                                           | MIN <sup>(2)</sup> TYP <sup>(2)</sup> MAX <sup>(2)</sup> | UNIT   |

|------------------|------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------|--------|

| FREQUENCY        | DOMAIN RESPONSE              |                                                                                           |                                                          |        |

| SSBW             | -3-dB Bandwidth Small Signal | $V_{OUT} = 0.25 V_{PP}$                                                                   | 120                                                      | MHz    |

| SSBW_1           | -3-ub Bandwidth Small Signal | $V_{OUT} = 0.25 V_{PP}, A_V = +1$                                                         | 250                                                      | IVITIZ |

| Peak             | Peaking                      | $V_{OUT} = 0.25 V_{PP}, A_V = +1$                                                         | 3.1                                                      | dB     |

| Peak_1           | Peaking                      | $V_{OUT} = 0.25 V_{PP}$                                                                   | 0.1                                                      | dB     |

| LSBW             | -3-dB Bandwidth Large Signal | $V_{OUT} = 2 V_{PP}$                                                                      | 73                                                       | MHz    |

| Peak_2           | Peaking                      | $V_{OUT} = 2 V_{PP}$                                                                      | 0                                                        | dB     |

| 0.1 dB BW        | 0.1-dB Bandwidth             | $V_{OUT} = 2 V_{PP}$                                                                      | 30                                                       | MHz    |

| GBWP_1k          | Gain Bandwidth Product       | Unity Gain, $R_L = 1 k\Omega$ to $V_S/2$                                                  | 110                                                      | NAL I- |

| GBWP_150         | Gain Bandwidth Product       | Unity Gain, $R_L = 150 \Omega$ to $V_S/2$                                                 | 81                                                       | MHz    |

| A <sub>VOL</sub> | Large Signal Open-Loop Gain  | 0.25 V < V <sub>OUT</sub> < 2.5 V                                                         | 56 65                                                    | dB     |

| PBW              | Full Power BW                | $-1$ dB, $A_V = +4$ , $V_{OUT} = 2$ $V_{PP}$ , $R_L = 150 \Omega$ to $V_S/2$              | 13                                                       | MHz    |

| DG               | Differential Gain            | 4.43 MHz, 0.45 V $\leq$ V <sub>OUT</sub> $\leq$ 2.05 V R <sub>L</sub> = 150 $\Omega$ to V | 0.12%                                                    |        |

<sup>(1)</sup> Electrical Characteristics, 2.7 V values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No specification of parametric performance is indicated in the electrical tables under conditions of internal self-heating where  $T_J > T_A$ .

Submit Documentation Feedback

Copyright © 2006-2015, Texas Instruments Incorporated

Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

## **Electrical Characteristics, 2.7 V (continued)**

Single-Supply with  $V_S = 2.7$  V,  $A_V = +2$ ,  $R_F = 604$   $\Omega$ ,  $\overline{SD}$  tied to  $V^+$ ,  $V_{OUT} = V_S/2$ ,  $R_L = 150$   $\Omega$  to  $V^-$  unless otherwise specified. (1)

|                  | PARAMETER                                         | TEST C                                            | ONDITIONS                   | MIN <sup>(2)</sup>    | TYP <sup>(2)</sup> | MAX <sup>(2)</sup>   | UNIT               |

|------------------|---------------------------------------------------|---------------------------------------------------|-----------------------------|-----------------------|--------------------|----------------------|--------------------|

| DP               | Differential Phase                                | 4.43 MHz, 0.45 V :<br>R <sub>L</sub> = 150 Ω to V | ≤ V <sub>OUT</sub> ≤ 2.05 V |                       | 0.62               |                      | deg                |

| TIME DOM         | AIN RESPONSE                                      | + -                                               |                             | +                     |                    |                      |                    |

| OS               | Overshoot                                         | 0.25-V Step                                       |                             |                       | 10%                |                      |                    |

| DISTORTIO        | ON and NOISE PERFORMANCE                          | -                                                 |                             |                       |                    |                      |                    |

| HD2              | Harmonic Distortion (2 <sup>nd</sup> )            | 1 V <sub>PP</sub> , 10 MHz                        |                             |                       | -58                |                      | dBc                |

| HD3              | Harmonic Distortion (3 <sup>rd</sup> )            | 1 V <sub>PP</sub> , 10 MHz                        |                             |                       | -60                |                      | dBc                |

| V <sub>N1</sub>  |                                                   | >10 MHz                                           |                             |                       | 8.4                |                      |                    |

| V <sub>N2</sub>  | Input Voltage Noise                               | 1 MHz                                             |                             |                       | 12                 |                      | nV/√Hz             |

| I <sub>N</sub>   | Input Current Noise                               | >1 MHz                                            |                             |                       | 50                 |                      | fA/√ <del>Hz</del> |

|                  | C PERFORMANCE                                     |                                                   |                             |                       |                    |                      |                    |

|                  |                                                   |                                                   |                             |                       | ±1                 | ±3.5                 |                    |

| V <sub>IO</sub>  | Input Offset Voltage                              | At temperature ext                                | remes                       |                       |                    | ±6.5                 | mV                 |

| DV <sub>IO</sub> | Input Offset Voltage Average Drift                | See (3)                                           | •                           |                       | -6.5               |                      | μV/°C              |

| I <sub>B</sub>   | Input Bias Current                                | See (4)                                           |                             |                       | 5                  | 50                   | pA                 |

| I <sub>OS</sub>  | Input Offset Current                              | See (4)                                           |                             |                       | 2                  | 25                   | pA                 |

| R <sub>IN</sub>  | Input Resistance                                  | 0V ≤ V <sub>IN</sub> ≤ 1.2V                       |                             |                       | 20                 |                      | ΤΩ                 |

| C <sub>IN</sub>  | Input Capacitance                                 | 0                                                 |                             |                       | 1.6                |                      | pF                 |

| - IIV            | mput Capacitance                                  |                                                   |                             | 58                    | 68                 |                      | P'                 |

| +PSRR            | Positive Power Supply Rejection Ratio             | DC                                                | At temperature extremes     | 53                    |                    |                      | dB                 |

|                  |                                                   |                                                   |                             | 56                    | 69                 |                      |                    |

| -PSRR            | Negative Power Supply Rejection Ratio             | DC                                                | At temperature extremes     | 53                    |                    |                      | dB                 |

|                  |                                                   |                                                   |                             | 57                    | 77                 |                      |                    |

| CMRR             | Common-Mode Rejection Ratio                       | DC                                                | At temperature extremes     | 52                    |                    |                      | dB                 |

| CMVR             | Input Voltage                                     | CMRR > 50 dB (At extremes)                        | t temperature               | V <sup>-</sup> - 0.20 | -                  | V <sup>+</sup> – 1.5 | V                  |

|                  |                                                   | Name of One of the                                |                             |                       | 9                  | 10.6                 |                    |

| I <sub>CC</sub>  | Supply Current                                    | Normal Operation $V_{OUT} = V_{S}/2$              | At temperature extremes     |                       |                    | 12.5                 | mA                 |

|                  |                                                   | Shutdown<br>SD tied to ≤ 0.27 \                   | <b>/</b> (5)                |                       | 100                |                      | nA                 |

|                  |                                                   |                                                   |                             | -260                  | -200               |                      |                    |

| VOH1             |                                                   | $R_L = 150 \Omega \text{ to V}^-$                 | At temperature extremes     | -420                  |                    |                      |                    |

| VOH2             | Output High Voltage (Relative to V <sup>+</sup> ) | $R_L = 75 \Omega \text{ to } V_S/2$               |                             |                       | -200               |                      | mV                 |

|                  | (Itelative to v )                                 |                                                   |                             | -50                   | -10                |                      |                    |

| VOH3             |                                                   | $R_L = 10 \text{ k}\Omega \text{ to V}^-$         | At temperature extremes     | 100                   |                    |                      |                    |

Drift determined by dividing the change in parameter at temperature extremes by the total temperature change. This parameter is ensured by design and/or characterization and is not tested in production.

SD logic is CMOS compatible. To ensure proper logic level and to minimize power supply current, SD should typically be less than 10% of total supply voltage away from either supply rail.

## **Electrical Characteristics, 2.7 V (continued)**

Single-Supply with  $V_S = 2.7$  V,  $A_V = +2$ ,  $R_F = 604$   $\Omega$ ,  $\overline{SD}$  tied to  $V^+$ ,  $V_{OUT} = V_S/2$ ,  $R_L = 150$   $\Omega$  to  $V^-$  unless otherwise specified. (1)

|                          | PARAMETER                         | TEST C                                                                                  | ONDITIONS               | MIN <sup>(2)</sup> | TYP <sup>(2)</sup> | MAX <sup>(2)</sup> | UNIT |

|--------------------------|-----------------------------------|-----------------------------------------------------------------------------------------|-------------------------|--------------------|--------------------|--------------------|------|

| VOL1                     |                                   | B = 150 O to \/=                                                                        |                         |                    | 4                  | 45                 |      |

| VOLI                     |                                   | $R_L = 150 \Omega \text{ to V}^-$                                                       |                         |                    |                    | 125                |      |

| VOL2                     | Output Low Voltage                | $R_L = 75 \Omega \text{ to } V_S/2$                                                     |                         |                    | 125                |                    | mV   |

|                          | (Relative to V <sup>-</sup> )     |                                                                                         |                         |                    | 4                  | 45                 |      |

| VOL3                     |                                   | $R_L = 10 \text{ k}\Omega \text{ to V}^-$                                               | At temperature extremes |                    |                    | 125                |      |

|                          |                                   | V <sub>OUT</sub> ≤ 0.6 V from                                                           | Source                  |                    | 25                 |                    |      |

| lo                       |                                   | Respective<br>Supply                                                                    | Sink                    |                    | 62                 |                    | mA   |

| I <sub>O</sub> _1        | ·                                 | $V_{OUT} = V_{S}/2, V_{ID}$<br>= ±18 mV <sup>(6)</sup>                                  | Source                  | 25                 |                    |                    |      |

|                          |                                   | $= \pm 18 \text{ mV}^{(6)}$                                                             | Sink                    | 35                 |                    |                    |      |

| Load                     | Output Load Rating                | THD < $-30$ dBc, f = 200 kHz, R <sub>L</sub> tied to $V_S/2$ , $V_{OUT}$ = 2.2 $V_{PP}$ |                         |                    | 40                 |                    | Ω    |

| R <sub>O</sub> _Enable   | Output Resistance                 | Enabled, A <sub>V</sub> = +1                                                            |                         |                    | 0.2                |                    | Ω    |

| R <sub>O</sub> _Disabled | Output Resistance                 | Shutdown                                                                                |                         |                    | >100               |                    | МΩ   |

| C <sub>O</sub> _Disabled | Output Capacitance                | Shutdown                                                                                |                         |                    | 5.6                |                    | pF   |

| MISCELLANE               | OUS PERFORMANCE                   |                                                                                         |                         |                    |                    |                    |      |

| VDMAX                    | Voltage Limit for Disable (Pin 5) | See (5) (At tempera                                                                     | ature extremes)         | 0                  |                    | 0.27               | V    |

| VDMIN                    | Voltage Limit for Enable (Pin 5)  | See <sup>(5)</sup> (At temperature extremes)                                            |                         | 2.43               |                    | 2.7                | V    |

| l <sub>i</sub>           | Logic Input Current (Pin 5)       | <del>SD</del> = 2.7 V <sup>(5)</sup>                                                    |                         |                    | 4                  |                    | рА   |

| V_glitch                 | Turnon Glitch                     |                                                                                         |                         |                    | 1.2                |                    | V    |

| Isolation <sub>OFF</sub> | Off Isolation                     | 1 MHz, $R_L = 1 k\Omega$                                                                |                         |                    | 60                 |                    | dB   |

<sup>(6) &</sup>quot;V<sub>ID</sub>" is input differential voltage (input overdrive).

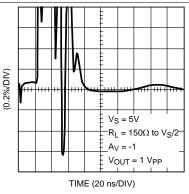

## 6.9 Switching Characteristics, 5 V

Single-Supply with VS= 5 V, AV = +2, RF = 604  $\Omega$ , SD tied to V+, VOUT = VS/2, RL = 150  $\Omega$  to V- unless otherwise specified.

|                  | PARAMETER          | TEST CONDITIONS                   | MIN | TYP | MAX | UNIT |  |

|------------------|--------------------|-----------------------------------|-----|-----|-----|------|--|

| TIME DON         | AIN RESPONSE       |                                   |     |     |     |      |  |

| TRS/TRL          | Rise and Fall Time | 0.25-V Step                       |     | 2.6 |     | ns   |  |

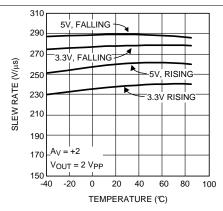

| SR               | Slew Rate          | 2-V Step                          |     | 275 |     | V/µs |  |

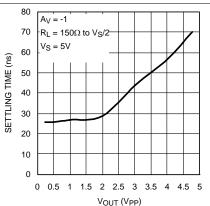

| T <sub>S</sub>   | Settling Time      | 1-V Step, ±0.1%                   |     | 50  |     | ns   |  |

| T <sub>S_1</sub> | Settling Time      | 1-V Step, ±0.02%                  |     | 220 |     |      |  |

| PD               | Propagation Delay  | Input to Output, 250-mV Step, 50% |     | 2.4 |     | ns   |  |

| MISCELLA         | NEOUS PERFORMANCE  |                                   |     |     |     |      |  |

| T <sub>on</sub>  | Turnon Time        |                                   |     | 1.4 |     | μs   |  |

| T <sub>off</sub> | Turnoff Time       |                                   |     | 520 |     | ns   |  |

| T_OL             | Overload Recovery  |                                   |     | <20 |     | ns   |  |

Submit Documentation Feedback

Copyright © 2006–2015, Texas Instruments Incorporated

#### 6.10 Switching Characteristics, 3.3 V

Single-Supply with  $V_S = 3.3 \text{ V}$ ,  $A_V = +2$ ,  $R_F = 604\Omega$ ,  $\overline{SD}$  tied to  $V^+$ ,  $V_{OUT} = V_S/2$ ,  $R_L = 150 \Omega$  to  $V^-$  unless otherwise specified. (1)

|                  | PARAMETER          | TEST CONDITIONS                   | MIN | TYP | MAX | UNIT |  |

|------------------|--------------------|-----------------------------------|-----|-----|-----|------|--|

| TIME DOM         | AIN RESPONSE       |                                   |     |     |     |      |  |

| TRS/TRL          | Rise and Fall Time | 0.25-V Step                       |     | 2.7 |     | ns   |  |

| SR               | Slew Rate          | 2-V Step                          |     | 260 |     | V/µs |  |

| T <sub>S</sub>   | Codding Times      | 1-V Step, ±0.1%                   |     | 70  |     |      |  |

| T <sub>S_1</sub> | Settling Time      | 1-V Step, ±0.02%                  |     | 300 |     | ns   |  |

| PD               | Propagation Delay  | Input to Output, 250-mV Step, 50% |     | 2.6 |     | ns   |  |

| MISCELLA         | NEOUS PERFORMANCE  |                                   |     |     | ·   |      |  |

| T <sub>on</sub>  | Turnon Time        |                                   |     | 3.5 |     | μs   |  |

| T <sub>off</sub> | Turnoff Time       |                                   |     | 500 |     | ns   |  |

<sup>(1)</sup> Electrical Characteristics, 3.3 V values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that T<sub>J</sub> = T<sub>A</sub>. No specification of parametric performance is indicated in the electrical tables under conditions of internal self-heating where T<sub>J</sub> > T<sub>A</sub>.

## 6.11 Switching Characteristics, 2.7 V

Single-Supply with  $V_S = 2.7 \text{ V}$ ,  $A_V = +2$ ,  $R_F = 604 \Omega$ ,  $\overline{SD}$  tied to  $V^+$ ,  $V_{OUT} = V_S/2$ ,  $R_L = 150 \Omega$  to  $V^-$  unless otherwise specified. (1)

| орсспіса.        |                    |                                   |     |     |     |      |  |

|------------------|--------------------|-----------------------------------|-----|-----|-----|------|--|

|                  | PARAMETER          | TEST CONDITIONS                   | MIN | TYP | MAX | UNIT |  |

| TIME DON         | IAIN RESPONSE      |                                   |     |     | ·   |      |  |

| TRS/TRL          | Rise and Fall Time | 0.25-V Step                       |     | 2.7 |     | ns   |  |

| SR               | Slew Rate          | 2-V Step                          |     | 260 |     | V/µs |  |

| T <sub>S</sub>   | Couling at Time o  | 1-V Step, ±0.1%                   |     | 147 |     |      |  |

| T <sub>S_1</sub> | Settling Time      | 1-V Step, ±0.02%                  |     | 410 |     | ns   |  |

| PD               | Propagation Delay  | Input to Output, 250-mV Step, 50% |     | 3.4 |     | ns   |  |

| MISCELLA         | ANEOUS PERFORMANCE |                                   |     |     |     |      |  |

| T <sub>on</sub>  | Turnon Time        |                                   |     | 5.2 |     | μs   |  |

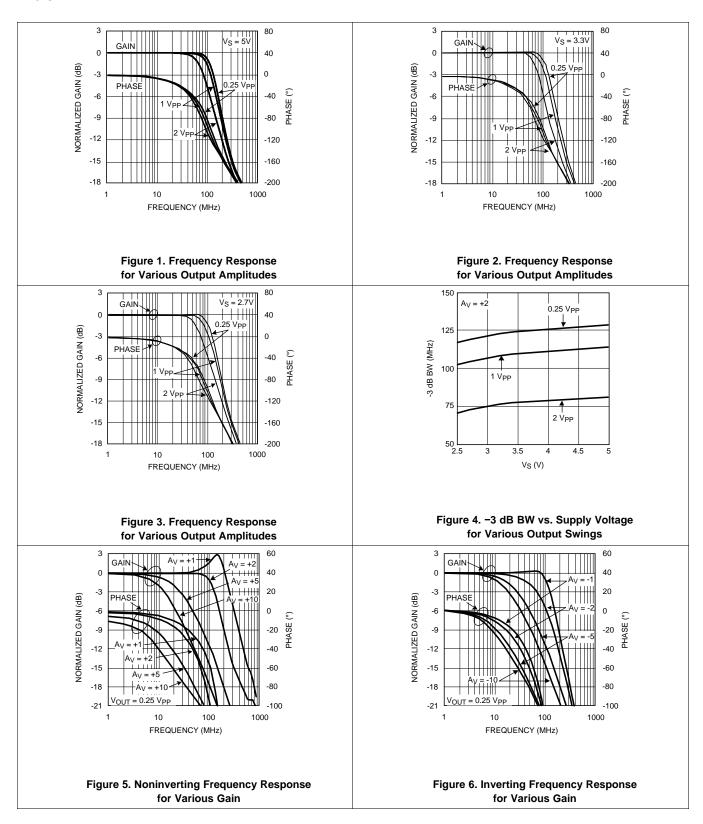

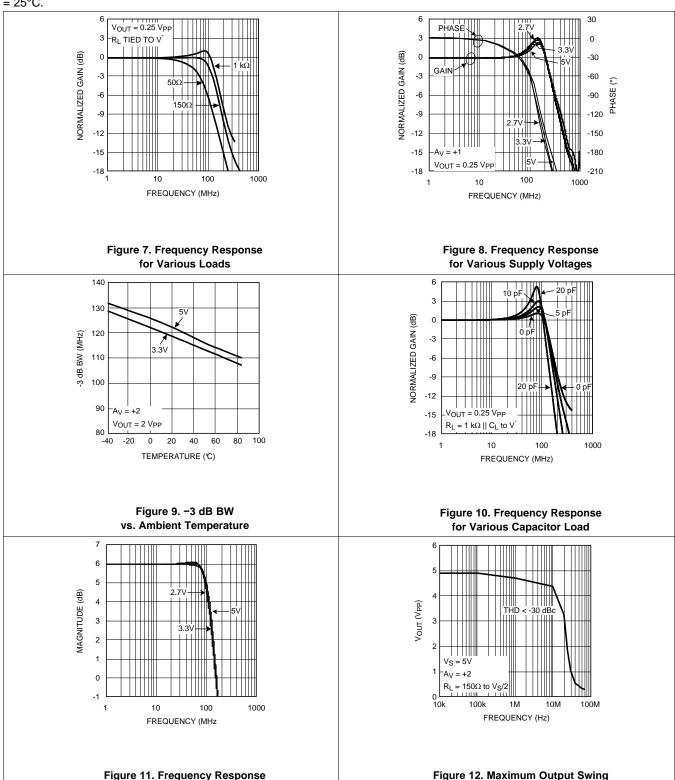

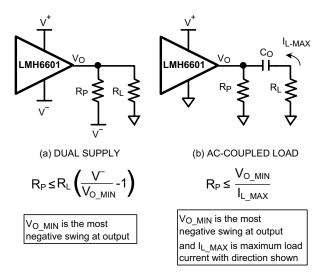

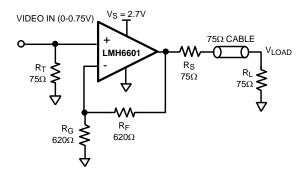

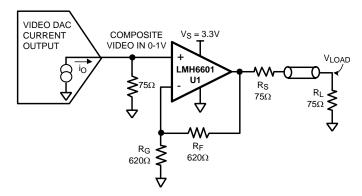

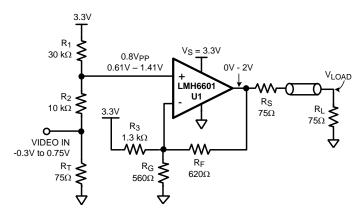

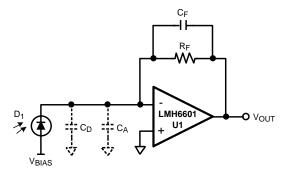

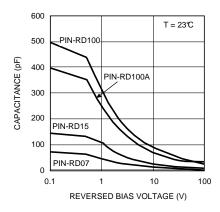

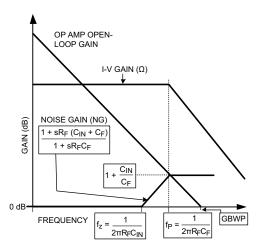

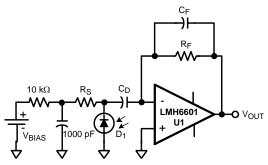

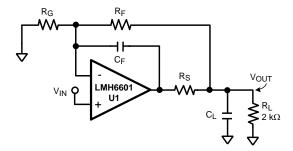

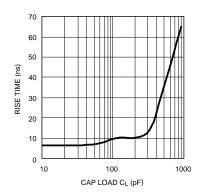

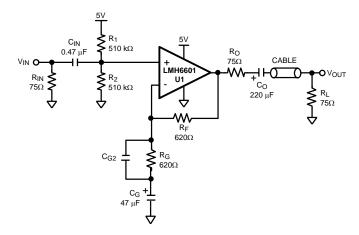

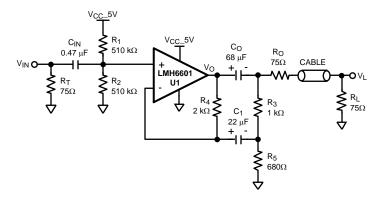

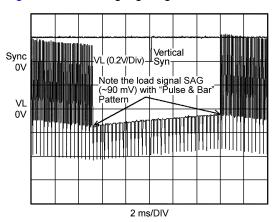

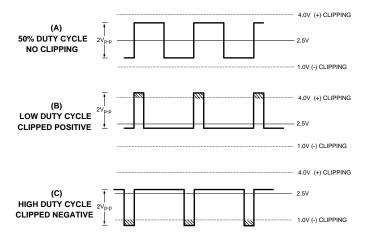

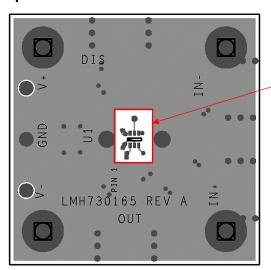

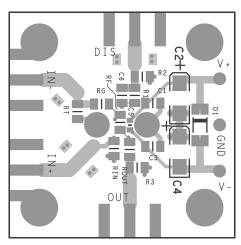

| T <sub>off</sub> | Turnoff Time       |                                   |     | 760 |     | ns   |  |