# 16-BIT, 2-MSPS, LVDS SERIAL INTERFACE, SAR ANALOG-TO-DIGITAL CONVERTER

# FEATURES

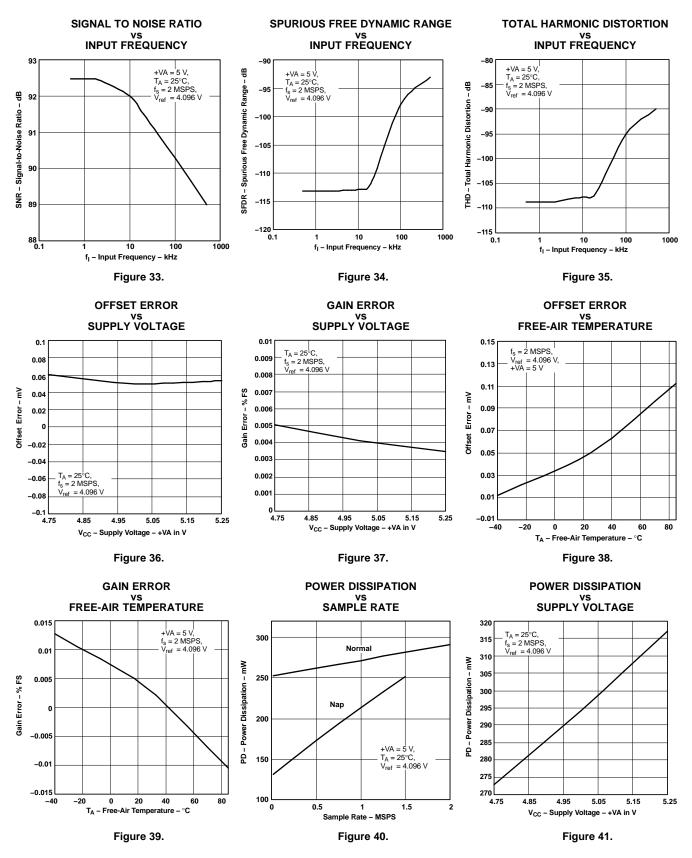

- 2-MHz Sample Rate

- 16-Bit Resolution

- SNR 92 dB at 10 kHz I/P

- THD –107 dB at 10 kHz I/P

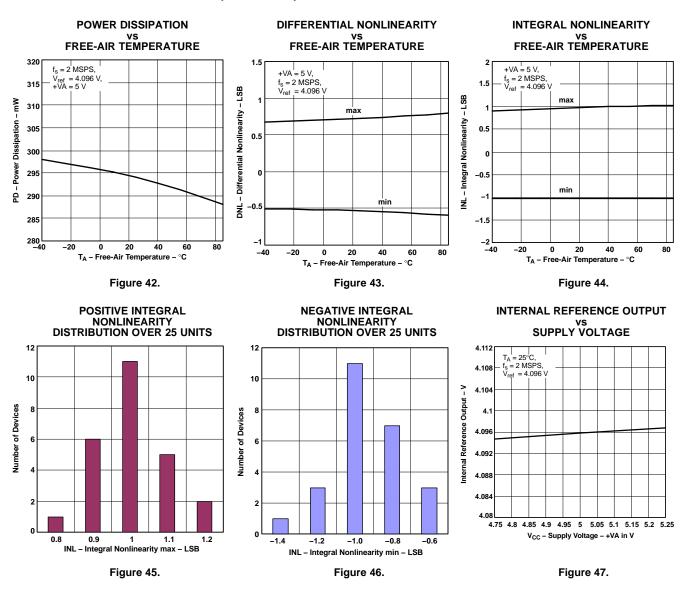

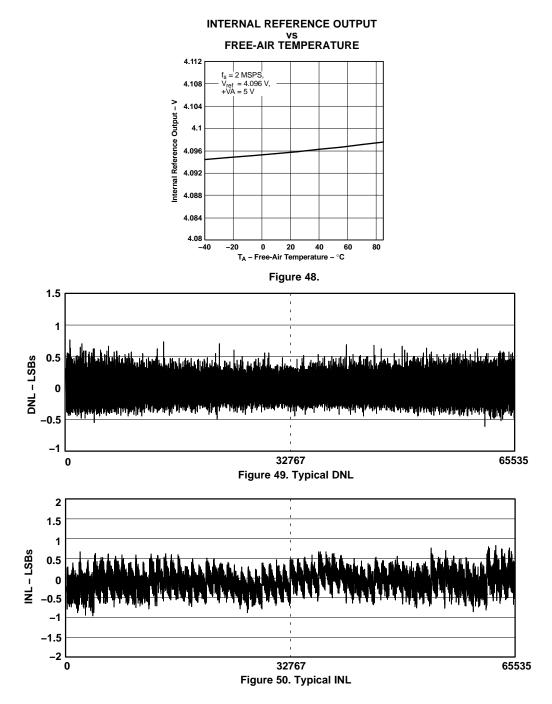

- ±1 LSB Typ, ±2 LSB INL Max

- +0.7/-0.5 LSB Typ, +1.5/-1 LSB DNL Max

- Unipolar Differential Input Range: -4 V to 4 V

- Internal Reference

- Internal Reference Buffer

- 200-Mbps LVDS Serial Interface

- Optional 200-MHz Internal Interface Clock

- 16-/8-Bit Data Frame

- Zero Latency at Full Speed

- Power Dissipation: 290 mW at 2 MSPS

- Nap Mode (125 mW Power Dissipation)

- Power Down (5 μW)

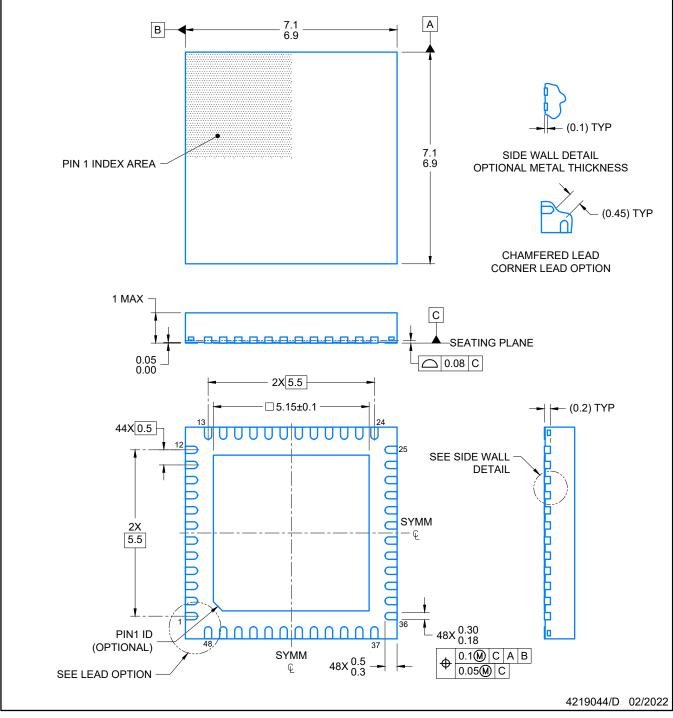

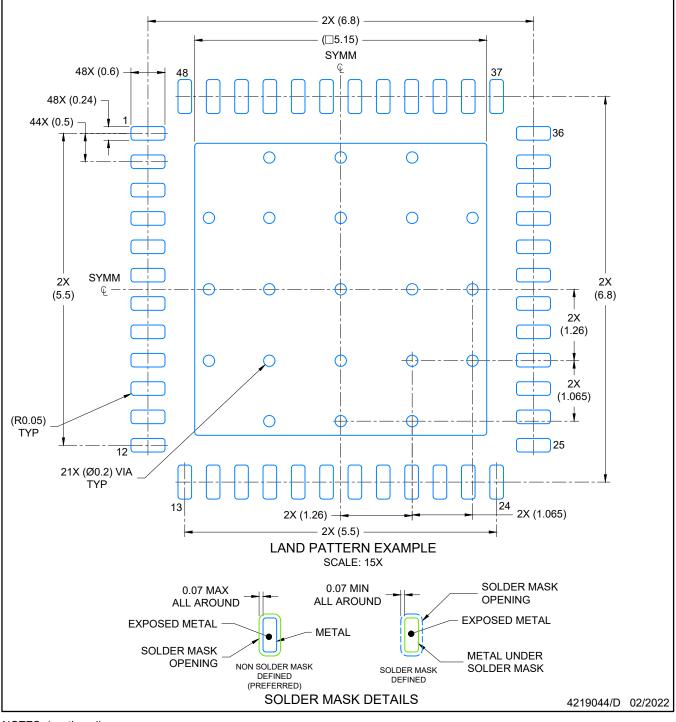

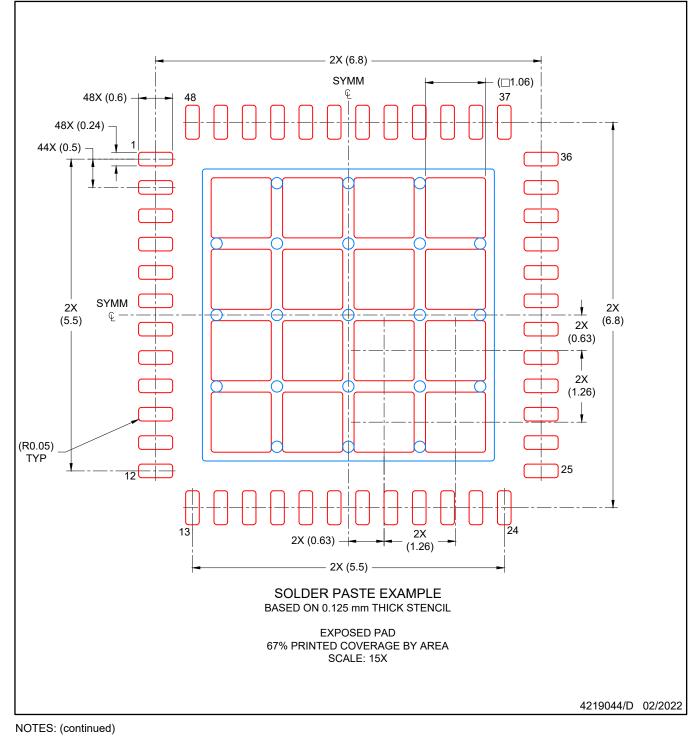

- 48-Pin QFN Package

# APPLICATIONS

- Medical Instrumentation

- High-Speed Data Acquisiton Systems

- High-Speed Close-Loop Systems

- Communication

# DESCRIPTION

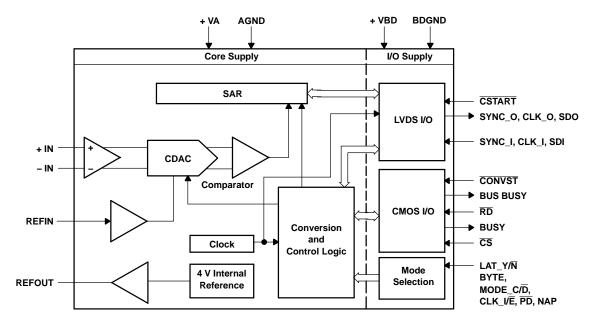

The ADS8413 is a 16-bit, 2-MSPS, analog-to-digital (A/D) converter with 4-V internal reference. The device includes a capacitor based SAR A/D converter with inherent sample and hold.

The ADS8413 also includes a 200-Mbps, LVDS, serial interface. This interface is designed to support daisy chaining or cascading of multiple devices. A selectable 16-/8-bit data frame mode enables the use of a single shift register chip (SN65LVDS152) for converting the data to parallel format.

The ADS8413 unipolar differential input range supports a differential input swing of  $-V_{ref}$  to  $+V_{ref}$  with a common-mode voltage of  $+V_{ref}/2$ .

The nap feature provides substantial power saving when used at lower conversion rates.

The ADS8413 is available in a 48-pin QFN package.

| Type/Speed                        | 500 kHz | ~ 600 kHz   | 750 kHZ | 1 MHz | 1.25 MHz    | 2 MHz               | 3 MHz   | 4 MHz   |

|-----------------------------------|---------|-------------|---------|-------|-------------|---------------------|---------|---------|

| 18-Bit Pseudo-Diff                | ADS8383 | ADS8381     |         |       |             |                     |         |         |

| IO-DIL PSEUDO-DIII                |         | ADS8380 (S) |         |       |             |                     |         |         |

| 18-Bit Pseudo-Bipolar, Fully Diff |         | ADS8382 (S) |         |       |             |                     |         |         |

|                                   |         |             |         |       |             | ADS8411             |         |         |

| 16-Bit Pseudo-Diff                |         | ADS8370 (S) | ADS8371 |       | ADS8401/05  | ADS8410<br>(S-LVDS) |         |         |

|                                   |         |             |         |       |             | ADS8412             |         |         |

| 16-Bit Pseudo-Bipolar, Fully Diff |         | ADS8372 (S) |         |       | ADS8402/06  | ADS8413<br>(S-LVDS) |         |         |

| 14-Bit Pseudo-Diff                |         |             |         |       | ADS7890 (S) |                     | ADS7891 |         |

| 12-Bit Pseudo-Diff                |         |             |         |       |             |                     |         | ADS7881 |

# High-Speed SAR Converter Family

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### ORDERING INFORMATION<sup>(1)</sup>

| MODEL     | MAXIMUM<br>INTEGRAL<br>LINEARITY<br>(LSB) | MAXIMUM<br>DIFFERENTIAL<br>LINEARITY<br>(LSB) | NO MISSING<br>CODES AT<br>RESOLUTION<br>(BIT) | PACKAGE<br>TYPE | PACKAGE<br>DESIGNATOR | TEMPERATURE<br>RANGE | ORDERING<br>INFORMATION | TRANSPORT<br>MEDIA<br>QUANTITY |

|-----------|-------------------------------------------|-----------------------------------------------|-----------------------------------------------|-----------------|-----------------------|----------------------|-------------------------|--------------------------------|

| ADS8413IB | +2                                        | 1.5/-1                                        | 16                                            | 48 pin          | RGZ                   | -40°C                | ADS8413IBRGZT           | 250                            |

| AD304131D | 12                                        | 1.5/-1                                        | 10                                            | QFN             | ROZ                   | to 85°C              | ADS8413IBRGZR           | 2000                           |

| ADS8413I  | ±4                                        | 3/-1                                          | 16                                            | 48 pin          | RGZ                   | -40°C                | ADS8413IRGZT            | 250                            |

| AD304131  | 4                                         | 3/-1                                          | 10                                            | QFN             | NGZ                   | to 85°C              | ADS8413IRGZR            | 2000                           |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

# **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                           |                                 | UNIT                           |  |  |

|-------------------------------------------|---------------------------------|--------------------------------|--|--|

| +IN to AGND                               | –0.3 V to +VA + 0.3 V           |                                |  |  |

| -IN to AGND                               | –0.3 V to +VA + 0.3 V           |                                |  |  |

| +VA to AGND                               |                                 | –0.3 to 7 V                    |  |  |

| +VBD to BDGND                             |                                 | –0.3 to 7 V                    |  |  |

| Digital input voltage to GND              |                                 | -0.3 V to (+VBD + 0.3 V)       |  |  |

| Digital output to GND                     |                                 | -0.3 V to (+VBD + 0.3 V        |  |  |

| Operating temperature range               |                                 | –40°C to 85°C                  |  |  |

| Storage temperature range                 |                                 | –65°C to 150°C                 |  |  |

| Junction temperature (T <sub>J</sub> max) |                                 | 150°C                          |  |  |

|                                           | Power dissipation               | $(T_J Max - T_A)/ \theta_{JA}$ |  |  |

| QFN package                               | $\theta_{JA}$ Thermal impedance | 86°C/W                         |  |  |

| l and towns ratives coldering             | Vapor phase (60 sec)            | 215°C                          |  |  |

| Lead temperature, soldering               | Infrared (15 sec)               | 220°C                          |  |  |

(1) Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# **SPECIFICATIONS**

$T_A = -40^{\circ}C$  to  $85^{\circ}C$ , +VA = 5 V,+VBD = 5 V or 3.3 V,  $V_{ref} = 4.096$  V, f <sub>sample</sub> = 2 MHz (unless otherwise noted)

|                           | PARAMETER                                |                                                                                               | TEST CONDITIONS                                                         | MIN                     | TYP                 | MAX                     | UNIT               |  |

|---------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------|---------------------|-------------------------|--------------------|--|

| ANALOG                    | INPUT                                    |                                                                                               | 1                                                                       |                         |                     |                         |                    |  |

|                           | Full-scale input voltage span            | (1)                                                                                           | +IN - (-IN)                                                             | -V <sub>ref</sub>       |                     | V <sub>ref</sub>        | V                  |  |

|                           | Absolute input voltage range             |                                                                                               | +IN                                                                     | -0.2                    |                     | V <sub>ref</sub> + 0.2  | V                  |  |

|                           | Absolute input voltage range             |                                                                                               | -IN                                                                     | -0.2                    |                     | V <sub>ref</sub> + 0.2  | v                  |  |

|                           | Input common-mode voltage                | range                                                                                         |                                                                         | V <sub>ref</sub> /2-0.2 | V <sub>ref</sub> /2 | V <sub>ref</sub> /2+0.2 | V                  |  |

| Ci                        | Input capacitance                        |                                                                                               |                                                                         |                         | 25                  |                         | pF                 |  |

|                           | Input leakage current                    |                                                                                               |                                                                         |                         | 500                 |                         | pА                 |  |

| SYSTEM F                  | PERFORMANCE                              |                                                                                               |                                                                         |                         |                     | ·                       |                    |  |

|                           | Resolution                               |                                                                                               |                                                                         |                         | 16                  |                         | Bits               |  |

|                           | No mining and a                          | ADS8413IB                                                                                     |                                                                         | 16                      |                     |                         | Dite               |  |

|                           | No missing codes                         | ADS8413I                                                                                      |                                                                         | 16                      |                     |                         | Bits               |  |

|                           |                                          | ADS8413IB                                                                                     |                                                                         | -2                      | ±1                  | 2                       |                    |  |

| INL                       | Integral linearity <sup>(2)</sup>        | ADS8413I                                                                                      | -                                                                       | -4.0                    | ±2                  | 4.0                     | LSB <sup>(3)</sup> |  |

|                           |                                          | ADS8413IB                                                                                     |                                                                         | -1                      | 0.7/-0.5            | 1.5                     | 1.00.00            |  |

| DNL                       | Differential linearity                   | ADS8413I                                                                                      | 1                                                                       | -1.0                    | 1.5/-0.8            | 3                       | LSB <sup>(3)</sup> |  |

|                           |                                          | ADS8413IB                                                                                     |                                                                         | -1                      | ±0.2                | 1                       |                    |  |

| Eo                        | Offset error                             | ADS8413I                                                                                      | External reference                                                      | -3.0                    | ±1                  | 3.0                     | mV                 |  |

|                           |                                          | ADS8413IB                                                                                     |                                                                         | -0.1                    | ±0.03               | 0.1                     |                    |  |

| E <sub>G</sub>            | Gain error <sup>(4)</sup>                | ADS8413I                                                                                      | External reference                                                      | -0.15                   | ±0.1                | 0.15                    | % of F             |  |

| CMMR                      | Common-mode rejection ratio              |                                                                                               | With common mode input signal = 200 mV <sub>p-p</sub> at 1 MHz          |                         | 60                  |                         | dB                 |  |

| PSRR                      | Power supply rejection ratio             |                                                                                               | At FFF0 <sub>H</sub> output code                                        |                         | 80                  |                         | dB                 |  |

| SAMPLIN                   | G DYNAMICS                               |                                                                                               |                                                                         |                         |                     |                         |                    |  |

|                           |                                          |                                                                                               | +VBD = 5 V                                                              |                         | 360                 | 391                     |                    |  |

|                           | Conversion time                          |                                                                                               | +VBD = 3 V                                                              |                         |                     | 391                     | ns                 |  |

|                           |                                          |                                                                                               | +VBD = 5 V                                                              | 100                     |                     |                         |                    |  |

|                           | Acquisition time                         |                                                                                               | +VBD = 3 V                                                              | 100                     |                     |                         | ns                 |  |

|                           | Maximum throughput rate with             | h or without latency                                                                          |                                                                         |                         |                     | 2.0                     | MHz                |  |

|                           | Aperture delay                           |                                                                                               |                                                                         |                         | 20                  |                         | ns                 |  |

|                           | Aperture jitter                          |                                                                                               |                                                                         |                         | 10                  |                         | psec               |  |

|                           | Step response                            |                                                                                               |                                                                         |                         | 50                  |                         | ns                 |  |

|                           | Overvoltage recovery                     |                                                                                               |                                                                         |                         | 50                  |                         | ns                 |  |

| DYNAMIC                   | CHARACTERISTICS                          |                                                                                               |                                                                         |                         |                     |                         |                    |  |

|                           |                                          |                                                                                               | V <sub>IN</sub> 0.5 dB below FS at 10 kHz                               |                         | -107                |                         |                    |  |

| THD                       | Total harmonic distortion <sup>(5)</sup> |                                                                                               | V <sub>IN</sub> 0.5 dB below FS at 100 kHz                              |                         | -95                 |                         | dB                 |  |

|                           |                                          |                                                                                               | $V_{IN}$ 0.5 dB below FS at 0.5 MHz                                     |                         | -90                 |                         |                    |  |

|                           |                                          |                                                                                               | V <sub>IN</sub> 0.5 dB below FS at 10 kHz                               |                         | 92                  |                         |                    |  |

| SNR Signal-to-noise ratio |                                          | $V_{IN}$ 0.5 dB below FS at 100 kHz                                                           |                                                                         | 90                      |                     | dB                      |                    |  |

|                           |                                          | VIN 0.5 dB below FS at 0.5 MHz         90           VIN 0.5 dB below FS at 0.5 MHz         89 |                                                                         |                         | üÐ                  |                         |                    |  |

|                           |                                          |                                                                                               | $V_{IN}$ 0.5 dB below FS at 10 kHz                                      |                         | 92                  |                         |                    |  |

| SINAD                     | AD Signal-to-noise and distortion        |                                                                                               | $V_{IN}$ 0.5 dB below FS at 10 kHz                                      |                         | 86                  |                         | ᅯᄆ                 |  |

| SINAD                     |                                          |                                                                                               |                                                                         |                         |                     |                         | dB                 |  |

|                           |                                          |                                                                                               | V <sub>IN</sub> 0.5 dB below FS at 0.5 MHz                              |                         | 84                  |                         |                    |  |

|                           | Onuminum francuis                        |                                                                                               | V <sub>IN</sub> 0.5 dB below FS at 10 kHz                               |                         | -113                |                         | 15                 |  |

| SFDR                      | Spurious free dynamic range              |                                                                                               | $V_{IN}$ 0.5 dB below FS at 100 kHz $V_{IN}$ 0.5 dB below FS at 0.5 MHz |                         | -98                 |                         | dB                 |  |

| N                         |                                          |                                                                                               |                                                                         | -93                     |                     |                         |                    |  |

Ideal input span; does not include gain or offset error.

This is endpoint INL, not best fit.

Least significant bit

(4) (5) Measured relative to actual measured reference.

Calculated on the first nine harmonics of the input frequency.

# **SPECIFICATIONS (continued)**

$T_A = -40^{\circ}C$  to  $85^{\circ}C$ , +VA = 5 V,+VBD = 5 V or 3.3 V,  $V_{ref} = 4.096$  V, f <sub>sample</sub> = 2 MHz (unless otherwise noted)

|                       | PARAMETER                                                                         |          | TEST CONDITIONS                                               | MIN        | TYP   | MAX       | UNIT    |

|-----------------------|-----------------------------------------------------------------------------------|----------|---------------------------------------------------------------|------------|-------|-----------|---------|

| EXTERNAL              | REFERENCE INPUT                                                                   |          |                                                               |            |       |           |         |

|                       | Input voltage range, V <sub>REF</sub>                                             |          |                                                               | 3.9        | 4.096 | 4.2       | V       |

|                       | Resistance <sup>(6)</sup>                                                         |          | To internal reference voltage                                 |            | 500   |           | kΩ      |

| INTERNAL I            | REFERENCE OUTPUT                                                                  |          |                                                               |            |       |           |         |

|                       | Start-up time                                                                     |          | From 95% (+VA), with 1-µF storage capacitor on REFOUT to AGND |            |       | 25        | ms      |

|                       | Reference voltage range, $V_{ref}$                                                |          | At room temperature                                           | 4.080      | 4.096 | 4.112     | V       |

|                       | Source current                                                                    |          | Static load                                                   |            |       | 10        | μA      |

|                       | Line regulation                                                                   |          | +VA = 4.75 V to 5.25 V                                        |            | 0.6   |           | mV      |

|                       | Drift                                                                             |          | IOUT = 0 V                                                    |            | 36    |           | PPM/°C  |

| POWER SU              | PPLY REQUIREMENTS                                                                 |          |                                                               |            |       |           |         |

|                       | Device events wells an                                                            | +VBD     |                                                               | 2.7        | 3.3   | 5.25      |         |

|                       | Power supply voltage                                                              | +VA      |                                                               | 4.75       | 5     | 5.25      | V       |

|                       | Supply current, 2-MHz sample rate                                                 | +VA      |                                                               |            | 58    | 64        | mA      |

|                       | Power dissipation, 2-MHz sample ra                                                | ate      | +VA = 5 V                                                     |            | 290   | 320       | mW      |

| NAP MODE              |                                                                                   |          | -                                                             | 1          |       |           |         |

|                       | Supply current                                                                    | +VA      |                                                               |            | 25    |           | mA      |

| POWER DO              | WN                                                                                |          |                                                               | I          |       |           |         |

|                       | Supply current                                                                    | +VA      |                                                               |            | 1     | 2.5       | μA      |

|                       | Powerdown time                                                                    |          |                                                               |            | 10    |           | μs      |

|                       | Powerup time                                                                      |          | With 1-µF storage capacitor on<br>REFOUT to AGND              |            | 25    |           | ms      |

|                       | Invalid conversions after power up of                                             | or reset |                                                               |            | 3     |           | Numbers |

| TEMPERAT              | URE RANGE                                                                         |          | I                                                             | 4          |       |           |         |

|                       | Operating free air                                                                |          |                                                               | -40        |       | 85        | °C      |

| LOGIC FAM             | ILY CMOS                                                                          |          | I                                                             | 4          |       |           |         |

| V <sub>IH</sub>       | High-level input voltage                                                          |          | I <sub>IH</sub> = 5 μA                                        | +VBD -1    |       | +VBD +0.3 | V       |

| V <sub>IL</sub>       | Low-level input voltage                                                           |          | I <sub>IL</sub> = 5 μA                                        | -0.3       |       | 0.8       | V       |

| V <sub>OH</sub>       | High-level output voltage                                                         |          | I <sub>OH</sub> = 2 TTL loads                                 | +VBD - 0.6 |       | +VBD      | V       |

| V <sub>OL</sub>       | Low-level output voltage                                                          |          | I <sub>OL</sub> = 2 TTL loads                                 | 0          |       | 0.4       | V       |

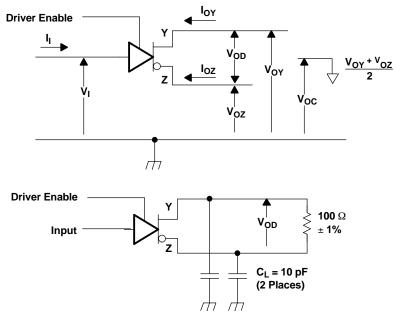

|                       | ILY LVDS <sup>(7)</sup>                                                           |          | r.                                                            | <u></u>    |       |           |         |

| DRIVER                |                                                                                   |          |                                                               |            |       |           |         |

| V <sub>OD(SS)</sub>   | Steady-state differential output volta magnitude                                  | ige      |                                                               | 247        | 340   | 454       |         |

| $\Delta  V_{OD(SS)} $ | Change in steady-state differential output voltage magnitude between logic states |          | $R_L = 100 \Omega$ , See Figure 52, Figure 53                 | -50        |       | 50        | mV      |

| V <sub>OC(SS)</sub>   | Steady-state common-mode output voltage                                           |          |                                                               | 1.125      | 1.2   | 1.375     | V       |

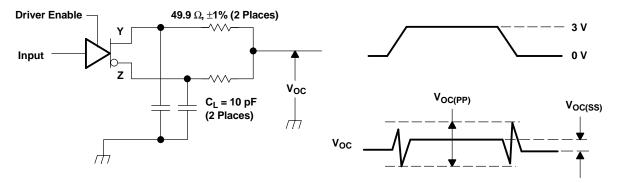

| Δ V <sub>OC(SS)</sub> | Change in steady-state common-mode output<br>voltage between logic states         |          | See Figure 54                                                 | -50        |       | 50        |         |

| V <sub>OC(pp)</sub>   | Peak to peak change in common-mode output voltage                                 |          | +                                                             |            | 50    | 150       | mV      |

|                       |                                                                                   |          | $V_{OY}$ or $V_{OZ} = 0 V$                                    |            | 3     | 10        |         |

| I <sub>OS</sub>       | Short circuit output current                                                      |          | V <sub>OD</sub> = 0 V                                         |            | 3     | 10        | mA      |

| I <sub>oz</sub>       | High impedance output current                                                     |          | VO = 0 V or +VBD                                              | -5         |       | 5         | μA      |

(6) Can vary ±20%

(7) All min max values ensured by design.

# **SPECIFICATIONS (continued)**

$T_A = -40^{\circ}C$  to  $85^{\circ}C$ , +VA = 5 V,+VBD = 5 V or 3.3 V,  $V_{ref} = 4.096$  V, f <sub>sample</sub> = 2 MHz (unless otherwise noted)

|                   | PARAMETER                                     | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-------------------|-----------------------------------------------|-----------------|-----|-----|-----|------|

| RECEIVE           | R                                             |                 |     |     |     |      |

| V <sub>ITH+</sub> | Positive going differential voltage threshold |                 |     |     | 50  | mV   |

| V <sub>ITH-</sub> | Negative going differential voltage threshold |                 | -50 |     |     | IIIV |

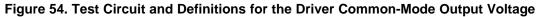

| VIC               | Common mode input voltage                     |                 | 0.2 | 1.2 | 2.2 | V    |

| CI                | Input capacitance                             |                 |     | 5   |     | pF   |

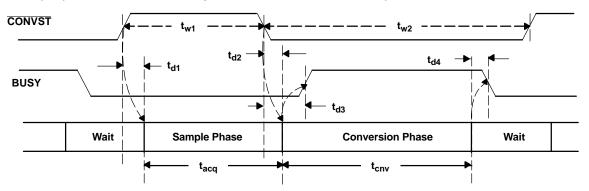

## TIMING REQUIREMENTS

$\rm T_{A}$  = -40°C to 85°C, +VA = 5 V, +VBD = 5 V or 3.3 V (unless otherwise noted)

|                  | PARAMETER                                                                           |                            | MIN                                                | TYP MAX                                            | UNIT                              | REF                               |

|------------------|-------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------|----------------------------------------------------|-----------------------------------|-----------------------------------|

| SAM              | PLING AND CONVERSION RELATED                                                        |                            |                                                    |                                                    |                                   |                                   |

| t <sub>acq</sub> | Acquisition time                                                                    |                            | 100                                                |                                                    | ns                                | Figure 1,<br>Figure 2             |

| t <sub>cnv</sub> | Conversion time                                                                     |                            | 391                                                | ns                                                 | Figure 1,<br>Figure 2             |                                   |

| t <sub>w1</sub>  | Pulse duration, CONVST high                                                         |                            | 100                                                |                                                    | ns                                | Figure 1                          |

| t <sub>w2</sub>  | Pulse duration, CONVST low                                                          |                            | 40                                                 |                                                    | ns                                | Figure 1,<br>Figure 2             |

| d1               | Delay time, CONVST rising edge to sample start                                      |                            |                                                    | 5                                                  | ns                                | Figure 1                          |

| t <sub>d2</sub>  | Delay time, CONVST falling edge to conversion start                                 |                            |                                                    | 5                                                  | ns                                | Figure 1,<br>Figure 2             |

| d3               | Delay time, CONVST falling edge to busy high                                        | +VBD = 3.3 V               |                                                    | 14                                                 | ns                                | Figure 1,                         |

| d3               |                                                                                     | +VBD = 5 V                 |                                                    | 13                                                 | 113                               | Figure 2                          |

| t <sub>d4</sub>  | Delay time, conversion end to busy low                                              | +VBD = 3.3 V               |                                                    | 8                                                  | ns                                | Figure 1,<br>Figure 2             |

| <u></u>          |                                                                                     | +VBD = 5 V                 |                                                    | 7                                                  | _                                 |                                   |

| t <sub>w3</sub>  | Pulse duration, CSTART high                                                         |                            | 100                                                |                                                    | ns                                | Figure 1,<br>Table 2              |

| w4               | Pulse duration, CSTART low                                                          | 45                         |                                                    | ns                                                 | Figure 1,<br>Figure 2,<br>Table 2 |                                   |

| d5               | Delay time, CSTART rising edge to sample start                                      |                            |                                                    | 7.5                                                | ns                                | Figure 1,<br>Table 2              |

| t <sub>d6</sub>  | Delay time, CSTART falling edge to conversion start                                 |                            |                                                    | 7.5                                                | ns                                | Figure 1,<br>Figure 2,<br>Table 2 |

| t <sub>d7</sub>  | Delay time, CSTART falling edge to busy high                                        | +VBD = 3.3 V<br>+VBD = 5 V |                                                    | 16.5<br>15.5                                       | ns                                | Figure 1,<br>Figure 2,<br>Table 2 |

| /0 R             | RELATED                                                                             |                            |                                                    |                                                    |                                   | 14510 2                           |

| d8               | Delay time, $\overline{RD}$ falling edge while $\overline{CS}$ low to BUS_BUSY high |                            |                                                    | 16                                                 | ns                                | Figure 5                          |

|                  | Delay time, RD falling edge while CS low to SYNC_O and SDO out of                   | +VBD = 3.3 V               |                                                    | 29                                                 |                                   |                                   |

| d9               | 3-state condition (for device with LAT_Y/N pulled low)                              | +VBD = 5 V                 |                                                    | 28                                                 | ns                                | Figure 5                          |

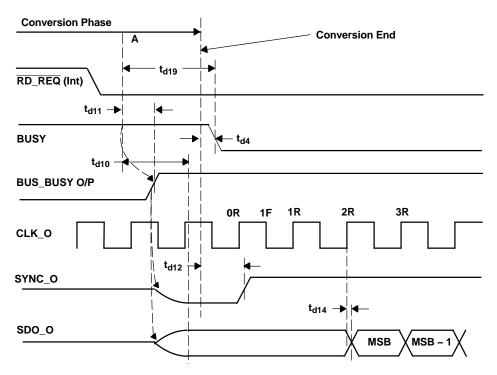

| d10              | Delay time, pre_conversion end (point A) to SYNC_O and SDO out of 3 condition       | 3-state                    |                                                    | 22                                                 | ns                                | Figure 6                          |

|                  | Delay time, pre_conversion end (point A) to BUS_BUSY high                           | VBD = 3.3 V                |                                                    | 8                                                  | ns                                | Figure 6                          |

| d11              |                                                                                     | +VBD = 5 V                 |                                                    | 7                                                  | 115                               | r igule o                         |

| d12              | Delay time, conversion phase end to SYNC_O high                                     |                            | 6                                                  | $9 + t_{CLK}$                                      | ns                                | Figure 6                          |

| d13              | Delay time, $\overline{RD}$ falling edge while $\overline{CS}$ low to SYNC_O high   | +VBD = 3.3 V<br>+VBD = 5 V | 5.5 + 4*t <sub>CLK</sub><br>5 + 4*t <sub>CLK</sub> | 8.5 + 5*t <sub>CLK</sub><br>8 + 5*t <sub>CLK</sub> | ns                                | Figure 5                          |

| w5               | Pulse duration, RD low for device in no latency mode                                |                            | 5                                                  | OLK                                                | ns                                | Figure 11                         |

|                  |                                                                                     | +VBD = 3.3 V               |                                                    | 1.4                                                |                                   | Figure 5,                         |

| d14              | Delay time, CLK_O rising edge to data valid                                         | +VBD = 5 V                 |                                                    | 1.3                                                | ns                                | Figure 6                          |

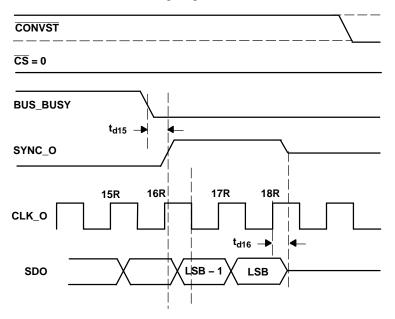

| t <sub>d15</sub> | Delay time, BUS_BUSY low to SYNC_O high in daisy chain mode                         | +VBD = 3.3 V               | 4*t <sub>CLK</sub> - 6.5                           | 4*t <sub>CLK</sub> - 3                             | ns                                | Figure 7,                         |

| -010             | indicating receiving device to output the data                                      | +VBD = 5 V                 | 4*t <sub>CLK</sub> – 6                             | 4*t <sub>CLK</sub> – 2.5                           |                                   | Figure 12                         |

# TIMING REQUIREMENTS (continued)

$T_{\rm A}$  = -40°C to 85°C, +VA = 5 V, +VBD = 5 V or 3.3 V (unless otherwise noted)

|                  | PARAMETER                                                                |                 | MIN | TYP | MAX                       | UNIT                                              | REF                     |

|------------------|--------------------------------------------------------------------------|-----------------|-----|-----|---------------------------|---------------------------------------------------|-------------------------|

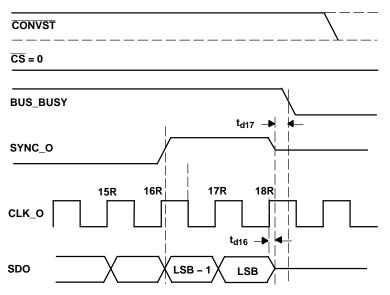

| t <sub>d16</sub> | Delay time, CLK_O to SDO and SYNC_O 3-state                              |                 |     | 4   | ns                        | Figure 7,<br>Figure 8,<br>Figure 12,<br>Figure 15 |                         |

| t <sub>pd1</sub> | Propagation delay time, SYNC_I to SYNC_O in daisy chain mode             |                 |     |     | 11 + 0.5*t <sub>CLK</sub> | ns                                                | Figure 12               |

| t <sub>d17</sub> | Delay time, SYNC_O and SDO 3-state to BUS_BUSY low in cascade            | mode.           | 0   |     | 2                         | ns                                                | Figure 8                |

|                  | Delay time, RD rising edge to BUS_BUSY high for device with              | +VBD = 3.3 V    |     |     | 8                         |                                                   | Figure 11,              |

| t <sub>d18</sub> | $LAT_Y/N = 1$                                                            | +VBD = 5 V      |     |     | 7                         | ns                                                | Figure 14               |

|                  | Delay time, point A indicating clear for bus 3-state release to BUSY     | +VBD = 3.3 V    |     |     | 40.5                      | ns                                                | Figure 6                |

| t <sub>d19</sub> | falling edge                                                             | +VBD = 5 V      |     | 40  |                           | 115                                               | rigure o                |

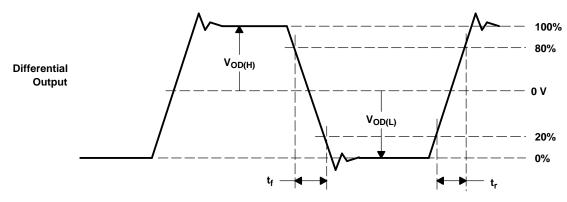

| t <sub>r</sub>   | Rise time, differential LVDS output signal                               |                 |     |     | 950                       | ps                                                | Figure 53               |

| t <sub>f</sub>   | Fall time, differential LVDS output signal                               |                 |     |     | 950                       | ps                                                | Figure 53               |

|                  | CLK frequency (serial data rate)                                         |                 | 190 |     | 210                       | MHz                                               |                         |

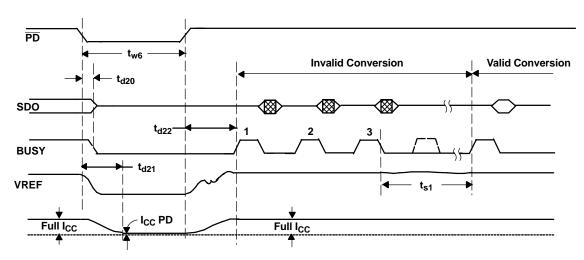

| t <sub>d20</sub> | Delay time, from PD falling edge to SDO 3-state                          |                 |     |     | 10                        | ns                                                | Figure 22,<br>Figure 23 |

| t <sub>d21</sub> | Delay time, from PD falling edge to device powerdown                     |                 |     |     | 10                        | μs                                                | Figure 22,<br>Figure 23 |

| t <sub>d22</sub> | d <sub>22</sub> Delay time, from PD rising edge to device powerup        |                 |     |     | 25                        | ms                                                | Figure 22,<br>Figure 23 |

| t <sub>s1</sub>  | Settling time, internal reference after first three conversions          |                 |     |     | 4                         | ms                                                | Figure 22               |

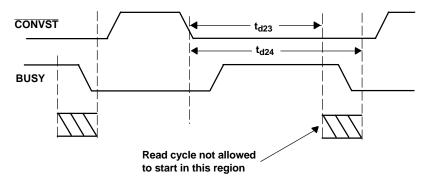

| t <sub>d23</sub> | Delay time, CONVST falling edge to start of restricted zone for start of |                 |     | 335 | ns                        | Figure 9                                          |                         |

| t <sub>d24</sub> | Delay time, CONVST falling edge to end of restricted zone for start of   | data read cycle |     |     | 406                       | ns                                                | Figure 9                |

NC – No internal connection

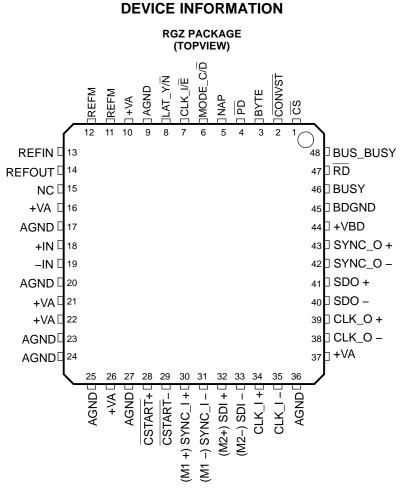

#### **TERMINAL FUNCTIONS**

| TE          | RMINAL             | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|-------------|--------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NO.         | NAME               | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| ANALOG PINS |                    |     |                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 11, 12      | REFM               | I   | Reference ground. Connect to analog ground plane.                                                                                                                                                                                                                                                                                                   |  |  |  |

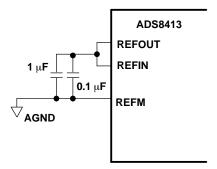

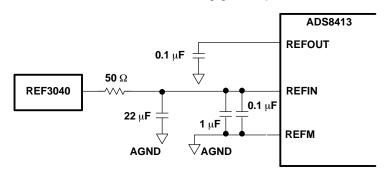

| 13          | REFIN              | I   | Reference (positive) input. Decouple with REFM pin using 0.1- $\mu$ F bypass capacitor and 1- $\mu$ F storage capacitor.                                                                                                                                                                                                                            |  |  |  |

| 14          | REFOUT             | 0   | Internal reference output. Short to REFIN pin when internal reference is used. Do not connect to REFIN pin when external reference is used. Always decouple with AGND using $0.1-\mu F$ bypass capacitor.                                                                                                                                           |  |  |  |

| 18          | +IN                | I   | Noninverting analog input channel                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 19          | –IN                | I   | Inverting analog input channel                                                                                                                                                                                                                                                                                                                      |  |  |  |

|             |                    |     | LVDS I/O PINS <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 28,<br>29   | CSTART+<br>CSTART- | I   | Device sample and convert control input. Device enters sample phase with rising edge of $\overrightarrow{\text{CSTART}}$ and conversion phase starts with falling edge of $\overrightarrow{\text{CSTART}}$ (provided other conditions are satisfied). Set $\overrightarrow{\text{CSTART}} = 0$ when $\overrightarrow{\text{CONVST}}$ input is used. |  |  |  |

(1) All LVDS inputs and outputs are differential with signal+ and signal- lines. Whenever only the 'signal' is mentioned it refers to the signal+ line and signal- line is the compliment. For example CLK\_O refers to CLK\_O+.

# **DEVICE INFORMATION (continued)**

# **TERMINAL FUNCTIONS (continued)**

| TE                                     | RMINAL               | 1/0                 | DESCRIPTION                                                                                                                                                                                                                                                                                     |

|----------------------------------------|----------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.                                    | NAME                 | 1/0                 | DESCRIPTION                                                                                                                                                                                                                                                                                     |

| 30,                                    | SYNC_I +<br>SYNC_I–  | l<br>Dasiy<br>Chain | Connect to previous device SYNC_O with same polarity, while device is selected to operate in daisy chain mode.                                                                                                                                                                                  |

| 31                                     | M1+<br>M1-           | l<br>Cascade        | Mode 1 (valid in cascade mode only). CLK_O available while M1=1 (LVDS) or M1+ is pulled up to +VBD and M1- is grounded (AGND). CLK_O o/p goes to 3-state when M1 = 0 (LVDS) or M1+ is grounded (AGND) and M1- is pulled up to +VBD. Do not allow these pins to float.                           |

| 32,                                    | SDI+<br>SDI–         | l<br>Daisy<br>Chain | Serial data input. Connect to previous device SDO with same polarity, while device is selected to operate in daisy chain mode.                                                                                                                                                                  |

| 33                                     | M2+<br>M2-           | l<br>Cascade        | Mode 2 (valid in cascade mode only). Doubles LVDS o/p current while M2 = 1 (LVDS) or M2+ is pulled up to +VBD and M2– is grounded (AGND). LVDS o/p current is normal (3.4 mA typ) when M2 = 0 (LVDS) or M2+ is grounded (AGND) and M2 – is pulled up to +VBD. Do not allow these pins to float. |

| 34,<br>35                              | CLK_I+<br>CLK_I-     | Ι                   | Serial external clock input. Set $CLK_{I/E}$ (pin 7) = 0 to select external clock source.                                                                                                                                                                                                       |

| 38,<br>39                              | CLK_O-<br>CLK_O+     | 0                   | Serial clock out. Data is latched out on the rising edge of CLK_O and can be captured on the next falling edge.                                                                                                                                                                                 |

| 40,<br>41                              | SDO-<br>SDO+         | Ο                   | Serial data out. Data is latched out on the rising edge of CLK_O with MSB first format.                                                                                                                                                                                                         |

| 42,<br>43                              | SYNC_O -<br>SYNC_O + | 0                   | Synchronizes the data frame. <sup>(2)</sup>                                                                                                                                                                                                                                                     |

|                                        | -                    |                     | CMOS I/O PINS                                                                                                                                                                                                                                                                                   |

| 1                                      | CS                   | I                   | Chip select, active low signal. All of the LVDS o/p except CLK_O are 3-state if this pin is high.                                                                                                                                                                                               |

| 2                                      | CONVST               | I                   | CMOS equivalent of $\overrightarrow{CSTART}$ input. So functionality is the same as the $\overrightarrow{CSTART}$ input. Set $\overrightarrow{CONVST}$ = 0 when the $\overrightarrow{CSTART}$ input is used.                                                                                    |

| 3                                      | BYTE                 | I                   | Controls the data frame <sup>(2)</sup> duration. The frame duration is 16 CLKs if BYTE = 0 or 8 CLKs if BYTE = $1$ .                                                                                                                                                                            |

| 4                                      | PD                   | I                   | Active low input, acts as device power down.                                                                                                                                                                                                                                                    |

| 5                                      | NAP                  | I                   | Selects nap mode while high. Device enters nap state at conversion end and remains so until next acquisition phase begins.                                                                                                                                                                      |

| 6                                      | MODE_C/D             | I                   | Selects cascade (MODE_C/ $\overline{D}$ = 1) or daisy chain mode (MODE_C/ $\overline{D}$ = 0).                                                                                                                                                                                                  |

| 7                                      | CLK_I/E              | I                   | Selects the source of the I/O clock.<br>$CLK_{I}/\overline{E} = 1$ selects internally generated clock with 200-MHz typ frequency.<br>$CLK_{I}/\overline{E} = 0$ selects $CLK_{I}$ as the I/O clock.                                                                                             |

| 8                                      | LAT_Y/N              | I                   | Controls the data read with latency (LAT_Y/ $\overline{N}$ = 1) or without latency ((LAT_Y/ $\overline{N}$ = 0). It is essential to set LAT_Y/ $\overline{N}$ = 0 for the first device in daisy chain or cascade.                                                                               |

| 46                                     | BUSY                 | 0                   | Active high signal, indicates a conversion is in progress.                                                                                                                                                                                                                                      |

| 47                                     | RD                   | I                   | Data read request to the device, also acts as a hand shake signal for daisy chain and cascade operation.                                                                                                                                                                                        |

| 48                                     | BUS_BUSY             | 0                   | Status output. Indicates that the bus is being used by the device. Connect to $\overline{RD}$ of the next device for daisy chain or cascade operation.                                                                                                                                          |

|                                        |                      |                     | POWER SUPPLY PINS                                                                                                                                                                                                                                                                               |

| 10, 16,<br>21, 22,<br>26, 37           | +VA                  | -                   | Analog power supply and LVDS input buffer power supply.                                                                                                                                                                                                                                         |

| 9, 17, 20,<br>23, 24,<br>25, 27,<br>36 | AGND                 | _                   | Analog ground pins. Short to the analog ground plane below the device.                                                                                                                                                                                                                          |

| 44                                     | +VBD                 | _                   | Digital power supply for all CMOS digital inputs and CMOS, LVDS outputs.                                                                                                                                                                                                                        |

| 45                                     | BDGND                | -                   | Digital ground for all digital inputs and outputs. Short to the analog ground plane below the device.                                                                                                                                                                                           |

(2) The duration from the first rising edge of SYNC\_O to the second rising edge of SYNC\_O is one data frame. The data frame duration is 16 CLKs if BYTE = 0 or 8 CLKs if BYTE = 1.

# **DEVICE INFORMATION (continued)**

#### **TERMINAL FUNCTIONS (continued)**

| TE  | TERMINAL                                                     |       | DESCRIPTION |  |  |  |  |

|-----|--------------------------------------------------------------|-------|-------------|--|--|--|--|

| NO. | NAME                                                         | - I/O | DESCRIPTION |  |  |  |  |

|     | NOT CONNECTED PINS                                           |       |             |  |  |  |  |

| 15  | 15 NC – No connection pins                                   |       |             |  |  |  |  |

|     | Table 1. Device Configuration for Various Modes of Operation |       |             |  |  |  |  |

#### DEVICE PINS AND RECOMMENDED LOGIC LEVELS REFERENCE FIGURES COMMENTS FOR SAMPLING **OPERATION MODE** FOR DATA MODE\_C/D CLK\_I/E LAT\_Y/N M2+ M2-M1+ M1-AND CONVERSION READ +VBD AGND AGND +VBD See Figures 3,4 1 1 or 0 0 Recommended configuration 1 or 2 and 5,6,8 for or M1 = 1 LVDS or M2 = 0 LVDS more details Single device Set SYNC\_I and SDI to logic 0 See Figures 3,4 and 5,6,7 for 0 1 or 0 0 See comments See comments or + terminal to AGND and -ve 1 or 2 terminal to +VBD more details Set SYNC\_I and SDI to logic 0 Multiple 1st Device 0 1 or 0 0 See comments See comments or + terminal to AGND and -ve 1 or 2 See Figures devices terminal to +VBD 3.4.11 and 6.12 in daisy for more details Maximum 4 devices supported at 2 MSPS with 200-MHz CLK 2nd To last chain 0 0 1 See comments See comments 1 or 2 device +VBD AGND AGND +VBD 1st Device 1 0 0 Multiple See Figures 3,4,14 and 6,15 or M1 = 1 LVDS or M2 = 0 LVDS<sup>(1)</sup> devices Maximum 3 devices supported 1 or 2 in +VBD AGND AGND +VBD at 2 MSPS for more details 2nd To last cascade 0 1 1 device or M1 = 0 LVDS or M2 = 0 LVDS(1)

(1) Specified polarity is suitable for a  $100-\Omega$  differential load across the LVDS outputs. However, polarity can be reversed to double the output current in order to support two  $100-\Omega$  loads on both ends of the transmission lines, resulting in  $50-\Omega$  net load.

# **DETAILED DESCRIPTION**

## SAMPLE AND CONVERT

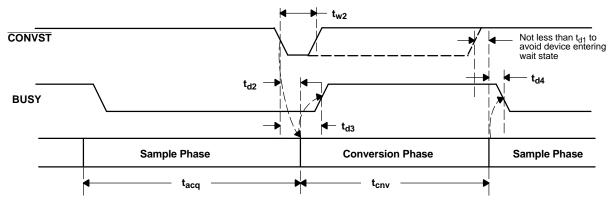

The sampling and conversion process is controlled by the  $\overline{\text{CSTART}}$  (LVDS) or  $\overline{\text{CONVST}}$  (CMOS) signal. Both signals are functionally identical. The following diagrams show control with  $\overline{\text{CONVST}}$ . The rising edge of  $\overline{\text{CONVST}}$  (or  $\overline{\text{CSTART}}$ ) starts the sample phase, if the conversion has completed and the device is in the wait state. Figure 2 shows the case when the device is in the conversion phase at the rising edge of  $\overline{\text{CONVST}}$ . In this case, the sample phase starts immediately at the end of the conversion phase and there is no wait state.

Figure 1. Sample and Convert With Wait (Less Than 2 MSPS Throughput)

## **DETAILED DESCRIPTION (continued)**

Figure 2. Sample and Convert With No Wait or Back to Back (2 MSPS Throughput)

The device ends the sample phase and enters the conversion phase on the falling edge of CONVST (CSTART). A high level on the BUSY output indicates an ongoing conversion. The device conversion time is fixed. The falling edge of CONVST (CSTART) during the conversion phase aborts the ongoing conversion. A data read after a conversion abort fetches invalid data. Valid data is only available after a sample phase and a conversion phase has completed. The timing diagram for control with CSTART is similar to Figure 1 and Figure 2. Table 2 shows the equivalent timing for control with CONVST and CSTART.

|                            | •••••••••••••••••••••••••••••••••••••• |  |  |

|----------------------------|----------------------------------------|--|--|

| TIMING CONTROL WITH CONVST | TIMING CONTROL WITH CSTART             |  |  |

| t <sub>w1</sub>            | t <sub>w3</sub>                        |  |  |

| t <sub>w2</sub>            | t <sub>w4</sub>                        |  |  |

| t <sub>d1</sub>            | t <sub>d5</sub>                        |  |  |

| t <sub>d2</sub>            | t <sub>d6</sub>                        |  |  |

| t <sub>d3</sub>            | t <sub>d7</sub>                        |  |  |

#### Table 2. CONVST and CSTART Timing Control

#### DATA READ OPERATION

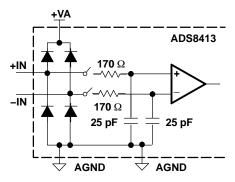

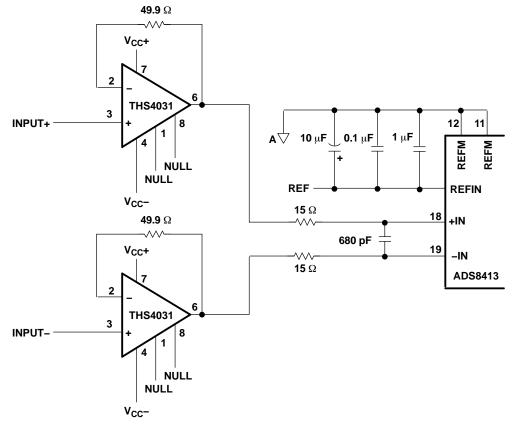

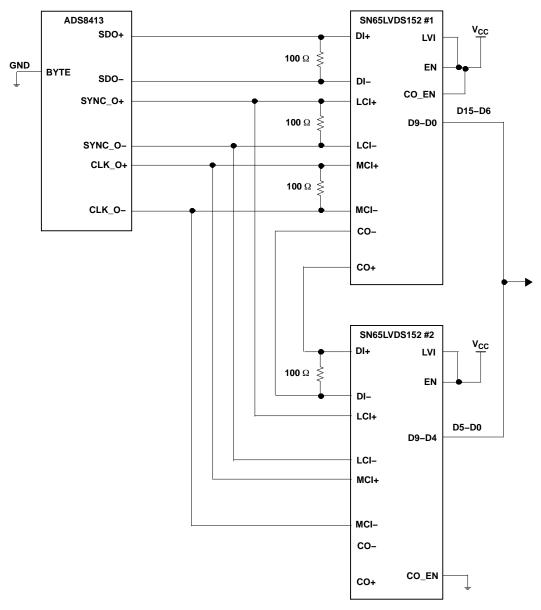

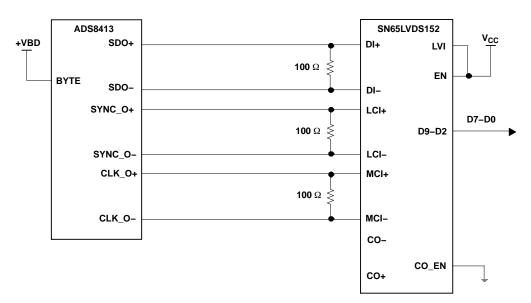

The ADS8413 supports a 200-MHz serial LVDS interface for data read operation. The three signal LVDS interface (SDO, CLK\_O, and SYNC\_O) is well suited for high-speed data transfers. An application with a single device or multiple devices can be implemented with a daisy chain or cascade configuration. The following sections discuss data read timing when a single device is used.

#### DATA READ FOR A SINGLE DEVICE (See Table 1 for Device Configuration)

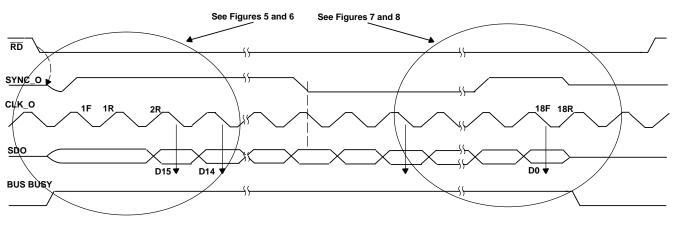

For a single device, there are two possible read cycle starts: a data read cycle start during a wait or sample phase or a data read cycle start at the end of a conversion phase. Read cycle end conditions can change depending on MODE C/D selection. Figure 3 explains the data read cycle. The details of a read frame start with the two previous listed conditions and a read cycle end with MODE C/D selection are explained in Figure 5 and Figure 6 and Figure 7 and Figure 8, respectively.

Figure 3. Data Read With  $\overline{CS}$  Low and BYTE = 0

As shown in Figure 3, a new data read cycle is initiated with the falling edge of  $\overline{RD}$ , if  $\overline{CS}$  is low and the device is in a wait or sample phase. The device releases the LVDS o/p (SYNC\_O, SDO) from 3-state and sets BUS\_BUSY high at the start of the read cycle. The SYNC\_O cycle is 16 clocks wide (rising edge to rising edge) if BYTE i/p is held low and can be used to synchronize a data frame. The clock count begins with the first CLK\_O falling edge after a SYNC\_O rising edge. The MSB is latched out on the second rising edge (2R) and each subsequent data bit is latched out on the rising edge of the clock. The receiver can shift data bits on the falling edges of the clock. The next rising edge of SYNC\_O coincides with the 16th rising edge of the clock. D0 is latched out on the 17th rising edge of the clock. The receiver can latch the de-serialized 16-bit word on the 18th rising edge (18R, or the second rising edge after a SYNC\_O rising edge).

CS high during a data read 3-states SYNC\_O and SDO. These signals remain in 3-state until the start of the next data read cycle.

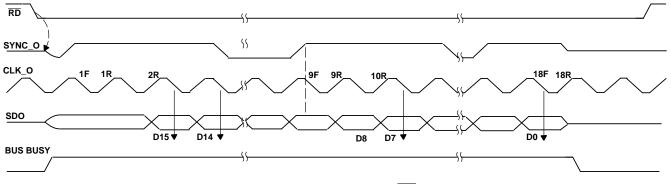

## DATA READ IN BYTE MODE

Byte mode is selected by setting BYTE = 1, this mode is allowed for any condition listed in Table 1. Figure 4 shows a data read operation in byte mode.

Figure 4. Data Read Timing Diagram with  $\overline{CS}$  Low and BYTE = 1

Similar to Figure 3, a new data read cycle is initiated with the falling edge of RD, if CS is low and device is in a wait or sample phase. The device releases the LVDS o/p (SYNC\_O, SDO) from 3-state and sets BUS\_BUSY high at the start of the read cycle. The SYNC\_O cycle is 8 clocks wide (rising edge to rising edge) if BYTE i/p is held high and can be used to synchronize a data frame. The clock count begins with the first CLK\_O falling edge after a SYNC\_O rising edge. The MSB is latched out on the second rising edge (2R) and each subsequent data bit is latched out on the rising edge of the clock. The receiver can shift data bits on the falling edges of clock. The next rising edge of SYNC\_O coincides with the 8th rising edge of the clock. D8 is latched out on the 9th rising edge of the clock. The receiver can latch the de-serialized higher byte on the 10th rising edge (10R, or second rising edge after a SYNC\_O rising edge). The de-serialized lower byte can be latched on the 18th rising edge (18R).

CS high during a data read 3-states SYNC\_O and SDO. These signals remain in 3-state until the start of the next data read cycle.

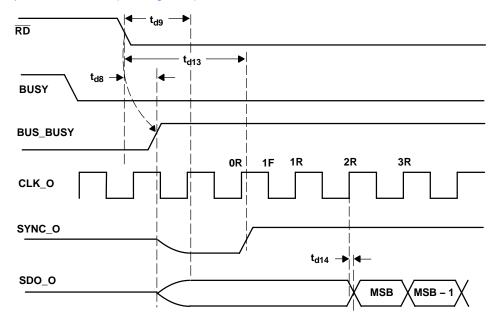

#### DATA READ CYCLE START DURING WAIT OR SAMPLE PHASE

As shown in Figure 5, the falling edge of  $\overline{RD}$ , with  $\overline{CS}$  low and the device is in a wait or sample phase, triggers the start of a read cycle. The cycle starts when BUS\_BUSY goes high and SYNC\_O, SDO are released from 3-state. SYNC\_O is low at the start and rises to a high level t<sub>d13</sub> ns after the falling edge of  $\overline{RD}$ . As shown in Figure 5, the MSB is shifted on the 2nd rising edge of the clock (2R). Other details about the data read cycle are discussed in the previous section (see Figure 3).

Figure 5. Start of Data Read Cycle with RD with CS Low and Device in Wait or Sample Phase

#### DATA READ CYCLE START AT END OF CONVERSION PHASE (Read Without Latency, Back-to-Back)

This mode is optimized for a data read immediately after the end of a conversion phase and ensures the data read is complete before the sample end while running at 2 MSPS. Point A in Figure 6 indicates 'pre\_conversion\_end'; it occurs  $t_{d19}$  ns before the falling edge of BUSY or  $[(t_{d2} + t_{cnv} + t_{d4}) - t_{d19}]$  ns after the falling edge of CONVST. A read cycle is initiated at point A if RD is issued before point A while CS is low. Alternately, RD and CS can be held low. At the start of the read cycle, BUS\_BUSY rises to a high level and the LVDS outputs are released from 3-state. The rising edge of SYNC\_O occurs  $t_{d12}$  ns after the conversion end. As shown in Figure 6, the MSB is shifted on the 2nd rising edge of the clock (2R). Other details about the data read cycle are discussed in the previous section (see Figure 3).

TEXAS INSTRUMENTS www.ti.com

SLAS490-OCTOBER 2005

Figure 6. Start of Data Read Cycle with End of Conversion

## DATA READ CYCLE END (With MODE $C/\overline{D} = 0$ )

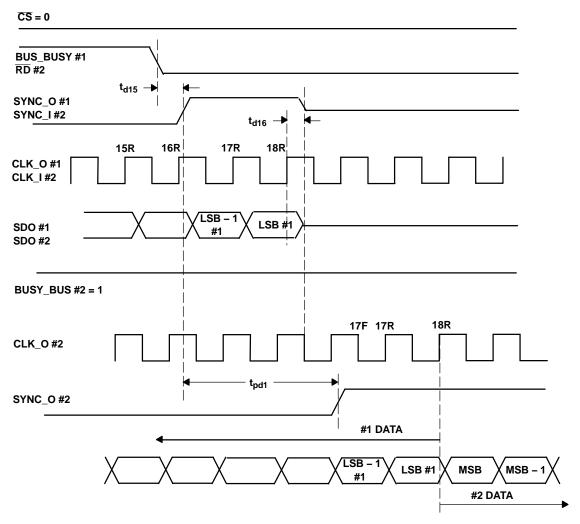

A data read cycle ends after all 16 bits have been serially latched out. Figure 7 shows the timing of the falling edge of BUS\_BUSY and the rising edge of SYNC\_O with respect to SDO. SYNC\_O rises on the 16th rising edge of CLK\_O. As shown in Figure 5 and Figure 6, the MSB is shifted out on the 2nd rising edge of CLK\_O. Therefore, the LSB-1 is shifted out on the 16th rising edge of CLK\_O.

Figure 7. Data Read Cycle End with MODE  $C/\overline{D} = 0$

The next two rising edges of CLK\_O are shown as 17R and 18R in Figure 7. On 17R the LSB is latched out, and on 18R SDO and SYNC-O go to 3-state. Note that BUS\_BUSY falls  $t_{d15}$  ns before the rising edge of SYNC\_O when MODE C/D = 0. Care must be taken not to allow LVDS bus usage by any other device until the end of the read cycle or ( $t_{d15} + 2/f_{clk} + t_{d16}$ ) ns after the falling edge of BUS\_BUSY.

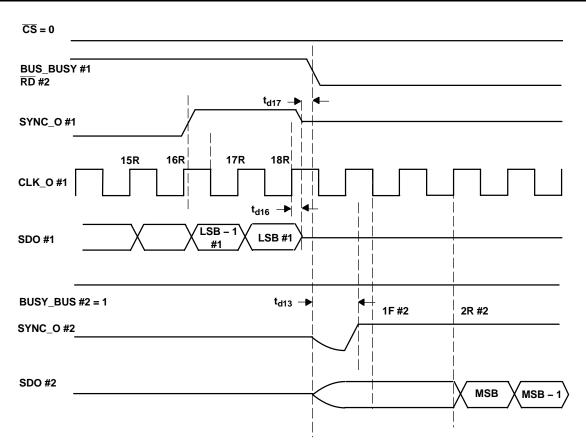

#### DATA READ CYCLE END (With MODE $C/\overline{D} = 1$ )

A data read cycle ends after all 16 bits have been serially latched out. Figure 8 shows the timing of the falling edge of BUS\_BUSY and the rising edge of SYNCO with respect to SDO. SYNC\_O rises on the 16th rising edge of CLK\_O. As shown in Figure 5 and Figure 6, the MSB is shifted out on the 2nd rising edge of CLK\_O. Therefore, the LSB-1 is shifted out on the 16th rising edge of CLK\_O.

Figure 8. Data Read Cycle End with MODE  $C/\overline{D} = 1$

The next two rising edges of CLK\_O are shown as 17R and 18R in Figure 8. On 17R the LSB is latched out and on 18R the SDO and SYNC\_O go in 3-state. In cascade mode (with MODE C/D = 1) unlike daisy chain mode BUS\_BUSY falling edge occurs after LVDS outputs are 3-state. One can use BUS\_BUSY falling edge to allow the LVDS bus usage by any other device.

## **RESTRICTIONS ON READ CYCLE START**

Figure 9. Read Cycle Restriction Region

The start of a data read cycle is not allowed in the region bound by  $t_{d23}$  and  $t_{d24}$ . Previous conversion results are available for a data read cycle start before this region, and current conversion results are available for a read cycle start after this region.

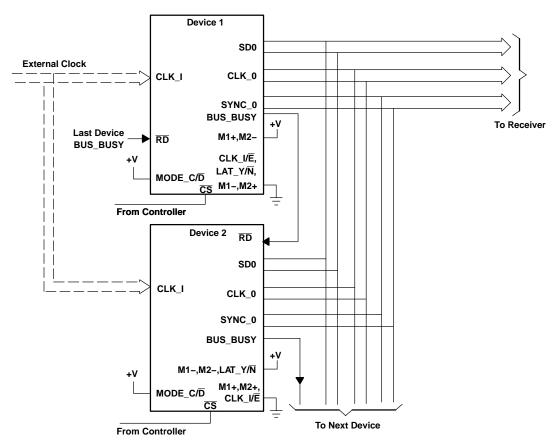

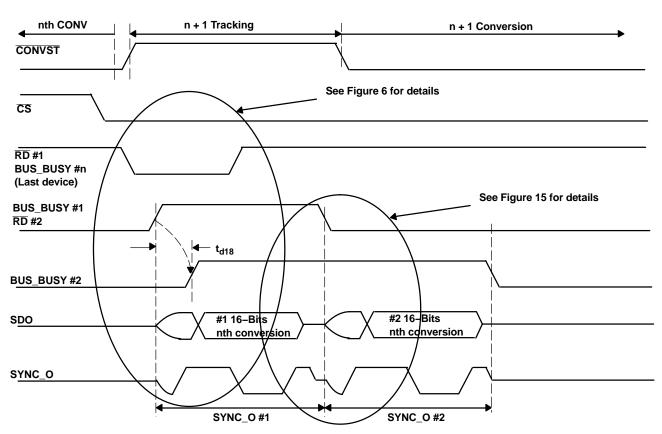

# MULTIPLE DEVICES IN DAISY CHAIN OR CASCADE

Multiple devices can be connected in either a daisy chain or cascade configuration. The following sections describes detailed timing diagrams and electrical connections. The ADS8413 provides all of the hand-shake signals required for both of these modes. CONVST or CSTART is the only external signal needed for operation.

#### DAISY CHAIN

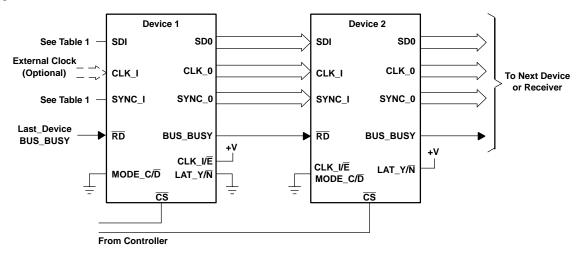

Figure 10 shows the first two devices in daisy chain. The signals shown by double lines are LVDS and the others are CMOS. Daisy chain mode is selected by setting  $MODE_C/\overline{D} = 0$ . The first device in the chain is identified by selecting LAT\_Y/N = 0.

Figure 10. Connecting Multiple Devices in Daisy Chain

For all of the other devices in the chain LAT\_Y/ $\overline{N}$  = 1. See Table 1 for more details on device configurations. SDO, CLK\_O, and SYNC\_O of device *n* are to be connected to SDI, CLK\_I, and SYNC\_I of *the n+1* device. SDO, CLK\_O, and SYNC\_O of the last device in the chain go to the receiver. BUS\_BUSY of device *n* is connected to RD of device *n+1* and so on. Finally, BUS\_BUSY of the last device in the chain is connected to RD of device 1. This ensures the necessary handshake to seamlessly propagate the data of all devices through the chain (it is also allowed to tie  $\overline{RD}$  = 0 for device 1).

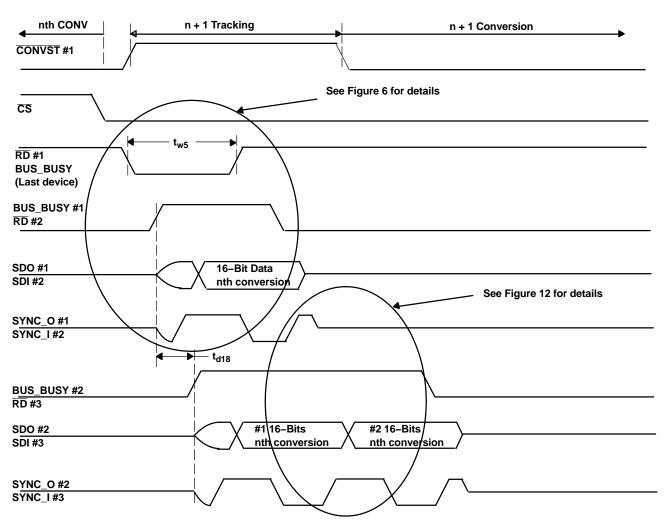

## TIMING DIAGRAMS FOR DAISY CHAIN OPERATION

The conversion speed for n devices in the chain must be selected such that:

#### 1/conversion speed > read startup delay + $n^*(data frame duration) + t_{d16}$

# Read startup delay = 10 ns + $(t_{d19} - t_{d4}) + t_{d12} + 2/f_{CLK}$

#### Data frame duration = 16/f<sub>CLK</sub>

Note that it is not necessary for all devices in the chain to sample the data simultaneously. But all of the devices must operate with the same exact conversion speed.

# ADS8413

SLAS490-OCTOBER 2005

Figure 11. Data Read Operation for Devices in Daisy Chain

# DATA READ OPERATION