SBAS611B - SEPTEMBER 2013-REVISED OCTOBER 2013

# 14-Bit, Input-Buffered, 160-MSPS, Analog-to-Digital Converter with JESD204A Output Interface

Check for Samples: ADS61JB46

#### **FEATURES**

- **Output Interface:**

- Single-Lane and Dual-Lane Interfaces

- Maximum Data Rate: 3.125 Gbps

- Meets JEDEC JESD204A Specification

- CML Outputs with Current Programmable from 2 mA to 32 mA

- **Power Dissipation:**

- 583 mW at 160 MSPS in Dual-Lane Mode

- **Power Scales Down with Clock Rate**

- Input Interface: Buffered Analog Inputs

- SNR at 185-MHz IF: -72.7 dBFS

- Analog Input Dynamic Range: 2 Vpp

- **Reference Support: External and Internal (Trimmed)**

- Supply:

- Analog and Digital: 1.8 V

- Input Buffer: 3.3 V

- Programmable Digital Gain: 0 dB to 6 dB

- **Output: Straight Offset Binary or Twos Complement**

- Package: 6-mm × 6-mm QFN-40

#### APPLICATIONS

- **Wireless Base-Station Infrastructures**

- **Test and Measurement Instrumentation**

#### DESCRIPTION

The ADS61JB46 is a high-performance, low-power, single-channel, analog-to-digital converter with an integrated JESD204A output interface. Available in a 6-mm × 6-mm QFN package, with both single-lane and dual-lane output modes, the device offers an unprecedented level of compactness. The output interface is compatible to the JESD204A standard, with an additional mode (as per the IEEE standard 802.3-2002 part 3, clause 36.2.4.12) to interface seamlessly to the TI TLK family of SERDES transceivers. Equally impressive is the inclusion of an on-chip analog input buffer, providing isolation between the sample-and-hold switches and higher and more consistent input impedance.

device is specified over the industrial temperature range (-40°C to +85°C).

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## ABSOLUTE MAXIMUM RATINGS(1)

|                                                      |                    | VALUE                          | UNIT |

|------------------------------------------------------|--------------------|--------------------------------|------|

|                                                      | AVDD               | -0.3 to +2.2                   | V    |

| Supply voltage range                                 | DRVDD              | -0.3 to +2.2                   | V    |

|                                                      | IOVDD              | -0.3 to +2.2                   | V    |

|                                                      | AVDD_3V            | -0.3 to +3.9                   | V    |

| Voltage between AGND and DRGND                       |                    | -0.3 to +0.3                   | V    |

|                                                      | External VCM pin   | -0.3 to +2.2                   | V    |

| Valtage applied to                                   | Analog input pins  | -0.3 to min (3, AVDD_3V + 0.3) | V    |

| Voltage applied to:                                  | Digital input pins | -0.3 to AVDD + 0.3             | V    |

| Clock input pins (2)                                 |                    | -0.3 to AVDD + 0.3             | V    |

| Operating free-air temperature range, T <sub>A</sub> |                    | -40 to +85                     | °C   |

| Junction temperature                                 |                    | +105                           | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### THERMAL INFORMATION

|                         | THERMAL METRIC <sup>(1)</sup>                | ADS61JB46 | LINUTO |

|-------------------------|----------------------------------------------|-----------|--------|

|                         | THERMAL METRIC                               | RHA (QFN) | UNITS  |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance       | 30.7      |        |

| $\theta_{JCtop}$        | Junction-to-case (top) thermal resistance    | 17        |        |

| $\theta_{JB}$           | Junction-to-board thermal resistance         | 5.7       | 9C/M/  |

| ΨЈТ                     | Junction-to-top characterization parameter   | 0.2       | °C/W   |

| ΨЈВ                     | Junction-to-board characterization parameter | 5.7       |        |

| $\theta_{\text{JCbot}}$ | Junction-to-case (bottom) thermal resistance | 1         |        |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

<sup>(2)</sup> When AVDD is turned off, TI recommends switching off the input clock (or ensuring the voltage on CLKP, CLKM is less than |0.3 V|). This setting prevents the electrostatic discharge (ESD) protection diodes at the clock input pins from turning on.

## **RECOMMENDED OPERATING CONDITIONS**

|                   |                                                                             |                                    | MIN    | TYP               | MAX   | UNIT            |

|-------------------|-----------------------------------------------------------------------------|------------------------------------|--------|-------------------|-------|-----------------|

| SUPPLIES, ANALO   | G INPUTS, AND REFERENCE VO                                                  | LTAGES                             |        |                   | '     |                 |

| AVDD              | Analog supply voltage                                                       |                                    | 1.7    | 1.8               | 1.9   | V               |

| DRVDD             | Digital supply voltage                                                      |                                    | 1.7    | 1.8               | 1.9   | V               |

| IOVDD             | CML buffer supply voltage                                                   |                                    | 1.7    | 1.8               | 1.9   | V               |

| AVDD_3V           | Analog buffer supply voltage                                                |                                    | 3.0    | 3.3               | 3.6   | V               |

|                   | Differential input voltage range                                            | )                                  |        | 2                 |       | V <sub>PP</sub> |

|                   | Input common-mode voltage                                                   |                                    |        | VCM ± 0.05        |       | V               |

|                   | VCM (output), internal reference                                            | ce mode <sup>(1)</sup>             |        | 1.95              |       | V               |

|                   | VCM (input), external reference                                             | e mode                             |        | 1.4               |       | V               |

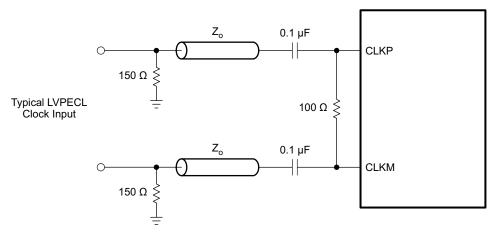

| CLOCK INPUT       |                                                                             |                                    |        |                   | "     |                 |

|                   | Input clock rate                                                            | In JESD204A single-lane mode       | 15.625 |                   | 156.3 | MSPS            |

|                   |                                                                             | In JESD204A dual-lane mode         | 31.25  |                   | 160   | MSPS            |

|                   |                                                                             | Sine wave, ac-coupled              | 0.2    | 3.0               |       | $V_{PP}$        |

|                   | Input clock amplitude differential (V <sub>CLKP</sub> – V <sub>CLKM</sub> ) | LVPECL, ac-coupled                 |        | 1.6               |       | $V_{PP}$        |

|                   |                                                                             | LVDS, ac-coupled                   |        | 0.7               |       | $V_{PP}$        |

|                   |                                                                             | CMOS, single-ended, ac-<br>coupled |        | 1.5               |       | V               |

|                   | Input clock duty cycle                                                      |                                    | 35%    | 50%               | 65%   |                 |

| DIGITAL OUTPUTS   | }                                                                           | ,                                  |        |                   | '     |                 |

|                   | Outrot data ante                                                            | In single-lane mode                | 312.5  | 20x (sample rate) | 3125  | Mbps            |

|                   | Output data rate                                                            | In dual-lane mode                  | 312.5  | 10x (sample rate) | 1600  | Mbps            |

| C <sub>LOAD</sub> | Maximum external load capacitance from each pin to DRGND                    |                                    |        | 5                 |       | pF              |

| R <sub>LOAD</sub> | External termination from each output pin to IOVDD                          |                                    |        | 50                |       | Ω               |

| T <sub>A</sub>    | Operating free-air temperature                                              |                                    | -40    |                   | +85   | °C              |

<sup>(1)</sup> Typical VCM reduces to 1.85 V after HIGH\_SFDR\_MODE (register address 02h) is written.

## Table 1. HIGH\_SFDR\_MODE Summary

| MODE           | DESCRIPTION                                                                                         |

|----------------|-----------------------------------------------------------------------------------------------------|

| HIGH_SFDR_MODE | Write register 02h, value 71h, to obtain best HD3 for input frequencies between 150 MHz to 250 MHz. |

### **ELECTRICAL CHARACTERISTICS**

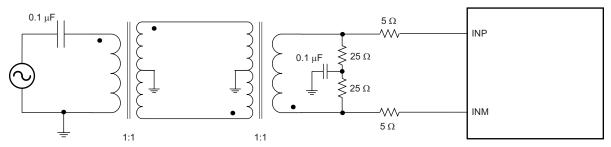

Typical values are at +25°C, minimum and maximum values are across the full temperature range of  $T_{MIN} = -40$ °C to  $T_{MAX} = +85$ °C, AVDD = 1.8 V, AVDD\_3V = 3.3 V, DRVDD = 1.8 V, IOVDD = 1.8 V, clock frequency = 160 MSPS, 10x mode, 50% clock duty cycle, -1-dBFS differential analog input, internal reference mode, and CML buffer current setting = 16 mA, unless otherwise noted.

|                      | PARAMETER                                                | TEST CONDITIONS                           | MIN          | TYP       | MAX  | UNIT     |

|----------------------|----------------------------------------------------------|-------------------------------------------|--------------|-----------|------|----------|

| REFEREN              | ICE VOLTAGES (Internal)                                  |                                           |              |           |      |          |

|                      | VCM analog input common-mode voltage (output)            |                                           |              | 1.95      |      | V        |

|                      | VCM output current (resulting in a VCM change of ±50 mV) |                                           |              | 2.5       |      | mA       |

| REFEREN              | ICE VOLTAGES (External)                                  |                                           |              |           |      |          |

|                      | VCM reference voltage (input)                            |                                           |              | 1.4 ± 0.1 |      | V        |

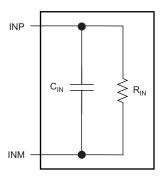

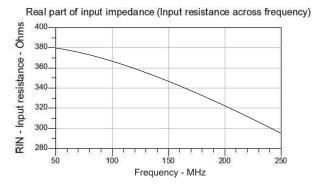

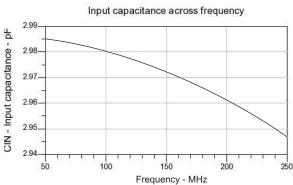

| ANALOG               | INPUT                                                    |                                           |              |           |      |          |

|                      | Differential input voltage range                         |                                           |              | 2.0       |      | $V_{PP}$ |

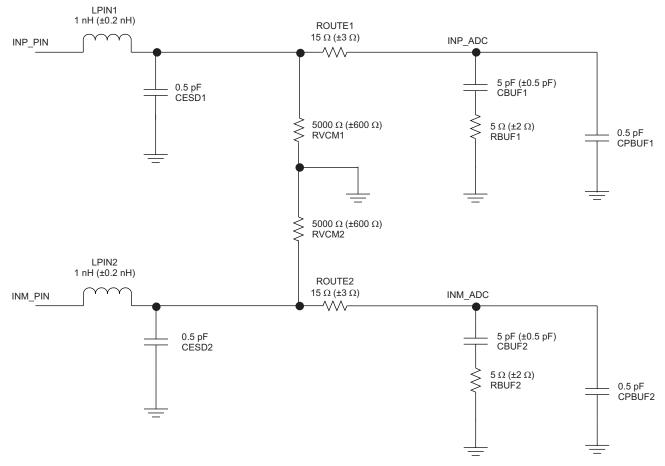

|                      | Differential input capacitance                           |                                           |              | 3         |      | pF       |

|                      | Analog input bandwidth                                   |                                           |              | 480       |      | MHz      |

|                      | Analog input common-mode range                           |                                           | VC           | M ± 0.05  |      | V        |

|                      | Analog input common-mode current (per input pin)         |                                           |              | 1.6       |      | μA       |

| DC ACCU              | RACY                                                     |                                           |              |           |      |          |

| Eo                   | Offset error                                             |                                           | -20          |           | 20   | mV       |

| E <sub>GREF</sub>    | Gain error due to internal reference inaccuracy alone    |                                           | -2.5         |           | 2.5  | %FS      |

| E <sub>GCHAN</sub>   | Gain error of channel alone                              |                                           |              | 5         |      | %FS      |

|                      | Gain error temperature coefficient                       |                                           |              | 0.006     |      | mV/°C    |

| PSRR                 | AC power-supply rejection ratio                          | 50-mV <sub>PP</sub> signal on AVDD supply |              | > 30      |      | dB       |

| POWER-D              | OOWN MODES                                               |                                           |              |           |      |          |

|                      | Complete power-down mode                                 |                                           |              | 10        |      | mW       |

|                      | Fast recovery power-down mode                            |                                           |              | 230       |      | mW       |

|                      | Power with no clock                                      |                                           |              | 115       |      | mW       |

| DNL                  | Differential nonlinearity                                |                                           | -0.95        | ±0.6      |      | LSB      |

| INL                  | Integral nonlinearity                                    |                                           |              | ±2        | ±4.5 | LSB      |

| POWER-S              | SUPPLY CURRENTS                                          |                                           | <del>.</del> |           |      |          |

| I <sub>AVDD</sub>    | AVDD current                                             |                                           |              | 132       | 160  | mA       |

| I <sub>AVDD_3V</sub> | AVDD_3V current                                          |                                           |              | 42        | 55   | mA       |

| I <sub>DRVDD</sub>   | DRVDD current                                            |                                           |              | 79        | 100  | mA       |

| I <sub>IOVDD</sub>   | IOVDD current (in 10x mode)                              |                                           |              | 31        | 40   | mA       |

|                      | Total power                                              |                                           |              | 583       | 700  | mW       |

| DYNAMIC              | PERFORMANCE <sup>(1)(2)</sup>                            |                                           |              |           |      |          |

| 0555                 |                                                          | f <sub>IN</sub> = 10 MHz                  |              | 75        |      | dBc      |

| SFDR                 | Spurious-free dynamic range                              | f <sub>IN</sub> = 185 MHz                 | 71.5         | 77        |      | dBc      |

| 0110                 | 0                                                        | f <sub>IN</sub> = 10 MHz                  |              | 75        |      | dBFS     |

| SNR                  | Signal-to-noise ratio                                    | f <sub>IN</sub> = 185 MHz                 | 69.2         | 72.7      |      | dBFS     |

| OINIAD               | 0. 1                                                     | f <sub>IN</sub> = 10 MHz                  |              | 72.1      |      | dBFS     |

| SINAD                | Signal-to-noise and distortion ratio                     | f <sub>IN</sub> = 185 MHz                 |              | 71.5      |      | dBFS     |

| LIDO                 | <b>T</b>                                                 | f <sub>IN</sub> = 10 MHz                  |              | 75        |      | dBc      |

| HD3                  | Third-order harmonic distortion                          | f <sub>IN</sub> = 185 MHz                 | 71.5         | 77        |      | dBc      |

|                      |                                                          | f <sub>IN</sub> = 10 MHz                  |              | 90        |      | dBc      |

| HD2                  | Second-order harmonic distortion                         | f <sub>IN</sub> = 185 MHz                 | 71.5         | 81        |      | dBc      |

|                      |                                                          | f <sub>IN</sub> = 10 MHz                  |              | 95        |      | dBc      |

|                      | Worst spur (excluding HD2, HD3)                          | f <sub>IN</sub> = 185 MHz                 | 81           | 90        |      | dBc      |

<sup>(1)</sup> HIGH\_SFDR\_MODE is enabled.

<sup>(2)</sup>  $f_S = 156.25 \text{ MSPS}$ , 20x mode.

## **DIGITAL CHARACTERISTICS**

The dc specifications refer to the condition where the digital outputs do not switch, but are permanently at a valid logic level '0' or '1'.

|                                          | PARAMETER                            | TEST CONDITIONS                                                         | MIN         | TYP       | MAX  | UNIT  |

|------------------------------------------|--------------------------------------|-------------------------------------------------------------------------|-------------|-----------|------|-------|

| DIGITAL                                  | INPUTS                               |                                                                         |             |           |      |       |

| V <sub>IH</sub>                          | High-level input voltage             |                                                                         | 1.2         |           |      | V     |

| V <sub>IL</sub>                          | Low-level input voltage              |                                                                         |             |           | 0.6  | V     |

|                                          |                                      | SEN                                                                     |             | 0         |      | μA    |

| I <sub>IH</sub>                          | High-level input current             | SCLK, SDATA, RESET, PDN, PDN_ANA                                        |             | 10        |      | μA    |

|                                          | Laurentinaut aumant                  | SEN                                                                     |             | 10        |      | μΑ    |

| I <sub>IL</sub>                          | Low-level input current              | SCLK, SDATA, RESET, PDN, PDN_ANA                                        |             | 0         |      | μA    |

| DIGITAL                                  | OUTPUTS (SDOUT)                      |                                                                         |             |           |      |       |

| V <sub>OH</sub>                          | High-level output voltage            |                                                                         | DRVDD - 0.1 | DRVDD     |      | V     |

| V <sub>OL</sub>                          | Low-level output voltage             |                                                                         |             | 0         | 0.1  | V     |

| CML OU                                   | TPUTS (50-Ω single-ended external to | ermination to IOVDD)                                                    |             |           |      |       |

|                                          | IOVDD supply range                   |                                                                         | 1.7         | 1.8       | 1.9  | V     |

|                                          | High-level output voltage            |                                                                         |             | IOVDD     |      | V     |

|                                          | Low-level output voltage             |                                                                         | IC          | VDD - 0.4 |      | V     |

| VOD                                      | Output differential voltage          |                                                                         |             | 0.4       |      | V     |

| V <sub>OCM</sub>                         | Output common-mode voltage           |                                                                         | IC          | VDD - 0.2 |      | V     |

|                                          | Transmitter short-circuit current    | Transmitter terminals shorted to any voltage between –0.25 V and 1.45 V | -90         |           | 50   | mA    |

|                                          | Single-ended output impedance        |                                                                         |             | 50        |      | Ω     |

| UI                                       | Unit interval                        |                                                                         | 625         |           | 3200 | UI    |

| TJ                                       | Total jitter                         |                                                                         |             | 0.35      |      | p-pUI |

| t <sub>RISE</sub> ,<br>t <sub>FALL</sub> | Rise time,<br>Fall time              | 5-pF, single-ended load capacitance to ground                           |             | 175       |      | ps    |

## **WAKE-UP TIMING CHARACTERISTICS**

Copyright © 2013, Texas Instruments Incorporated

| PARAMETER                      |                                                                 | TEST CONDITIONS                                                      | MIN | TYP | MAX | UNIT |

|--------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>WAKE</sub> Wake-up time | Time to valid data after coming out of complete power-down mode |                                                                      | 50  |     | μs  |      |

|                                | Waka un tima                                                    | Time to valid data after coming out of fast-recovery power-down mode |     | 50  |     | μs   |

|                                | Time to valid data after coming out of software power-down mode |                                                                      | 10  |     | μs  |      |

|                                |                                                                 | Time to valid data after stopping and restarting the input clock     |     | 5   |     | μs   |

#### PARAMETRIC MEASUREMENT INFORMATION

#### **JESD204A OUTPUT INTERFACE**

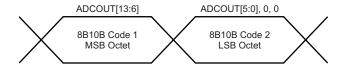

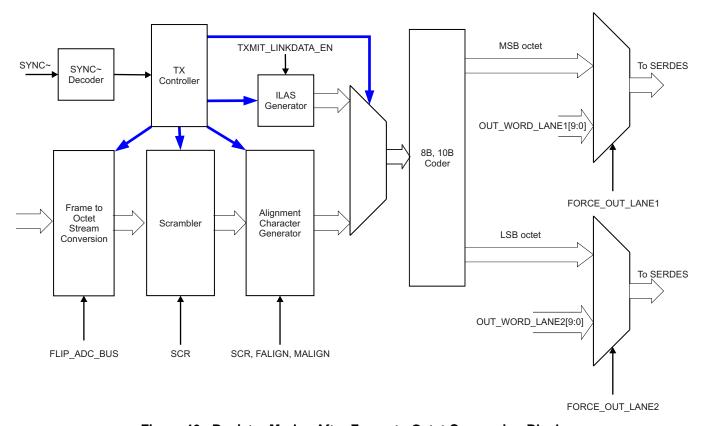

The 14-bit analog-to-digital converter (ADC) output is padded with four zeros on the LSB side to form a 16-bit output. Two 8B10B codes are formed; one from the eight MSBs and the other from the six LSBs and the two padded zeros, as shown in Figure 1.

Figure 1. ADC Output Mapping to Two 8B10B Codes

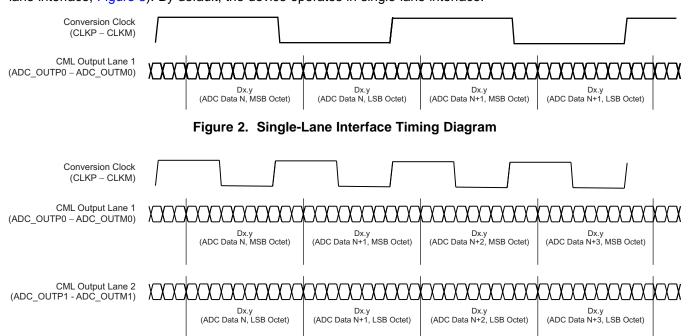

The two octets can be either transmitted on the same lane (single-lane interface, Figure 2) or on two lanes (dual-lane interface, Figure 3). By default, the device operates in single-lane interface.

Figure 3. Dual-Lane Interface Timing Diagram

## PARAMETRIC MEASUREMENT INFORMATION (continued)

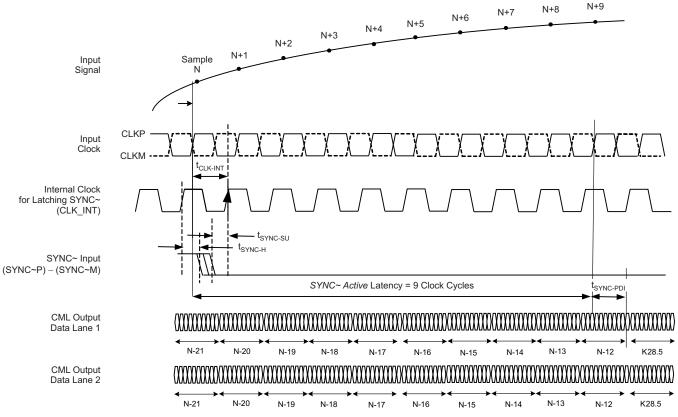

A detailed dual-lane mode timing diagram is shown in Figure 4.

(1) These clock cycles comprise the ADC latency. At higher sampling frequencies, t<sub>PDI</sub> > 1 clock cycle and overall latency = ADC latency + 1.

Figure 4. Dual-Lane Mode Timing Diagram

|                  | PARAMETER              | 30 MSPS | 40 MSPS | 60 MSPS | 160 MSPS | UNIT           |

|------------------|------------------------|---------|---------|---------|----------|----------------|

| T <sub>A</sub>   | Aperture delay         | 560     | 560     | 560     | 560      | ps             |

| TJ               | Aperture jitter (RMS)  | 125     | 125     | 125     | 125      | f <sub>S</sub> |

|                  | Latency                | 20      | 20      | 20      | 20       | Clocks         |

| t <sub>PDI</sub> | Data propagation delay | 33.3    | 26.2    | 18.9    | 15.3     | ns             |

The receiver issues a synchronization request through the SYNC~P, SYNC~M pins whenever the frame boundary of the output data stream must be synchronized to. Figure 5 shows how the transmission switches from normal data (D) to code group synchronization symbols K28.5 symbols during and after a synchronization request.

Figure 5. SYNC~ Active Timing Diagram

Table 2. SYNC~ Falling Edge Timing at 160 MSPS

|                       | PARAMETER                    | DESCRIPTION                                                                                                             | TYP  | UNIT   |

|-----------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------|------|--------|

| t <sub>CLK-INT</sub>  |                              | Delay from the input clock rising edge to the internal clock (CLK_INT) rising edge used to latch the SYNC~ falling edge | 10.5 | ns     |

| t <sub>SYNC-SU</sub>  | SYNC~ active edge setup time | Minimum delay required from SYNC~ falling edge to CLK_INT rising edge                                                   | 2    | ns     |

| t <sub>SYNC-H</sub>   | SYNC~ active edge hold time  | Minimum delay required from CLK_INT rising edge to SYNC~ falling edge                                                   | 2    | ns     |

|                       | SYNC~ active latency         | Number of clocks for K28.5 to appear at the output after a SYNC~ request                                                | 9    | clocks |

| t <sub>SYNC-PDI</sub> | SYNC~ data propagation delay | Similar to data propagation delay                                                                                       | 15.3 | ns     |

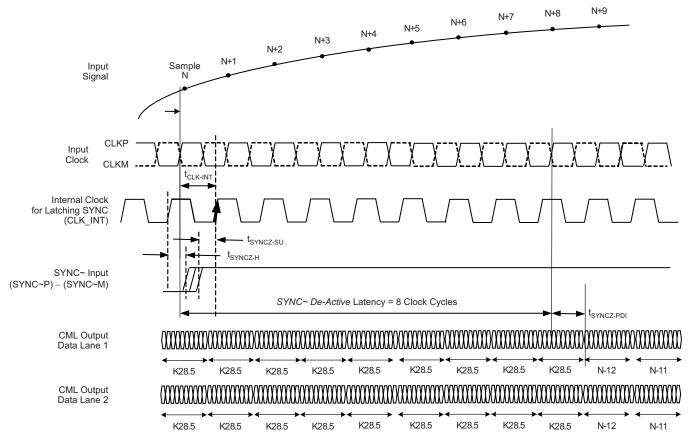

Figure 6. SYNC~ De-Active Timing Diagram

Table 3. SYNC~ Rising Edge Timing at 160 MSPS

|                        | PARAMETER                              | DESCRIPTION                                                                                                        | TYP  | UNIT   |

|------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------|------|--------|

| t <sub>CLK-INT</sub>   |                                        | Delay from input clock rising edge to the internal clock (CLK_INT) rising edge used to latch the SYNC~ rising edge | 10.5 | ns     |

| t <sub>SYNCZ-SU</sub>  | SYNC~ active edge setup time           | Minimum delay required from SYNC~ rising edge to CLK_INT rising edge                                               | 2    | ns     |

| t <sub>SYNCZ-H</sub>   | SYNC~ active edge hold time            | Minimum delay required from CLK_INT rising edge to SYNC~ rising edge                                               | 2    | ns     |

|                        | SYNC~ de-active latency                | Number of clocks for normal data to appear at the output after a SYNC~ de-activate request                         | 8    | Clocks |

| t <sub>SYNCZ-PDI</sub> | SYNC~ de-active data propagation delay | Similar to data propagation delay                                                                                  | 15.3 | ns     |

## **4-LEVEL CONTROL**

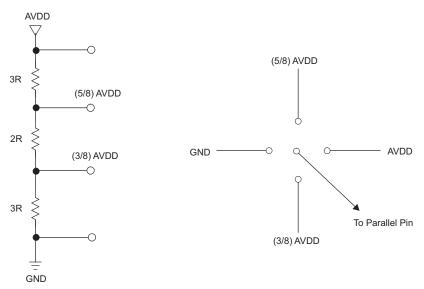

The DFS\_EXTREF and MODE pins function as 4-level control pins in the device, as described in Table 4 and Table 5. A simple scheme to generate a 4-level voltage is shown in Figure 7.

Figure 7. Simple Scheme to Configure 4-Level Control Pins

Table 4. DFS\_EXTREF Pin (Pin 3)

| DFS_EXTREF             | DESCRIPTION         |

|------------------------|---------------------|

| 0<br>+150 mV / 0 mV    | EXTREF = 0, DFS = 0 |

| (3/8) AVDD<br>±150 mV  | EXTREF = 1, DFS = 0 |

| (5/8) AVDD<br>±150 mV  | EXTREF = 1, DFS = 1 |

| AVDD<br>0 mV / –150 mV | EXTREF = 0, DFS = 1 |

Key:

*EXTREF:* 0 = Internal reference mode, 1 = External reference mode

**DFS:** 0 = Twos complement output, 1 = Offset binary output

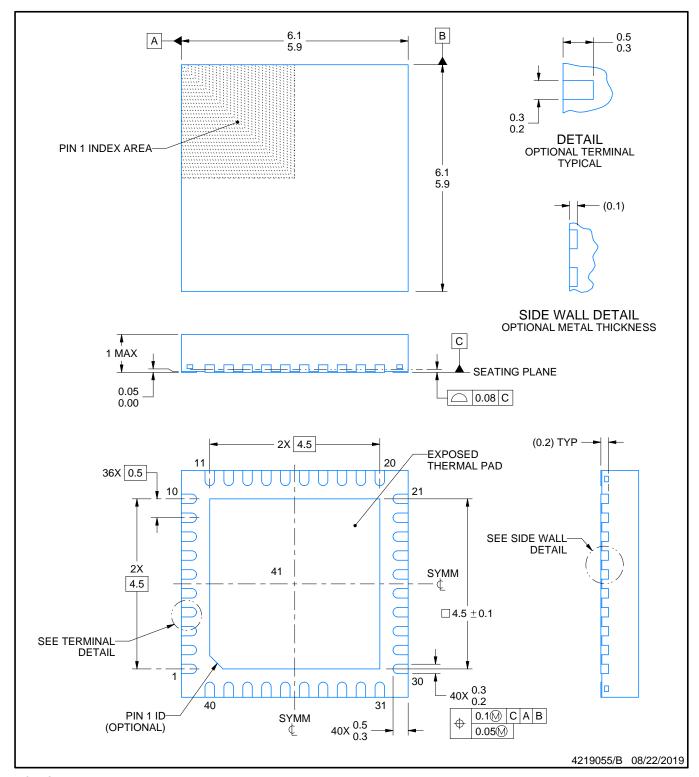

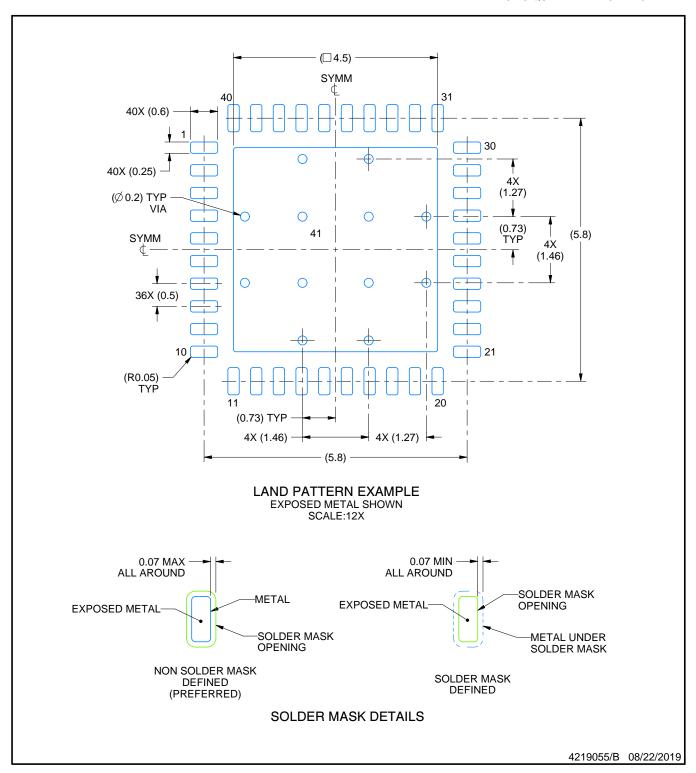

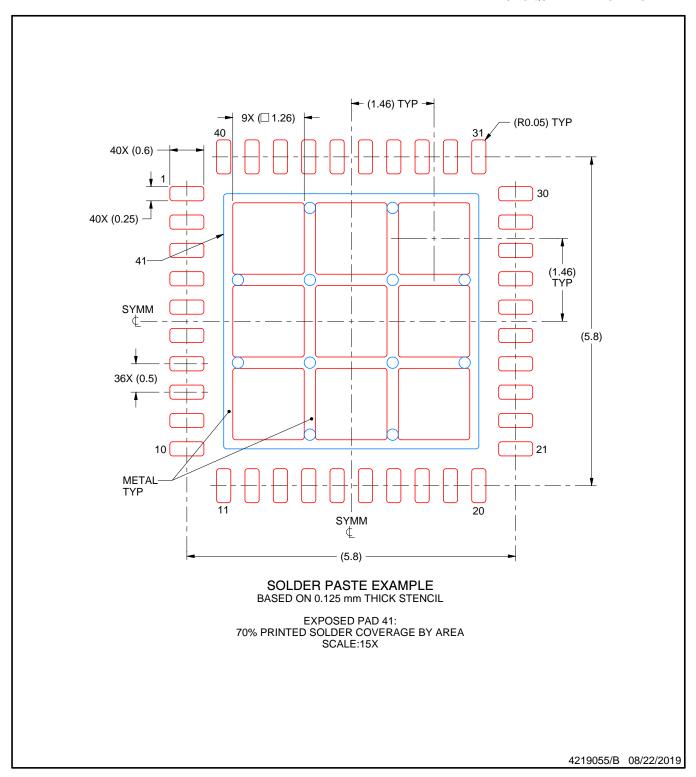

### PIN CONFIGURATION

NOTE: The thermal pad is connected to DRGND.

## **PIN FUNCTIONS**

| Р               | IN                   | PIN FUNCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|-----------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME            | NO.                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| ADC_OUTM0       | 34                   | CML output lane 1, negative output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| ADC_OUTM1       | 31                   | CML output lane 2, negative output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| ADC_OUTP0       | 35                   | CML output lane 1, positive output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| ADC_OUTP1       | 32                   | CML output lane 2, positive output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| AGND            | 5, 6, 9, 11, 14, 16, | Analog ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| AVDD            | 15, 18, 22           | Analog supply, 1.8 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| AVDD_3V         | 17                   | Analog supply for input buffer, 3.3 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| CLKM            | 8                    | Conversion clock, negative input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| CLKP            | 7                    | Conversion clock, positive input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| DETECT3         | 36                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| DETECT2         | 37                   | Signal level-detect output pins in 1.8-V CMOS logic level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| DETECT1         | 38                   | These pins can be used to either output a 4-bit ADC code with low latency or to output a 16-level RMS power estimate.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| DETECT0         | 39                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| DFS_EXTREF      | 3                    | 4-level analog control for data format selection and internal and external reference mode                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| DRGND           | 29                   | Digital ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| DRVDD           | 27, 30               | Digital supply, 1.8 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| FAVDD           | 20                   | Fuse supply, connect externally to AVDD, 1.8 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| INM             | 13                   | Analog input, Negative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| INP             | 12                   | Analog input, Positive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| IOVDD           | 33                   | CML buffer supply, 1.7 V to 1.9 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| MODE            | 19                   | 4-level control for selecting the serial and parallel interface modes                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| OVR             | 40                   | Over-range output in 1.8-V CMOS logic levels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| PDN             | 21                   | Full chip power-down (also referred to as complete power-down mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| PDN_ANA         | 4                    | Analog section power-down; JESD interface is still active. This mode is referred to as fast-recovery power-down mode.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| RESET           | 26                   | Serial interface RESET input. When using the serial interface mode, the internal registers must be initialized through a hardware RESET by applying a high pulse on this pin or by using the S_RESET register bit; refer to the <i>Serial Interface</i> section.  In parallel interface mode, the RESET pin must be permanently tied high. In this mode, the SEN_FALIGN_IDLE, SCLK_SERFO_SCR, and SDATA_TESTO pins function as parallel pins with their functionality described in Table 6, Table 7, and Table 8, respectively. |  |  |  |

| SCLK_SERF0_SCR  | 25                   | Serial clock input in serial interface mode. In parallel interface mode, this pin provides a 4-level control for all JESD modes (single-lane, dual-lane, and scrambling modes).                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| SDATA_TEST0     | 24                   | Serial data input in serial interface mode. In parallel interface mode, this pin provides a JESD test mode.                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| SDOUT_TEST1     | 28                   | Serial data out in serial interface mode. In parallel interface mode, this pin provides a JESD test mode.                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| SEN_FALIGN_IDLE | 23                   | Serial enable input in serial interface mode. In parallel interface mode, this pin provides a 4-level control for JESD modes.                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| SYNC~M          | 1                    | JESD synchronization request, negative input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| SYNC~P          | 2                    | JESD synchronization request, positive input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| VCM             | 10                   | Common-mode output for setting the input common-mode. 1.95 V, reference input in external reference mode.                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

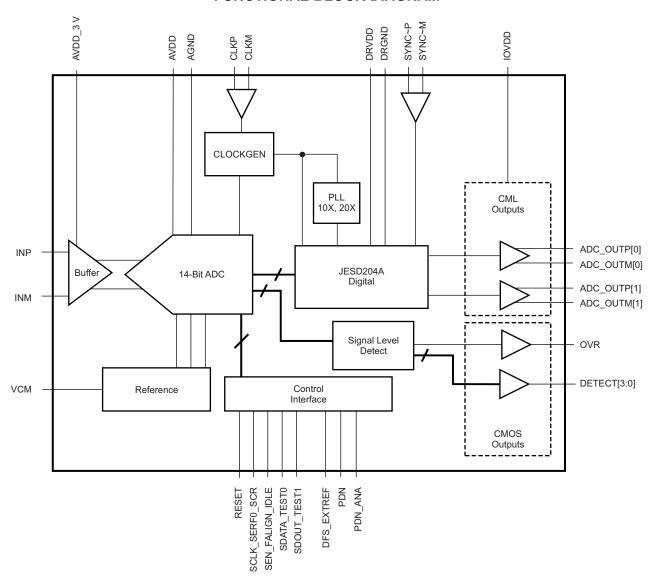

## **FUNCTIONAL BLOCK DIAGRAM**

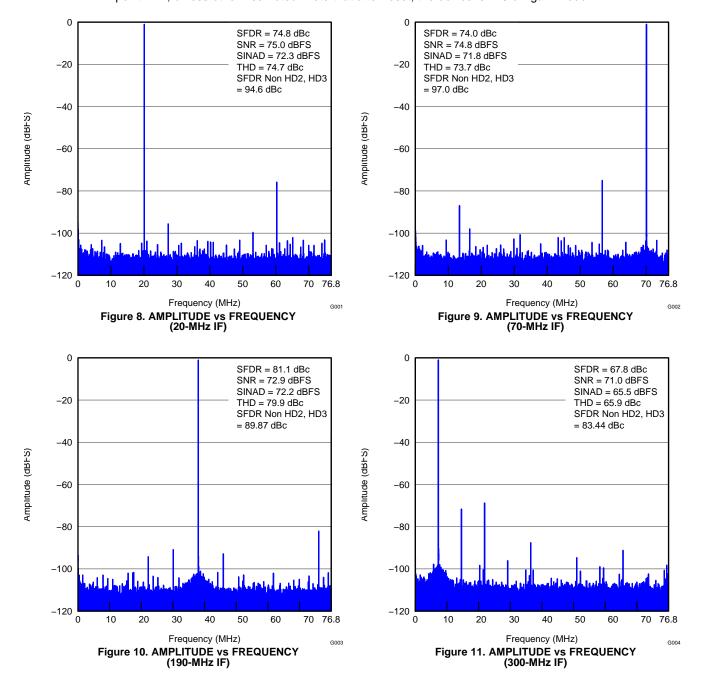

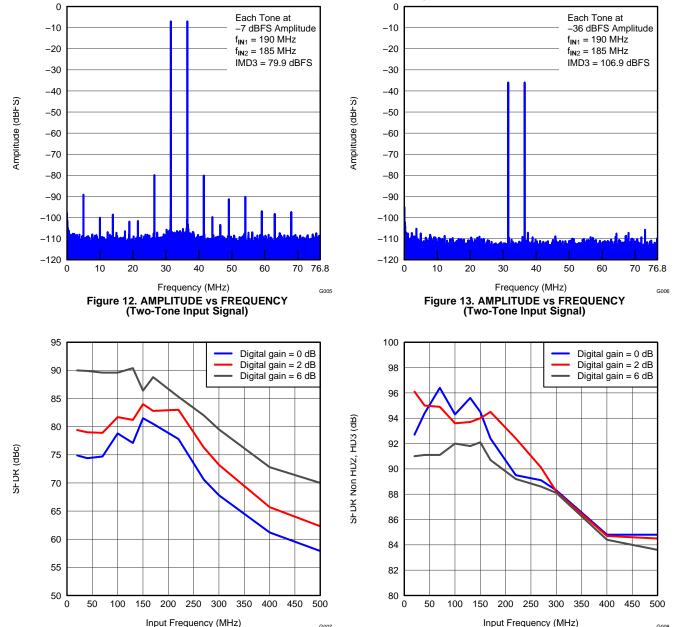

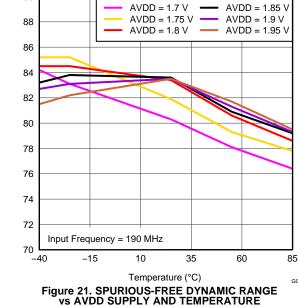

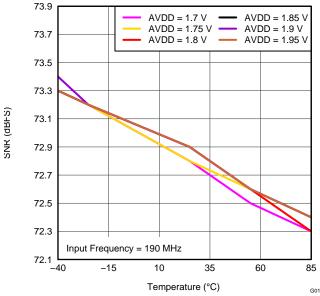

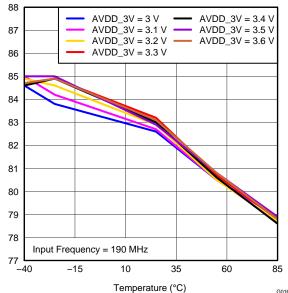

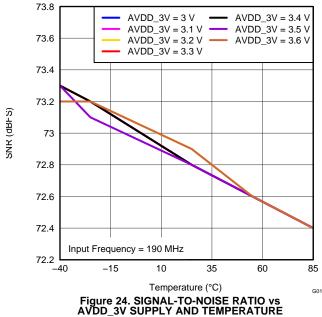

#### TYPICAL CHARACTERISTICS

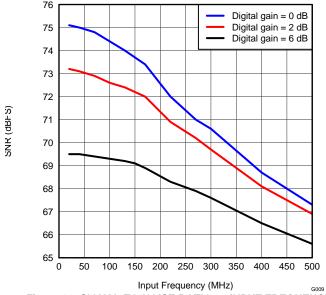

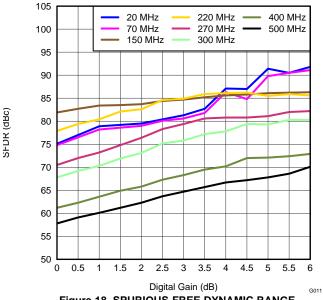

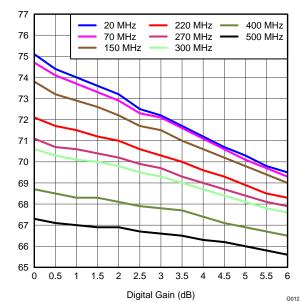

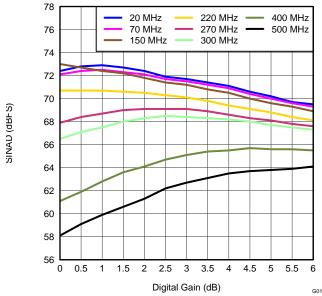

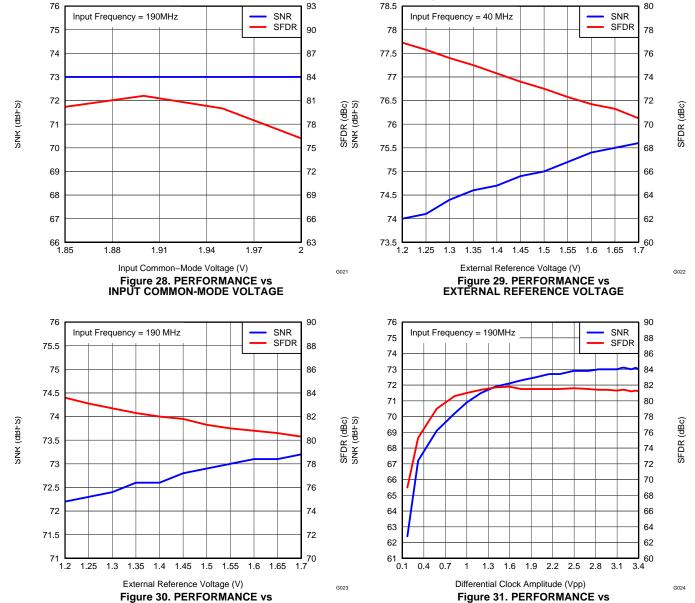

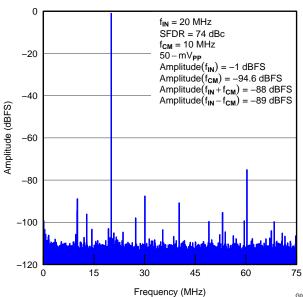

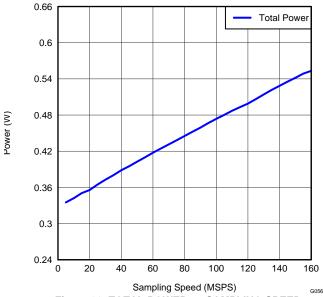

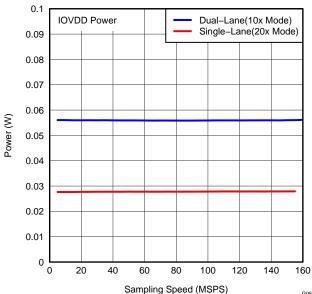

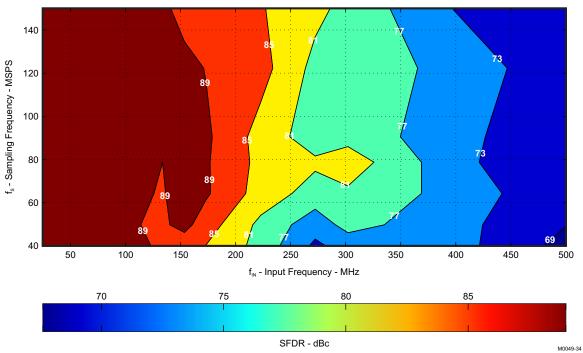

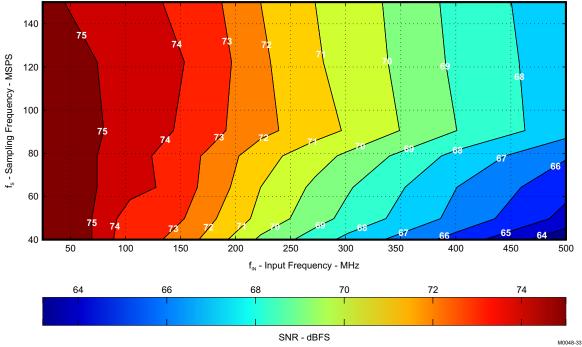

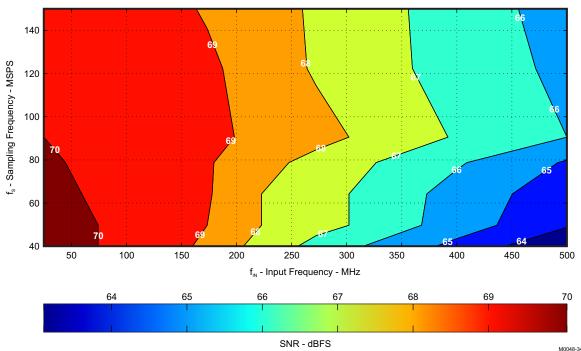

At +25°C, AVDD = 1.8 V, AVDD\_3V = 3.3 V, DRVDD = 1.8 V, IOVDD = 1.8 V,  $f_S$  = 153.6 MSPS, sine-wave input clock, 1.5- $V_{PP}$  differential clock amplitude, 50% clock duty cycle, -1-dBFS differential analog input, 16-mA CML current, and 32k-point FFT, unless otherwise noted. Note that after reset, the device is in 0-dB gain mode.

At +25°C, AVDD = 1.8 V, AVDD\_3V = 3.3 V, DRVDD = 1.8 V, IOVDD = 1.8 V, f<sub>S</sub> = 153.6 MSPS, sine-wave input clock,

1.5-V<sub>PP</sub> differential clock amplitude, 50% clock duty cycle, -1-dBFS differential analog input, 16-mA CML current, and 32k-point FFT, unless otherwise noted. Note that after reset, the device is in 0-dB gain mode.

Figure 14. SPURIOUS-FREE DYNAMIC RANGE vs INPUT FREQUENCY

Figure 15. SPURIOUS-FREE DYNAMIC RANGE (NON HD2, HD3) vs INPUT FREQUENCY

At +25°C, AVDD = 1.8 V, AVDD\_3V = 3.3 V, DRVDD = 1.8 V, IOVDD = 1.8 V,  $f_S$  = 153.6 MSPS, sine-wave input clock,

1.5-V<sub>PP</sub> differential clock amplitude, 50% clock duty cycle, -1-dBFS differential analog input, 16-mA CML current, and 32k-point FFT, unless otherwise noted. Note that after reset, the device is in 0-dB gain mode.

SNR (dBFS)

SNK (dBFS)

130 SNR(dBFS) Input Frequency = 40MHz 120 78 SFDR(dBc) SFDR(dBFS) 77.5 77 100 76.5 90 SFDR (dBc,dBFS) 76 80 70 75.5 60 75 50 74.5 74 40 73.5 30 20 73 72.5 10 -80 -70 -60 -50 -40 -30 -20 -10 0 Amplitude (dBFS) G010

Figure 16. SIGNAL-TO-NOISE RATIO vs INPUT FREQUENCY

Figure 17. PERFORMANCE ACROSS INPUT AMPLITUDE

Figure 18. SPURIOUS-FREE DYNAMIC RANGE vs DIGITAL GAIN

Figure 19. SIGNAL-TO-NOISE RATIO vs DIGITAL GAIN

At +25°C, AVDD = 1.8 V, AVDD\_3V = 3.3 V, DRVDD = 1.8 V, IOVDD = 1.8 V, f<sub>S</sub> = 153.6 MSPS, sine-wave input clock,

1.5-V<sub>PP</sub> differential clock amplitude, 50% clock duty cycle, -1-dBFS differential analog input, 16-mA CML current, and 32kpoint FFT, unless otherwise noted. Note that after reset, the device is in 0-dB gain mode.

Figure 20. SIGNAL-TO-NOISE AND DISTORTION RATIO vs DIGITAL GAIN

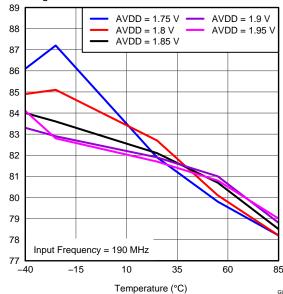

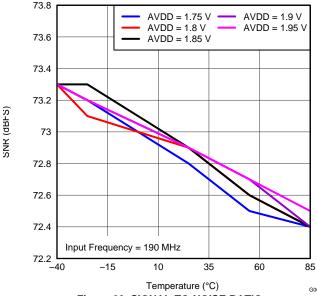

Figure 22. SIGNAL-TO-NOISE RATIO vs **AVDD SUPPLY AND TEMPERATURE**

Figure 23. SPURIOUS-FREE DYNAMIC RANGE vs AVDD\_3V SUPPLY AND TEMPERATURE

SFUR (dBc)

At +25°C, AVDD = 1.8 V, AVDD\_3V = 3.3 V, DRVDD = 1.8 V, IOVDD = 1.8 V, f<sub>S</sub> = 153.6 MSPS, sine-wave input clock,

1.5-V<sub>PP</sub> differential clock amplitude, 50% clock duty cycle, -1-dBFS differential analog input, 16-mA CML current, and 32kpoint FFT, unless otherwise noted. Note that after reset, the device is in 0-dB gain mode.

-40

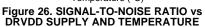

Figure 25. SPURIOUS-FREE DYNAMIC RANGE vs DRVDD SUPPLY AND TEMPERATURE

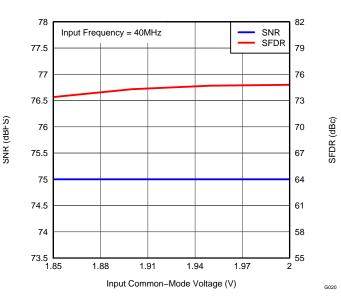

Figure 27. PERFORMANCE vs INPUT COMMON-MODE VOLTAGE

At +25°C, AVDD = 1.8 V, AVDD\_3V = 3.3 V, DRVDD = 1.8 V, IOVDD = 1.8 V, f<sub>S</sub> = 153.6 MSPS, sine-wave input clock,

1.5-V<sub>PP</sub> differential clock amplitude, 50% clock duty cycle, -1-dBFS differential analog input, 16-mA CML current, and 32kpoint FFT, unless otherwise noted. Note that after reset, the device is in 0-dB gain mode.

Submit Documentation Feedback

DIFFERENTIAL CLOCK AMPLITUDE

EXTERNAL REFERENCE VOLTAGE

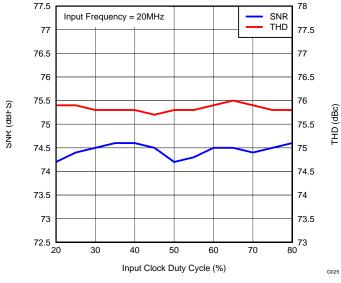

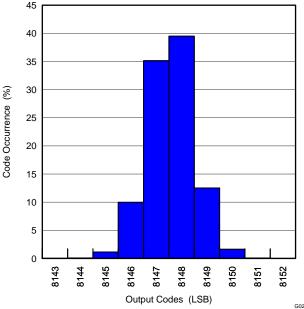

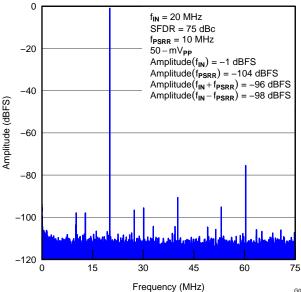

At +25°C, AVDD = 1.8 V, AVDD\_3V = 3.3 V, DRVDD = 1.8 V, IOVDD = 1.8 V, f<sub>S</sub> = 153.6 MSPS, sine-wave input clock,

1.5-V<sub>PP</sub> differential clock amplitude, 50% clock duty cycle, -1-dBFS differential analog input, 16-mA CML current, and 32k-point FFT, unless otherwise noted. Note that after reset, the device is in 0-dB gain mode.

Figure 32. PERFORMANCE vs INPUT CLOCK DUTY CYCLE

Figure 33. OUTPUT CODES HISTOGRAM WITH IDLE CHANNEL INPUT

75 G054

Figure 34. POWER-SUPPLY REJECTION RATIO SPECTRUM FOR AVDD SUPPLY

Figure 35. COMMON-MODE REJECTION RATIO SPECTRUM FOR AVDD SUPPLY

0.3

0.27

0.21

0.18

Power (W)

At +25°C, AVDD = 1.8 V, AVDD\_3V = 3.3 V, DRVDD = 1.8 V, IOVDD = 1.8 V,  $f_S = 153.6$  MSPS, sine-wave input clock,

1.5-V<sub>PP</sub> differential clock amplitude, 50% clock duty cycle, -1-dBFS differential analog input, 16-mA CML current, and 32k-point FFT, unless otherwise noted. Note that after reset, the device is in 0-dB gain mode.

0.12 0.09 0.06 0.03 0 20 40 60 80 100

AVDD Power AVDD 3V Power

DRVDD Power

IOVDD Power

Figure 36. TOTAL POWER vs SAMPLING SPEED

Sampling Speed (MSPS)

Figure 37. POWER BREAK-UP vs SAMPLING SPEED

120

140

160

Figure 38. IOVDD POWER vs SAMPLING SPEED

Copyright © 2013, Texas Instruments Incorporated

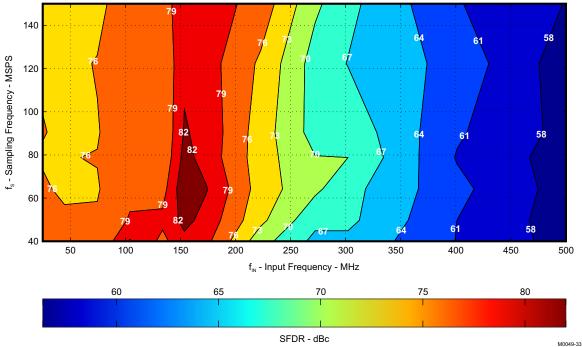

### TYPICAL CHARACTERISTICS: CONTOUR

At +25°C, AVDD = 1.8 V, AVDD\_3V = 3.3 V, DRVDD = 1.8 V, IOVDD = 1.8 V, f<sub>S</sub> = 153.6 MSPS, sine-wave input clock, 1.5-V<sub>PP</sub> differential clock amplitude, 50% clock duty cycle, -1-dBFS differential analog input, 16-mA CML current, and 32k-point FFT, unless otherwise noted. Note that after reset, the device is in 0-dB gain mode.

Figure 39. SFDR ACROSS INPUT AND SAMPLING FREQUENCIES

Figure 40. SFDR ACROSS INPUT AND SAMPLING FREQUENCIES (6-dB Gain)

## TYPICAL CHARACTERISTICS: CONTOUR (continued)

At +25°C, AVDD = 1.8 V, AVDD\_3V = 3.3 V, DRVDD = 1.8 V, IOVDD = 1.8 V,  $f_S$  = 153.6 MSPS, sine-wave input clock,

1.5-V<sub>PP</sub> differential clock amplitude, 50% clock duty cycle, -1-dBFS differential analog input, 16-mA CML current, and 32k-point FFT, unless otherwise noted. Note that after reset, the device is in 0-dB gain mode.

Figure 41. SNR ACROSS INPUT AND SAMPLING FREQUENCIES

Figure 42. SNR ACROSS INPUT AND SAMPLING FREQUENCIES (6-dB Gain)

Copyright © 2013, Texas Instruments Incorporated

#### **DEVICE CONFIGURATION**

#### PARALLEL INTERFACE MODE

The device operates in parallel interface mode when a suitable voltage is applied on the MODE pin, as described in Table 5. In parallel interface mode, the SEN, SDATA, SCLK, and SDOUT pins functionality differs from the serial interface mode. In this mode, the SEN\_FALIGN\_IDLE and SCLK\_SERF0\_SCR pins turn into four level-control pins for the JESD interface (as described in Table 6 and Table 7), whereas the SDATA\_TEST0 and SDOUT\_TEST1 pins turn into 2-level control pins, as described in Table 8.

## Table 5. MODE Pin (Pin 19)

| MODE                  | DESCRIPTION                                                                                                                                                                                                                           |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>+150 mV/–0 mV    | Serial interface mode. Pins 23, 24, and 25 are configured as SEN, SDATA, SCLK. Pins 36, 37, 38, and 39 are configured to output either an early-signal estimate or a signal power estimate (selection is based on register settings). |

| (3/8)AVDD<br>±150 mV  | Do not use                                                                                                                                                                                                                            |

| (5/8)AVDD<br>±150 mV  | Parallel interface mode. Pins 23, 24 and 25 are configured as parallel input pins for controlling the JESD204A modes. Pins 36, 37, 38, and 39 always output an early-signal estimate.                                                 |

| AVDD<br>+0 mV/–150 mV | Do not use                                                                                                                                                                                                                            |

### Table 6. SEN\_FALIGN\_IDLE Pin, in Parallel Interface Mode (Pin 23)

| SEN_FALIGN_IDLE        | DESCRIPTION          |

|------------------------|----------------------|

| 0<br>+150 mV / 0 mV    | FALIGN = 0, IDLE = 0 |

| (3/8) AVDD<br>±150 mV  | FALIGN = 1, IDLE = 0 |

| (5/8) AVDD<br>±150 mV  | FALIGN = 1, IDLE = 1 |

| AVDD<br>0 mV / –150 mV | FALIGN = 0, IDLE = 1 |

Key:

IDLE:

When the last octet of the current frame is the same as the last octet of the previous frame, then FALIGN determines whether the last octet of the current frame is transmitted as is, or if the last octet is replaced by a K28.7 control symbol.

**FALIGN:** Whether the last octet of the cu 0 = Last octet transmitted as is

1 = Last octet is replaced with a K28.7 control symbol

IDLE determines the synchronization characters transmitted during and immediately after a SYNC event.

0 = The device transmits K28.5 as per the JESD204A specification

1 = The device alternately transmits K28.5 and D5.6/D16.2 characters as per the IEEE standard 802.3-2002 (part 3, clause

36.2.4.12). This setting is the case for both single- and dual-lane modes.

## Table 7. SCLK\_SERF0\_SCR Pin, in Parallel Interface Mode (Pin 25)

| SCLK_SERF0_SCR         | DESCRIPTION        |

|------------------------|--------------------|

| 0<br>+150 mV / 0 mV    | SERF0 = 0, SCR = 0 |

| (3/8) AVDD<br>±150 mV  | SERF0 = 1, SCR = 0 |

| (5/8) AVDD<br>±150 mV  | SERF0 = 1, SCR = 1 |

| AVDD<br>0 mV / –150 mV | SERF0 = 0, SCR = 1 |

Key:

SERF0: Output serialization factor.

0 = The device transmits two octets per frame (an entire ADC channel in a single lane) with an output serialization factor of 20

1 = The device transmits one octet per frame (one ADC channel over two lanes) with an output serialization factor of 10

SCR: 0 = Scrambling disabled

1 = Scrambling enabled (as per JESD204A)

## Table 8. SDATA\_TEST0 and SDOUT\_TEST1 Pins, in Parallel Interface Mode (Pins 24 and 28)

| TEST1 | TEST0 | MODE                                                                                                                                             |

|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | 0     | Normal mode. JESD204A encoder input is ADC data.                                                                                                 |

| 0     | 1     | JESD204A encoder input is B5B5. Output is a stream of D21.5 (alternating 1s and 0s).                                                             |

| 1     | 0     | JESD204A encoder input is FF00.                                                                                                                  |

| 1     | 1     | JESD204A encoder input is a pseudo random pattern 1 + X <sup>14</sup> + X <sup>15</sup> (regardless of whether the scrambler is enabled or not). |

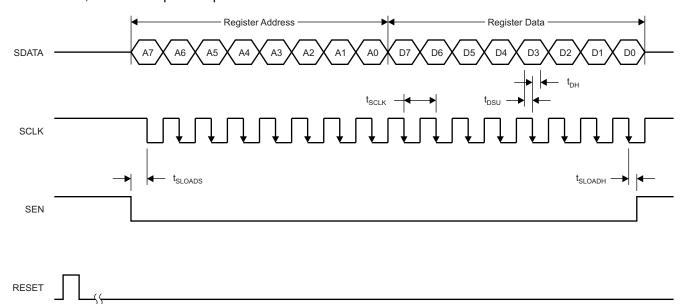

#### SERIAL INTERFACE

The analog-to-digital converter (ADC) has a set of internal registers that can be accessed by the serial interface formed by the serial interface enable (SEN), serial interface clock (SCLK), and serial interface data (SDATA) pins. Serially shifting bits into the device is enabled when SEN is low. SDATA serial data are latched at every SCLK falling edge when SEN is active (low). The serial data are loaded into the register at every 16th SCLK falling edge when SEN is low. If the word length exceeds a multiple of 16 bits, the excess bits are ignored. Data can be loaded in multiples of 16-bit words within a single active SEN pulse.

The first eight bits form the register address and the remaining eight bits are the register data. The interface can function with SCLK frequencies from 20 MHz down to very low speeds (of few Hertz) and also with a non-50% SCLK duty cycle.

#### **Register Initialization**

After power-up, the internal registers must be initialized to the default values. This initialization can be accomplished in one of two ways:

1. Either through a hardware reset by applying a high-going pulse on RESET pin (of widths greater than 10 ns), as shown in Figure 43,

or

2. By applying a software reset. Using the serial interface, set the S\_RESET bit (bit D1 in register 00h) high. This setting initializes the internal registers to the default values and then self-resets the S\_RESET bit low. In this case, the RESET pin is kept low.

Figure 43. Serial Interface Timing Diagram

Table 9. Timing Characteristics for Figure 43<sup>(1)</sup>

|                     | PARAMETER                                | MIN  | TYP | MAX | UNIT |

|---------------------|------------------------------------------|------|-----|-----|------|

| f <sub>SCLK</sub>   | SCLK frequency (= 1/ t <sub>SCLK</sub> ) | > DC |     | 20  | MHz  |

| t <sub>SLOADS</sub> | SEN to SCLK setup time                   | 25   |     |     | ns   |

| t <sub>SLOADH</sub> | SCLK to SEN hold time                    | 25   |     |     | ns   |

| t <sub>DS</sub>     | SDATA setup time                         | 25   |     |     | ns   |

| t <sub>DH</sub>     | SDATA hold time                          | 25   |     |     | ns   |

(1) Typical values are at T<sub>A</sub> = +25°C, minimum and maximum values are across the full temperature range of T<sub>MIN</sub> = -40°C to T<sub>MAX</sub> = +85°C, AVDD = 1.8 V, AVDD\_3V = 3.3 V, DRVDD = 1.8 V, and IOVDD = 1.8 V, unless otherwise noted.

#### **Serial Register Readout**

The device includes an option where the contents of the internal registers can be read back. This readback may be useful as a diagnostic check to verify the serial interface communication between the external controller and the ADC.

- 1. First, set the SERIAL\_READOUT register bit = 1. This setting also disables any further register writes (except for writes to the SERIAL\_READOUT register bit).

- 2. Initiate a serial interface cycle specifying the address of the register (A[7:0]) whose content must be read.

- 3. The device outputs the contents (D[7:0]) of the selected register on the SDOUT\_TEST1 pin.

- 4. The external controller latches the contents at the SCLK falling edge.

- 5. To enable register writes, reset the SERIAL\_READOUT register bit = 0.

## **Reset Timing**

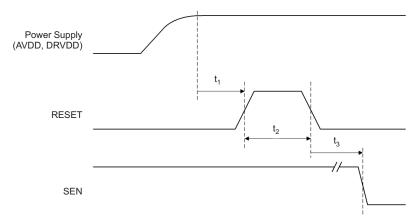

Figure 44 shows a reset timing diagram.

NOTE: A high-going pulse on the RESET pin is required for initialization through a hardware reset.

Figure 44. Reset Timing Diagram

Table 10. Timing Characteristics for Figure 44<sup>(1)</sup>

|                | PARAMETER              | CONDITIONS                                                                 | MIN | TYP | MAX | UNIT |

|----------------|------------------------|----------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>1</sub> | Power-on delay         | Delay from power-up of AVDD and DRVDD to RESET pulse active                |     | 1   |     | ms   |

| t <sub>2</sub> | Reset pulse duration   | Pulse duration of the active RESET signal that resets the serial registers | 10  |     |     |      |

| t <sub>3</sub> | Serial interface delay | Delay from RESET disable to SEN active                                     | 100 |     |     | ns   |

(1) Typical values are at  $T_A = +25$ °C and minimum and maximum values are across the full temperature range of  $T_{MIN} = -40$ °C to  $T_{MAX} = +85$ °C, unless otherwise noted.

## **SERIAL INTERFACE REGISTER MAP**

|                   | BIT LOCATION     |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|-------------------|------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| REGISTER BIT NAME | ADDRESS<br>(Hex) | BIT    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| S_RESET           | 00               | 1      | Software reset. This mode has the same function as a hardware reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| SERIAL_READOUT    | 00               | 0      | 0 = Serial interface write (default) 1 = Serial readout                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| HIGH_SFDR_MODE    | 02               | 6:4, 0 | Set these bits to obtain the best HD3 when the input frequency is between 150 MHz to 250 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| DFS_OVERRIDE      | 3C               | 7      | This bit provides the override control mode for the DFS_EXTREF pin when contro the DFS select mode. This bit controls the DFS_EXTREF pin with the DFS_REG register bit.  0 = DFS functionality determined by DFS_EXTREF pin 1 = DFS functionality determined by DFS_REG pin                                                                                                                                                                                                                                                           |  |  |

| DFS_REG           | 3C               | 6      | This bit is the register bit for DFS control.  0 = Output format is twos complement.  1 = Output format is offset binary. This setting takes effect when DFS_OVERRIDE is set to '1'.                                                                                                                                                                                                                                                                                                                                                  |  |  |

| CUSTOM_PAT[13:6]  | 3E               | 7:0    | Eight MSBs of the 14-bit custom pattern can be programmed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| CUSTOM_PAT[5:0]   | 3F               | 7:2    | Six LSBs of the 14-bit custom pattern can be programmed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| INT_REF_OVERRIDE  | 44               | 3      | This bit is the override control for DFS_EXTREF pin when controlling the internal/external reference select mode. This bit controls the DFS_EXTREF pin with the INT_REF_REG register bit.                                                                                                                                                                                                                                                                                                                                             |  |  |

|                   |                  |        | 0 = Internal/external reference mode is determined by the DFS_EXTREF pin 1 = Internal/external reference mode is determined by the INT_REF_REG                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|                   |                  |        | This bit is the register bit for internal/external reference mode control.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| INT_REF_REG       | 44               | 2      | 0 = Internal reference mode. 1 = External reference mode. This setting takes effect when INT_REF_OVERRIDE is set to '1'.                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| S_PDN             | 44               | 6      | Software power-down.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| FINE_GAIN[3:0]    | 45               | 7:4    | 0-dB to 6-dB digital gain in 0.5-dB steps (default gain is 0 dB). Refer to the <i>Fine-Gain Control</i> section for further details.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| BYPASS_FINE_GAIN  | 45               |        | Digital gain bypass. Digital gain is enabled by default. When this bit set to '1', digital gain (fine gain) is bypassed.                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

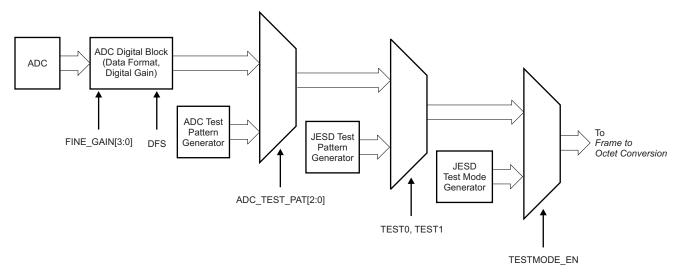

| ADC_TEST_PAT[2:0] | 45               | 2:0    | These bits control the output test patterns.  000 = ADC output data bus is input to JESD204A encoder block  001 = ADC bus is replaced by the minimum code (00000000000000 in offset binary).  010 = ADC bus replaced by the maximum code (111111111111111111111111111111111111                                                                                                                                                                                                                                                        |  |  |

| TXMIT_LINKDATA_EN | A0               | 0      | <ul> <li>0 = Initial lane alignment sequence is not transmitted (default)</li> <li>1 = Initial lane alignment sequence (as per JESD204A) is sent after the code group sync in both single- and dual-lane interfaces</li> </ul>                                                                                                                                                                                                                                                                                                        |  |  |

| S_FALIGN          | AO               | 1      | Software Frame Align control. This bit enables frame alignment monitoring. When scrambling is enabled and this bit is '1', this bit is encoded as K28.7 when the last scrambled octet in a frame equals FC. S_FALIGN bit control is similar to the FALIGN pin control. When this bit is 0 = There is no replacement. 1 = When scrambling is off, if the last octet in the previous frame is the same as the last octet in the current frame, then the last octet in the current frame is replaced with a frame alignment symbol K28.7 |  |  |

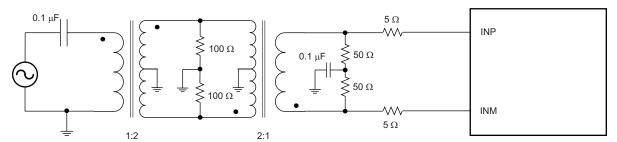

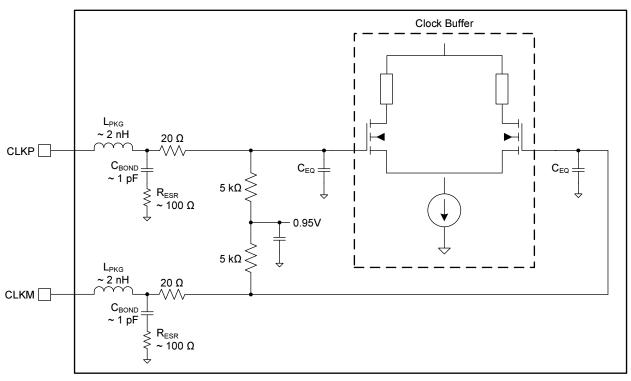

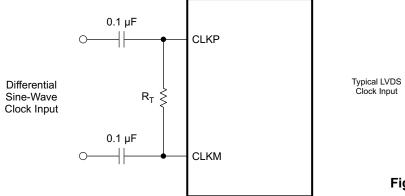

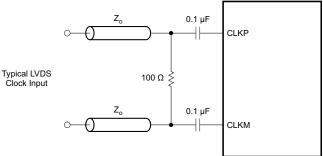

| MFALIGN           | A0               | 2      | Multiframe align control.  This bit functions similarly to S_FALIGN, but refers to multiframe instead.  The multiframe alignment symbol is K28.3.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |