SLAS776E - NOVEMBER 2011 - REVISED APRIL 2018

ADS5294

# ADS5294 Octal-Channel 14-Bit 80-MSPS High-SNR and Low-Power ADC

### **Features**

- Maximum Sample Rate: 80 MSPS/14-Bit

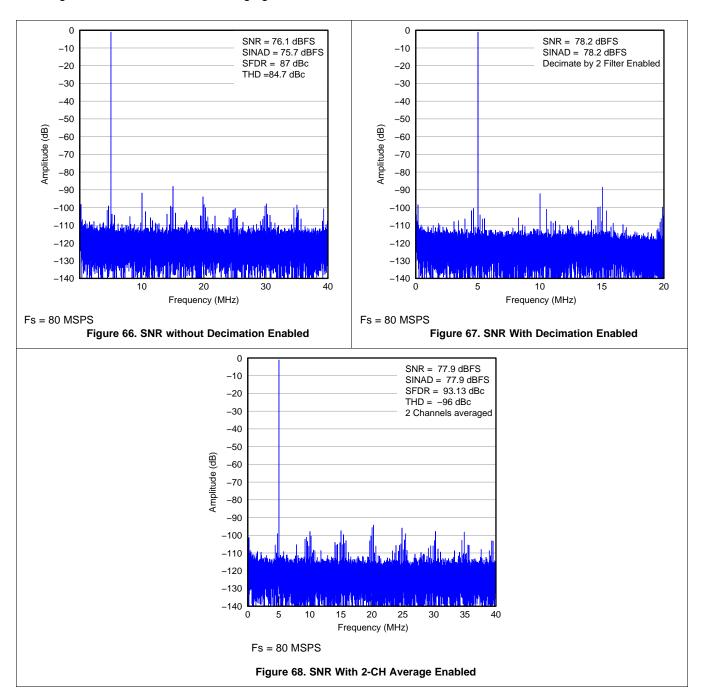

- High Signal-to-Noise Ratio

- 75.5-dBFS SNR at 5 MHz / 80 MSPS

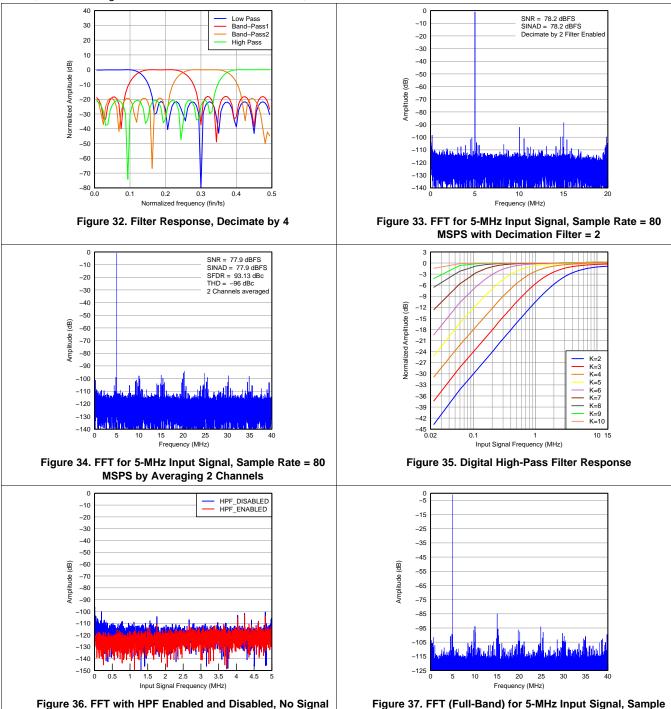

- 78.2-dBFS SNR at 5 MHz / 80 MSPS and **Decimation Filter Enabled**

- 84-dBc SFDR at 5 MHz / 80 MSPS

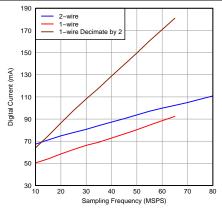

- Low Power Consumption

- 58 mW/CH at 50 MSPS

- 77 mW/CH at 80 MSPS (2-LVDS Wire Per Channel)

- Digital Processing Block

- Programmable FIR Decimation Filter and Oversampling to Minimize Harmonic Interference

- Programmable IIR High-Pass Filter to Minimize DC Offset

- Programmable Digital Gain: 0 dB to 12 dB

- 2-Channel or 4-Channel Averaging

- Flexible Serialized LVDS Outputs:

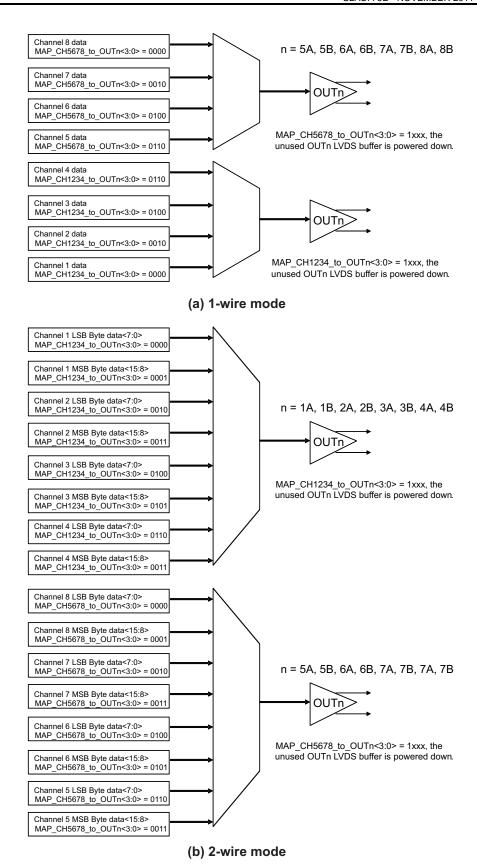

- One or Two Wires of LVDS Output Lines Per Channel Depending on ADC Sampling Rate

- Programmable Mapping Between ADC Input Channels and LVDS Output Pins-Eases Board Design

- Variety of Test Patterns to Verify Data Capture by FPGA/Receiver

- Internal and External References

- 1.8-V Operation for Low Power Consumption

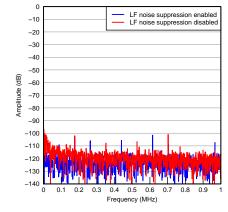

- Low-Frequency Noise Suppression

- Recovery From 6-dB Overload Within 1 Clock

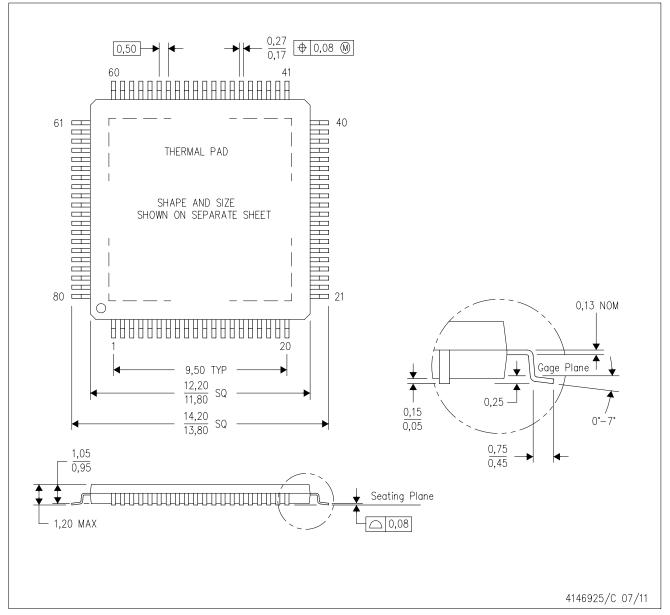

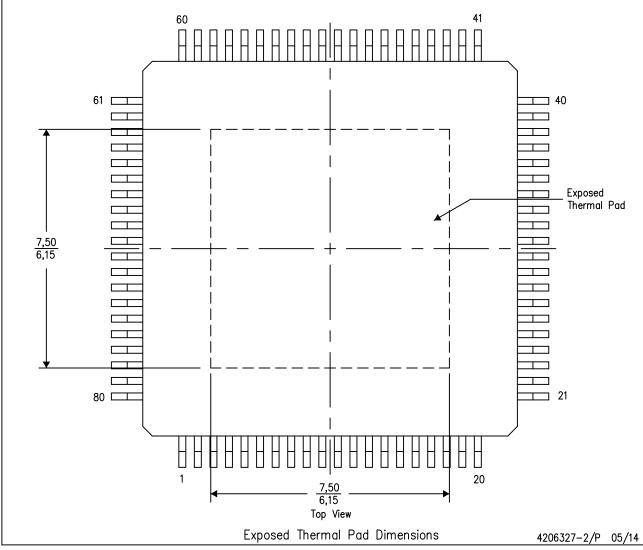

- Package: 12-mm x 12-mm 80-Pin QFP

# **Applications**

- Ultrasound and Sonar Imaging

- **Communication Applications**

- Multi-channel Data Acquisition

# 3 Description

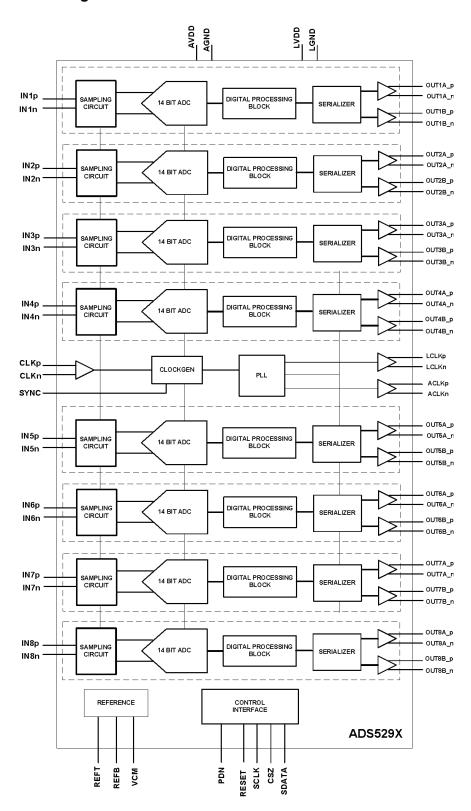

The ADS5294 is a low-power 80-MSPS 8-Channel ADC that uses CMOS process technology and innovative circuit techniques. Low power consumption, high SNR, low SFDR, and consistent overload recovery allow users to design highperformance systems.

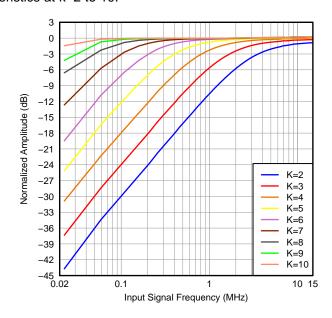

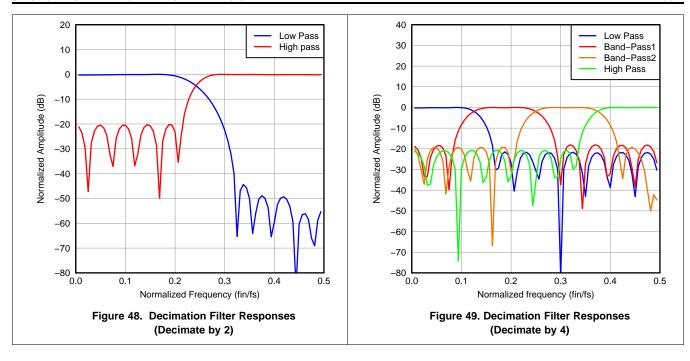

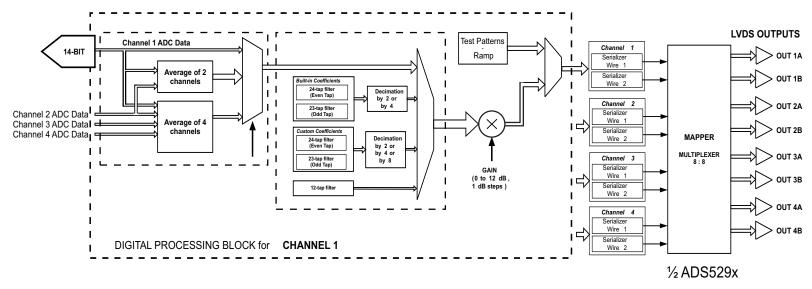

The digital processing block of the ADS5294 integrates several commonly used digital functions for improving system performance. The device includes a digital filter module that has built-in decimation filters (with lowpass, highpass and bandpass characteristics). The decimation rate is programmable (by 2, by 4, or by 8). This rate is useful for narrow-band applications, where the filters are used to conveniently improve SNR and knock-off harmonics, while at the same time reducing the output data rate. The device includes an averaging mode where two channels (or even four channels) are averaged to improve SNR.

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)     |

|-------------|------------|---------------------|

| ADS5294     | HTQFP (80) | 12.00 mm × 12.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

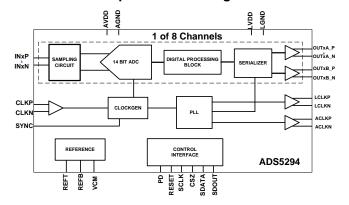

### Simplified Block Diagram

## **Table of Contents**

| 1 | Features 1                                                          |      | Filter Enabled                                                 | 16              |

|---|---------------------------------------------------------------------|------|----------------------------------------------------------------|-----------------|

| 2 | Applications 1                                                      | 8    | 3.14 LVDS Timing at Different Sampling Frequence               |                 |

| 3 | Description 1                                                       |      | 1-Wire Interface, 14x-Serialization, Decimation Filter Enabled |                 |

| 4 | Revision History2                                                   | 5    | 3.15 Typical Characteristics                                   |                 |

| 5 | Description (continued)5                                            |      | Detailed Description                                           |                 |

| 6 | Device Comparison Table 6                                           |      | 9.1 Overview                                                   |                 |

| 7 | Pin Configuration and Functions 7                                   |      | 9.2 Functional Block Diagram                                   |                 |

| 8 | Specifications9                                                     |      | 9.3 Feature Description                                        |                 |

| • | 8.1 Absolute Maximum Ratings                                        |      | 9.4 Device Functional Modes                                    |                 |

|   | 8.2 ESD Ratings9                                                    |      | 9.5 Programming                                                |                 |

|   | 8.3 Recommended Operating Conditions                                |      | 9.6 Register Maps                                              |                 |

|   | 8.4 Thermal Information                                             | 10   | Application and Implementation                                 |                 |

|   | 8.5 Electrical Characteristics Dynamic Performance 11               |      | 10.1 Application Information                                   |                 |

|   | 8.6 Digital Characteristics                                         |      | 10.2 Typical Application                                       |                 |

|   | 8.7 Timing Requirements                                             | 11 I | Power Supply Recommendations                                   |                 |

|   | 8.8 LVDS Timing at Different Sampling Frequencies —                 |      | _ayout                                                         |                 |

|   | 2-Wire Interface, 7x-Serialization, Digital Filter Disabled         |      | 12.1 Layout Guidelines                                         |                 |

|   | 8.9 LVDS Timing at Different Sampling Frequencies —                 |      | 12.2 Layout Example                                            |                 |

|   | 1-Wire Interface, 14x-Serialization, Digital Filter                 | 13 I | Device and Documentation Support                               | <b>7</b> 1      |

|   | Disabled14                                                          |      | 13.1 Device Support                                            |                 |

|   | 8.10 Serial Interface Timing Requirements                           |      | 13.2 Documentation Support                                     | 73              |

|   | 8.11 Reset Timing                                                   |      | 13.3 Community Resources                                       | <b>7</b> 3      |

|   | 8.12 LVDS Timing at Different Sampling Frequencies —                |      | 13.4 Trademarks                                                | <mark>73</mark> |

|   | 1-Wire Interface, 14x-Serialization, Decimation by 2 Filter Enabled | •    | 13.5 Electrostatic Discharge Caution                           | <b>7</b> 3      |

|   | 8.13 LVDS Timing at Different Sampling Frequencies —                |      | 13.6 Glossary                                                  | <mark>73</mark> |

|   | 1-Wire Interface, 14x-Serialization, Decimation by 4                |      | Mechanical, Packaging, and Orderable  nformation               | <b>7</b> 3      |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C | hanges from Revision D (September 2015) to Revision E                                                                  | Page |

|---|------------------------------------------------------------------------------------------------------------------------|------|

| • | Added The maximum limit used for the LVDD current at -40°C is 132 mA table note                                        | 12   |

| • | Added bypass decimation values to the DATA_RATE, FILTERn_RATE, and FILTERn_COEFF_SET columns                           | 33   |

| • | Changed D15 value of ADDR. (HEX) 28 to X                                                                               | 41   |

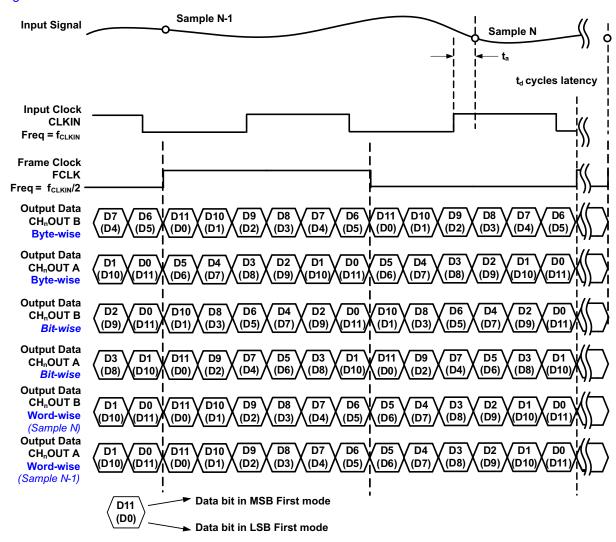

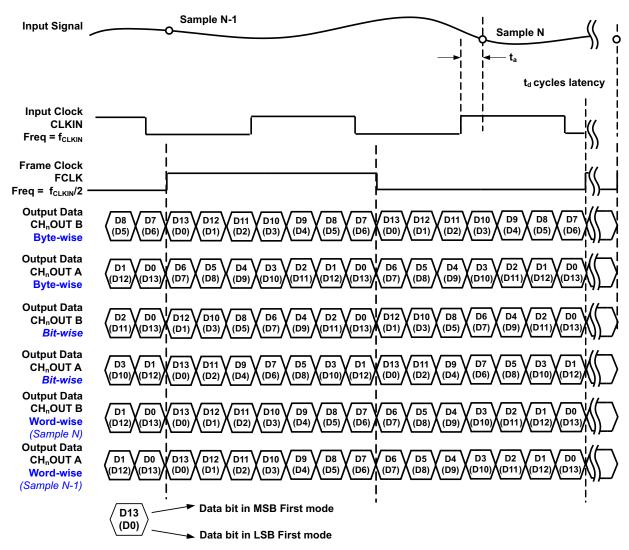

| • | Changed this to the byte-wise for clarification                                                                        | 41   |

| • | Changed this to the word-wise for clarification                                                                        | 41   |

| • | Changed D15 value to 1 in Bit-Byte-Word Wise Output table                                                              | 48   |

| • | Added DATA_RATE>, FILTERn_RATE, and FILTERn_COEFF_SET values to the bypass decimation row in the Digital Filters table | 55   |

|   |                                                                                                                        |      |

# Changes from Revision C (September 2013) to Revision D

Page

| • | Added Pin Configuration and Functions section, ESD Ratings table, Feature Description section, Device Functional |      |

|---|------------------------------------------------------------------------------------------------------------------|------|

|   | Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device      |      |

|   | and Documentation Support section, and Mechanical, Packaging, and Orderable Information section                  | 1    |

| • | Added "Sonar Imaging" in Applications                                                                            | 1    |

| • | Updated Pinout                                                                                                   | 7    |

|   | Added text note 2 to Figure 1                                                                                    |      |

| • | Added a text note to Figure 44.                                                                                  | . 30 |

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

| •  | Corrected typo in Table 1                                                                                                                                                                                                                              | 33       |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| •  | Added note to EN_2WIRE bit                                                                                                                                                                                                                             | 44       |

| •  | Corrected typo in Table 17                                                                                                                                                                                                                             | 55       |

| ۵. |                                                                                                                                                                                                                                                        | _        |

| Cr | nanges from Revision B (July 2012) to Revision C                                                                                                                                                                                                       | Page     |

| •  | Added cross-reference link for VCM pin                                                                                                                                                                                                                 | <b>7</b> |

| •  | Added note for REFB pin under INT/EXT reference modes.                                                                                                                                                                                                 |          |

| •  | Added note for REFT pin under INT/EXT reference modes.                                                                                                                                                                                                 | 8        |

| •  | Changed the maximum rating of digital input pins RESET, SCLK, SDATA, SYNC, PD, CSZ to 3.6V                                                                                                                                                             | 9        |

| •  | Added test condition "Digital Filter Disabled" and changed "LVDS output rate" to "ADC CLK Frequency" in LVDS Timing at Different Sampling Frequencies — 2-Wire Interface, 7x-Serialization, Digital Filter Disabled                                    | 14       |

| •  | Added test condition "Digital Filter Disabled" and changed "LVDS output rate" to "ADC CLK Frequency" in LVDS Timing at Different Sampling Frequencies — 1-Wire Interface, 14x-Serialization, Digital Filter Disabled                                   | 14       |

| •  | Added note after LVDS Timing at Different Sampling Frequencies — 1-Wire Interface, 14x-Serialization, Digital Filter Disabled: The above LVDS timing spec is only valid when digital filters are disabled                                              | 14       |

| •  | Added LVDS Timing at Different Sampling Frequencies — 1-Wire Interface, 14x-Serialization, Decimation by 2 Filter                                                                                                                                      |          |

|    | Enabled                                                                                                                                                                                                                                                |          |

| •  | Added LVDS Timing at Different Sampling Frequencies — 1-Wire Interface, 14x-Serialization, Decimation by 4 Filter Enabled                                                                                                                              | 16       |

| •  | Added LVDS Timing at Different Sampling Frequencies — 1-Wire Interface, 14x-Serialization, Decimation by 8 Filter Enabled                                                                                                                              |          |

| •  | Added a note related to EN_CUSTOM_FILT and changed formats in Table 9.                                                                                                                                                                                 |          |

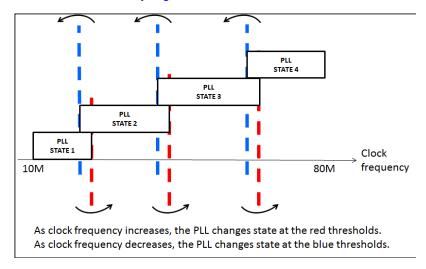

| •  | Added PLL Operation Versus LVDS Timing before APPLICATION INFORMATION section                                                                                                                                                                          | 35       |

| •  | Added a note link to Reg.0x38                                                                                                                                                                                                                          |          |

| •  | Changed 0xF[15] to 0xF0[15] in the description of Reg.0x42.                                                                                                                                                                                            | 44       |

| •  | Changed the Reg.0x46[11:8] formatting.                                                                                                                                                                                                                 | 44       |

| •  | Corrected the EN_RAMP address from 0x24 to 0x25 in the section of LVDS test patterns                                                                                                                                                                   | 47       |

| •  | Changed "Note that these bits are functional only when the GLOBAL_EN_FILTER gets set to 1" to " Note that these bits are functional only when the GLOBAL_EN_FILTER gets set to 1 and USE_FILTERn bit is set to 1" in the section of Decimation Filter. |          |

|    | Added a note related to EN_CUSTOM_FILT and changed formats inTable 17                                                                                                                                                                                  |          |

| •  | Changed Equation (5).                                                                                                                                                                                                                                  |          |

| •  | Added register address in Table 23.                                                                                                                                                                                                                    |          |

| •  |                                                                                                                                                                                                                                                        |          |

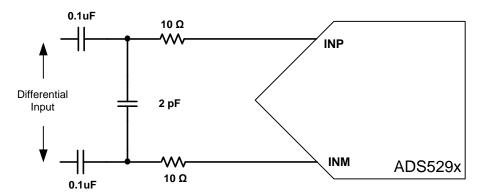

| •  | Revised Figure 63 and moved the 2pF cap to the left hand side of the resistors.                                                                                                                                                                        |          |

| _  | Added a note regarding the location of LVDS Rterm in the section of Input clock.                                                                                                                                                                       | 07       |

| Cr | nanges from Revision A (November 2011) to Revision B                                                                                                                                                                                                   | Page     |

| •  | Changed the location of OUT A and OUT B in Figure 5 and Figure 6                                                                                                                                                                                       | 20       |

| •  | Added Figure 45                                                                                                                                                                                                                                        | 31       |

| •  | Replaced Table 9 (Decimation Filter Modes) with new Table 1 - Digital Filters                                                                                                                                                                          | 33       |

| •  | Deleted section: Synchronization Pulse                                                                                                                                                                                                                 | 35       |

| •  | Added EN_HIGH_ADDRS to Table 3                                                                                                                                                                                                                         | 40       |

| •  | Moved EN_EXT_REF From: 0x0F To: 0xF0 in Table 3                                                                                                                                                                                                        |          |

| •  | Added the section BIT-BYTE-WORD WISE OUTPUT. Added Figure 53 and Figure 54                                                                                                                                                                             |          |

| •  | Added section DIGITAL PROCESSING BLOCKS                                                                                                                                                                                                                |          |

| •  | Replaced Table 5 and Table 6 with new Table 17 - Digital Filters                                                                                                                                                                                       |          |

| •  | Changed the SYNCHRONIZATION PULSE section                                                                                                                                                                                                              |          |

|    |                                                                                                                                                                                                                                                        |          |

### **ADS5294**

| SLAS776E - NOVEMBER 2011 - REVISED APRIL 2018          | www.ti.con |

|--------------------------------------------------------|------------|

| Added the External Reference Mode of Operation section | 59         |

| Changes from Original (November 2011) to Revision A    | Page       |

| Changed From: Product Preview To: Production           |            |

### 5 Description (continued)

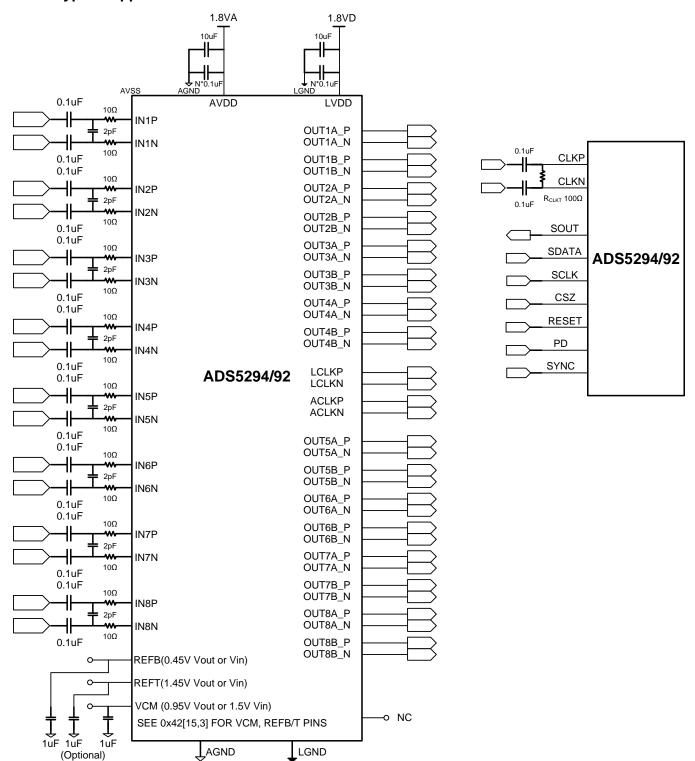

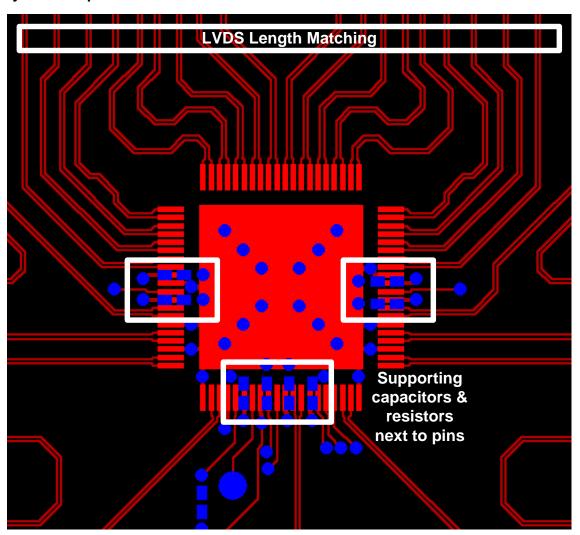

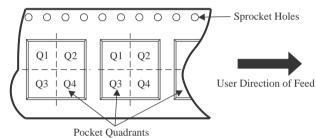

Serial LVDS outputs reduce the number of interface lines and enable the highest system integration. The digital data from each channel ADC is output over one or two wires of LVDS output lines depending on the ADC sampling rate. This 2-wire interface maintains a low serial-data rate, allowing low-cost FPGA-based receivers to be used even at a high sample rate. The ADC resolution is programmed to 12-bit or 14-bit through registers. A unique feature is the programmable-mapping module that allows flexible mapping between the input channels and the LVDS output pins. This module greatly reduces the complexity of LVDS-output routing, and by reducing the number of PCB layers, potentially results in cheaper system boards.

The device integrates an internal reference trimmed to accurately match across devices. Internal reference mode achieves the best performance. External references can also drive the device.

The device is available in a 12-mm × 12-mm 80-pin QFP package. The device is specified over a –40°C to 85°C operating temperature range. ADS5294 is completely pin-to-pin and register compatible to ADS5292.

# 6 Device Comparison Table

| DEVICE   | DESCRIPTION                                                                                                                         | PACKAGE     | BODY SIZE (NOM)     |

|----------|-------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------|

| ADS5294  | Octal-channel, 14-bit, 80-MSPS ADC, 75-dBFS SNR, 77 mW/ch                                                                           | HTQFP (80)  | 14.00 mm × 14.00 mm |

| ADS5292  | Octal-channel, 12-bit, 80-MSPS ADC, 70-dBFS SNR, 66 mW/ch                                                                           | HTQFP (80)  | 14.00 mm × 14.00 mm |

| ADS5295  | Octal-channel, 12-bit, 100-MSPS ADC, 70.6-dBFS SNR, 80 mW/ch                                                                        | HTQFP (80)  | 14.00 mm × 14.00 mm |

| ADS5296A | 10-bit, 200-MSPS, 4-channel, 61-dBFS SNR, 150-mW/ch and 12-bit, 80-MSPS, 8-channel, 70-dBFS SNR, 65-mW/ch ADC                       | VQFN (64)   | 9.00 mm × 9.00 mm   |

| AFE5801  | 8-channel variable-gain amplifier (VGA) with octal high-speed ADC, 5.5 nV/\Hz, 12 bits, 65 MSPS, 65 mW/ch                           | VQFN (64)   | 9.00 mm × 9.00 mm   |

| AFE5803  | 8-channel AFE, 0.75 nV/√Hz, 14 and 12 bits, 65 MSPS, 158 mW/ch                                                                      | NFBGA (135) | 15.00 mm × 9.00 mm  |

| AFE5804  | 8-channel AFE, 1.23 nV/√Hz, 12 bits, 50 MSPS, 101 mW/ch                                                                             | NFBGA (135) | 15.00 mm × 9.00 mm  |

| AFE5805  | 8-channel AFE, 0.85 nV/√Hz, 12 bits, 50 MSPS, 122 mW/ch                                                                             | NFBGA (135) | 15.00 mm × 9.00 mm  |

| AFE5807  | 8-channel AFE with passive CW mixer, 1.05 nV/\(\overline{Hz}\), 12 bits, 80 MSPS, 117 mW/ch                                         | NFBGA (135) | 15.00 mm × 9.00 mm  |

| AFE5808A | 8-channel AFE with passive CW mixer, 0.75 nV/√Hz, 14 and 12 bits, 65 MSPS, 158 mW/ch                                                | NFBGA (135) | 15.00 mm × 9.00 mm  |

| AFE5809  | 8-channel AFE with passive CW mixer, and digital I/Q demodulator, 0.75 nV/√Hz, 14 and 12 bits, 65 MSPS, 158 mW/ch                   | NFBGA (135) | 15.00 mm × 9.00 mm  |

| AFE5812  | Fully integrated, 8-channel AFE with passive CW mixer, and digital I/Q demodulator, 0.75 nV/\Hz, 14 and 12 bits, 65 MSPS, 180 mW/ch | NFBGA (135) | 15.00 mm × 9.00 mm  |

| AFE5818  | 16-Channel AFE with 124-mW/Channel, 0.75-nV/√Hz Noise, 14-Bit, 65-MSPS or 12-Bit, 80-MSPS ADC, and Passive CW Mixer                 | NFBGA (289) | 15.00 mm × 15.00 mm |

| AFE5816  | 16-channel AFE with 90-mW/channel, 1-nV/√Hz noise, 14-bit, 65-MSPS or 12-bit, 80-MSPS ADC and passive CW mixer                      | NFBGA (289) | 15.00 mm × 15.00 mm |

| AFE5851  | 16-channel VGA with high-speed ADC, 5.5 nV/\Hz, 12 bits, 32.5 MSPS, 39 mW/ch                                                        | VQFN (64)   | 9.00 mm × 9.00 mm   |

| VCA8500  | 8-channel, ultralow-power VGA with low-noise pre-amp, 0.8 nV/√Hz, 65 mW/ch                                                          | VQFN (64)   | 9.00 mm × 9.00 mm   |

| VCA5807  | 8-channel voltage-controlled amplifier with passive CW mixer, 0.75 nV/√Hz, 99 mW/ch                                                 | HTQFP (80)  | 14.00 mm × 14.00 mm |

| PGA5807A | Integrated 8-channel AFE with LNA, PGA, and LPF,2.1 nV/\(\sqrt{Hz}\), 60 mW/ch                                                      | VQFN (64)   | 9.00 mm × 9.00 mm   |

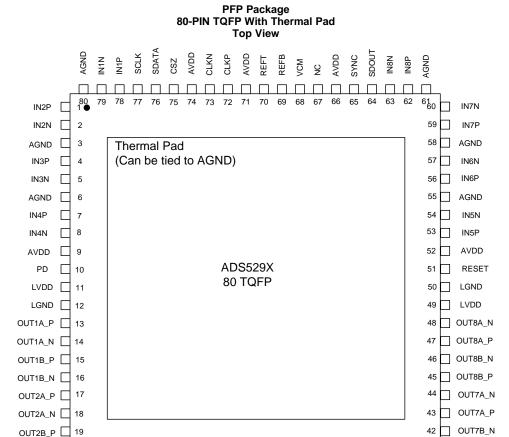

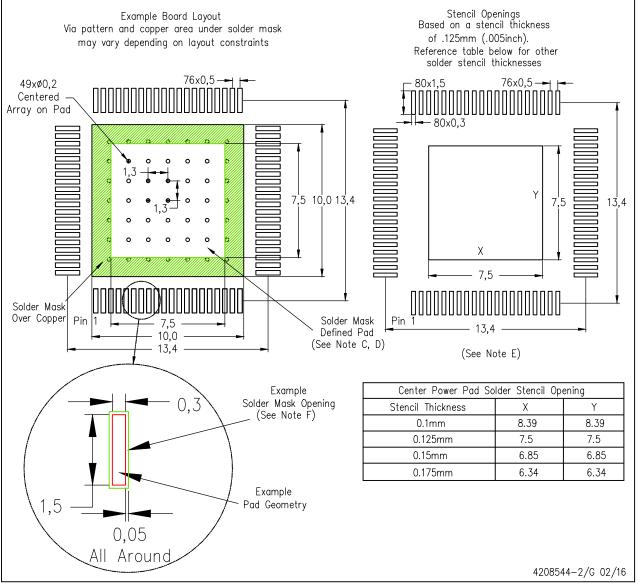

# 7 Pin Configuration and Functions

**Pin Functions**

30 31

LCLKN OUT5B\_P OUT5B\_N

32 33 34

35 36

OUT5A\_P OUT5A\_N

28 29

| F            | PIN                  |                                                                                                                                                                                       |  |

|--------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME         | NO.                  | DESCRIPTION                                                                                                                                                                           |  |

| AVDD         | 9, 52, 66, 71, 74    | Analog power supply, 1.8 V                                                                                                                                                            |  |

| AGND         | 3, 6, 55, 58, 61, 80 | Analog ground                                                                                                                                                                         |  |

| VCM          | 68                   | Common-mode output pin, 0.95-V output. This pin can be configured as the external reference voltage (1.5 V) input pin as well. See Reg 0x42 and External Reference Mode of Operation. |  |

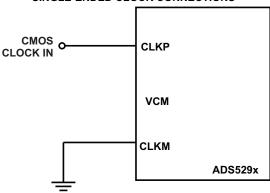

| CLKN         | 73                   | Negative differential clock –Tie CLKN to GND for single-ended clock                                                                                                                   |  |

| CLKP         | 72                   | Positive differential clock                                                                                                                                                           |  |

| IN1P, IN1N   | 78, 79               | Differential input signal, Channel 1                                                                                                                                                  |  |

| IN2P, IN2N   | 1, 2                 | Differential input signal, Channel 2                                                                                                                                                  |  |

| IN3P, IN3N   | 4, 5                 | Differential input signal, Channel 3                                                                                                                                                  |  |

| IN4P, IN4N   | 7, 8                 | Differential input signal, Channel 4                                                                                                                                                  |  |

| IN5P, IN5N   | 53, 54               | Differential input signal, Channel 5                                                                                                                                                  |  |

| IN6P, IN6N   | 56, 57               | Differential input signal, Channel 6                                                                                                                                                  |  |

| IN7P, IN7N   | 59, 60               | Differential input signal, Channel 7                                                                                                                                                  |  |

| IN8P, IN8N   | 62, 63               | Differential input signal, Channel 8                                                                                                                                                  |  |

| LCLKP, LCLKN | 31, 32               | Differential LVDS bit clock (7X)                                                                                                                                                      |  |

| ACLKP, ACLKN | 29, 30               | Differential LVDS frame clock (1X)                                                                                                                                                    |  |

Product Folder Links: ADS5294

41 39 40

OUT6A\_N

OUT6B\_N OUT6A\_P

OUT6B\_P

OUT7B\_P

OUT2B\_N  $\square$   $^{20}_{21}$

22 23 24 25 26 27

OUT4A\_P

OUT4A\_N

OUT4B\_P

OUT4B\_N

# Pin Functions (continued)

| PI               | N      |                                                                                                                                                                                                                                                                                                                                        |

|------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME             | NO.    | DESCRIPTION                                                                                                                                                                                                                                                                                                                            |

| OUT1A_P, OUT1A_N | 13, 14 | Differential LVDS data output, wire 1, channel 1                                                                                                                                                                                                                                                                                       |

| OUT1B_P, OUT1B_N | 15, 16 | Differential LVDS data output, wire 2, channel 1                                                                                                                                                                                                                                                                                       |

| OUT2A_P, OUT2A_N | 17, 18 | Differential LVDS data output, wire 1, channel 2                                                                                                                                                                                                                                                                                       |

| OUT2B_P, OUT2B_N | 19, 20 | Differential LVDS data output, wire 2, channel 2                                                                                                                                                                                                                                                                                       |

| OUT3A_P, OUT3A_N | 21, 22 | Differential LVDS data output, wire 1, channel 3                                                                                                                                                                                                                                                                                       |

| OUT3B_P, OUT3B_N | 23, 24 | Differential LVDS data output, wire 2, channel 3                                                                                                                                                                                                                                                                                       |

| OUT4A_P, OUT4A_N | 25, 26 | Differential LVDS data output, wire 1, channel 4                                                                                                                                                                                                                                                                                       |

| OUT4B_P, OUT4B_N | 27, 28 | Differential LVDS data output, wire 2, channel 4                                                                                                                                                                                                                                                                                       |

| OUT5A_P, OUT5A_N | 35, 36 | Differential LVDS data output, wire 1, channel 5                                                                                                                                                                                                                                                                                       |

| OUT5B_P, OUT5B_N | 33, 34 | Differential LVDS data output, wire 2, channel 5                                                                                                                                                                                                                                                                                       |

| OUT6A_P, OUT6A_N | 39, 40 | Differential LVDS data output, wire 1, channel 6                                                                                                                                                                                                                                                                                       |

| OUT6B_P, OUT6B_N | 37, 38 | Differential LVDS data output, wire 2, channel 6                                                                                                                                                                                                                                                                                       |

| OUT7A_P, OUT7A_N | 43, 44 | Differential LVDS data output, wire 1, channel 7                                                                                                                                                                                                                                                                                       |

| OUT7B_P, OUT7B_N | 41, 42 | Differential LVDS data output, wire 2, channel 7                                                                                                                                                                                                                                                                                       |

| OUT8A_P, OUT8A_N | 47, 48 | Differential LVDS data output, wire 1, channel 8                                                                                                                                                                                                                                                                                       |

| OUT8B_P, OUT8B_N | 45, 46 | Differential LVDS data output, wire 2, channel 8                                                                                                                                                                                                                                                                                       |

| PD               | 10     | Power-down control input. Active High. The pin has an internal 220-kΩ pulldown resistor.                                                                                                                                                                                                                                               |

| REFB             | 69     | Negative reference input and output. Internal reference mode: Reference bottom voltage (0.45 V) is output on this pin. A decoupling capacitor is not required on this pin. External reference mode: Reference bottom voltage (0.45 V) must be externally applied to this pin. Please see <i>External Reference Mode of Operation</i> . |

| REFT             | 70     | Positive reference input and output. Internal reference mode: Reference top voltage (1.45 V) is output on this pin. A decoupling capacitor is not required on this pin. External reference mode: Reference top voltage (1.45 V) must be externally applied to this pin. Please see <i>External Reference Mode of Operation</i> .       |

| RESET            | 51     | Active HIGH RESET input. The pin has an internal 220-kΩ pulldown resistor.                                                                                                                                                                                                                                                             |

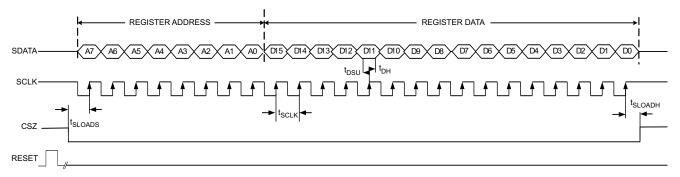

| SCLK             | 77     | Serial clock input. The pin has an internal 220-k $\Omega$ pulldown resistor.                                                                                                                                                                                                                                                          |

| SDATA            | 76     | Serial data input. The pin has an internal 220-k $\Omega$ pulldown resistor.                                                                                                                                                                                                                                                           |

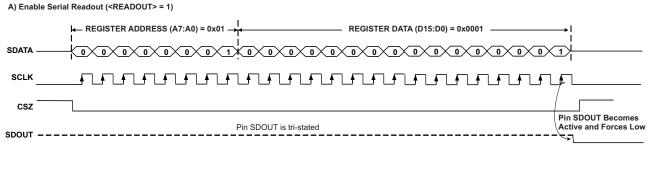

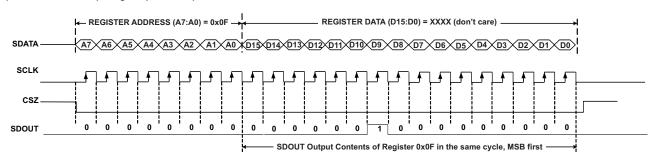

| SDOUT            | 64     | Serial data readout. This pin is in the high-impedance state after reset. When the <readout> bit is set, the SDOUT pin becomes active. SDOUT is a CMOS digital output running from the AVDD supply.</readout>                                                                                                                          |

| CSZ              | 75     | Serial enable chip select – active-low digital input                                                                                                                                                                                                                                                                                   |

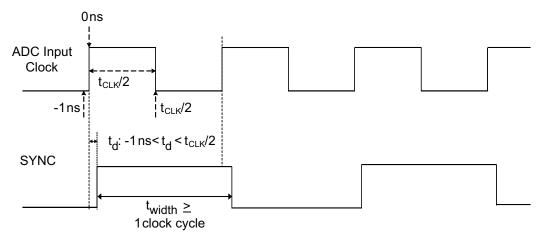

| SYNC             | 65     | Input signal to synchronize channels and chips when used with reduced output data rates. If it is not used, add a $\leq$ 10-K $\Omega$ pulldown resistor.                                                                                                                                                                              |

| LVDD             | 11, 49 | Digital and I/O power supply, 1.8 V                                                                                                                                                                                                                                                                                                    |

| LGND             | 12, 50 | Digital ground                                                                                                                                                                                                                                                                                                                         |

| NC               | 67     | No Connection. Must leave floated                                                                                                                                                                                                                                                                                                      |

Product Folder Links: ADS5294

DITIIL DOCUMENTATION FEEDDACK

# 8 Specifications

# 8.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                                                      | MIN  | MAX                   | UNIT |

|------------------|------------------------------------------------------|------|-----------------------|------|

| Completed        | AVDD                                                 | -0.3 | 2.2                   | V    |

| Supply voltage   | LVDD                                                 | -0.3 | 2.2                   | V    |

|                  | Between AGND and LGND                                | -0.3 | 0.3                   | V    |

|                  | At analog inputs                                     | -0.3 | min[2.2,<br>AVDD+0.3] | V    |

| Voltage          | At digital inputs, RESET, SCLK, SDATA, SYNC, PD, CSZ | -0.3 | 3.6                   | V    |

| vollage          | At CLKN, CLKP <sup>(2)</sup> ,                       | -0.3 | min[2.2,<br>AVDD+0.3] | V    |

|                  | At digital outputs                                   | -0.3 | min[2.2,<br>LVDD+0.3] | V    |

| Maximum junction | on temperature (T <sub>J</sub> ), any condition      |      | 105                   | °C   |

| Operating temper | erature                                              | -40  | 85                    | °C   |

| Storage tempera  | ature, T <sub>stg</sub>                              | -55  | 150                   | °C   |

<sup>(1)</sup> Stresses above those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute maximum rated conditions for extended periods may degrade device reliability.

# 8.2 ESD Ratings

|   |                 |                                                                     | VALUE | UNIT |

|---|-----------------|---------------------------------------------------------------------|-------|------|

| , | Electrostation  | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±1000 | V    |

| \ | (ESD) discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±250  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> When AVDD is turned off, TI recommends to switch off the input clock (or ensure the voltage on CLKP, CLKN is < |0.3V|). This prevents the ESD protection diodes at the clock input pins from turning on.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 8.3 Recommended Operating Conditions

|                   |                                                                                              |                             | MIN | NOM                | MAX | UNIT     |

|-------------------|----------------------------------------------------------------------------------------------|-----------------------------|-----|--------------------|-----|----------|

| SUPPL             | IES                                                                                          |                             |     |                    |     |          |

| AVDD              | Analog supply voltage                                                                        |                             | 1.7 | 1.8                | 1.9 | V        |

| LVDD              | Digital supply voltage                                                                       |                             | 1.7 | 1.8                | 1.9 | V        |

| ANALO             | OG INPUTS/OUTPUTS                                                                            |                             |     |                    |     |          |

|                   | Differential input voltage range                                                             |                             |     | 2                  |     | $V_{PP}$ |

|                   | Input common-mode voltage                                                                    |                             |     | $0.95 \pm 0.05$    |     | V        |

| REF <sub>T</sub>  | External reference mode                                                                      |                             |     | 1.45               |     | V        |

| REFB              | External reference mode                                                                      |                             |     | 0.45               |     | V        |

| VCNA              | Common-mode voltage output                                                                   |                             |     | 0.95               |     | V        |

| VCM               | External Reference mode Input                                                                |                             |     | 1.5                |     | V        |

|                   | Maximum Input Frequency (1)                                                                  | 2 V <sub>PP</sub> amplitude |     | 80                 |     | MHz      |

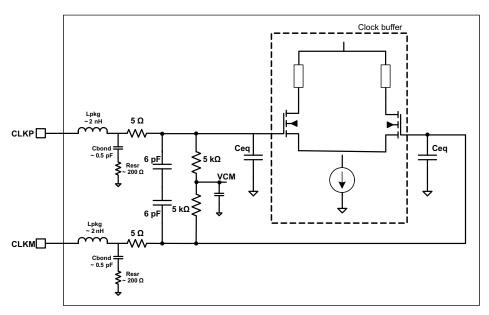

| CLOCI             | (INPUTS                                                                                      |                             |     |                    |     |          |

|                   | ADC Clock input sample rate                                                                  |                             | 10  |                    | 80  | MSPS     |

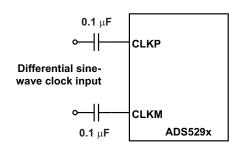

|                   |                                                                                              | Sine wave, AC-coupled       | 0.2 | 1.5                |     |          |

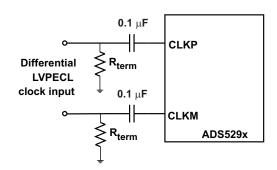

|                   | Input Clock amplitude differential (V <sub>(CLKP)</sub> – V <sub>(CLKN)</sub> ) peak-to-peak | LVPECL, AC-coupled          | 0.2 | 1.6                |     | $V_{PP}$ |

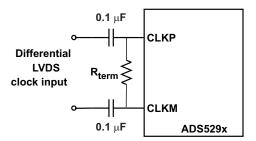

|                   | (V(CLKP)) V(CLKN)) peak to peak                                                              | LVDS, AC-coupled            | 0.2 | 0.7                |     |          |

| $V_{IL}$          | lanut Clark CMCC single anded ()/                                                            |                             |     | <0.3               |     | V        |

| V <sub>IH</sub>   | Input Clock CMOS single-ended (V <sub>(CLKP)</sub> )                                         |                             |     | >1.5               |     | V        |

|                   | Input clock duty cycle                                                                       |                             | 35% | 50%                | 65% |          |

| DIGITA            | L OUTPUTS                                                                                    |                             |     |                    |     |          |

|                   | ACLKP and ACLKN outputs (LVDS), 1-wi                                                         | re interface                |     | 1x (sample rate)   |     | MSPS     |

|                   | LCLKP and LCLKN outputs (LVDS), 1-wir                                                        | e interface                 |     | 7x (sample rate)   |     | MSPS     |

|                   | ACLKP and ACLKN outputs (LVDS), 2-wi                                                         | re interface                | (   | 0.5x (sample rate) |     | MSPS     |

|                   | LCLKP and LCLKN outputs (LVDS), 2-wir                                                        | e interface                 | ;   | 3.5x (sample rate) |     | MSPS     |

|                   | Maximum data rate, 2-wire interface                                                          |                             |     | 560                |     | Mbps     |

|                   | Maximum data rate, 1-wire interface                                                          |                             |     | 700                |     | Mbps     |

| C <sub>LOAD</sub> | Maximum external capacitance from each                                                       | output pin to LGND          |     | 5                  |     | pF       |

| R <sub>LOAD</sub> | Differential load resistance between the L'                                                  | VDS output pairs            |     | 100                |     | Ω        |

| T <sub>A</sub>    | Operating free-air temperature                                                               |                             | -40 |                    | 85  | °C       |

<sup>(1)</sup> See the Large and Small Signal Input Bandwidth section.

### 8.4 Thermal Information

| 0.4 1116             |                                              | ADS5294     |      |

|----------------------|----------------------------------------------|-------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | PFP (HTQFP) | UNIT |

|                      |                                              | 80 PINS     |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 30.8        | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 6.3         | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 8.3         | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.2         | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 8.2         | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 0.3         | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

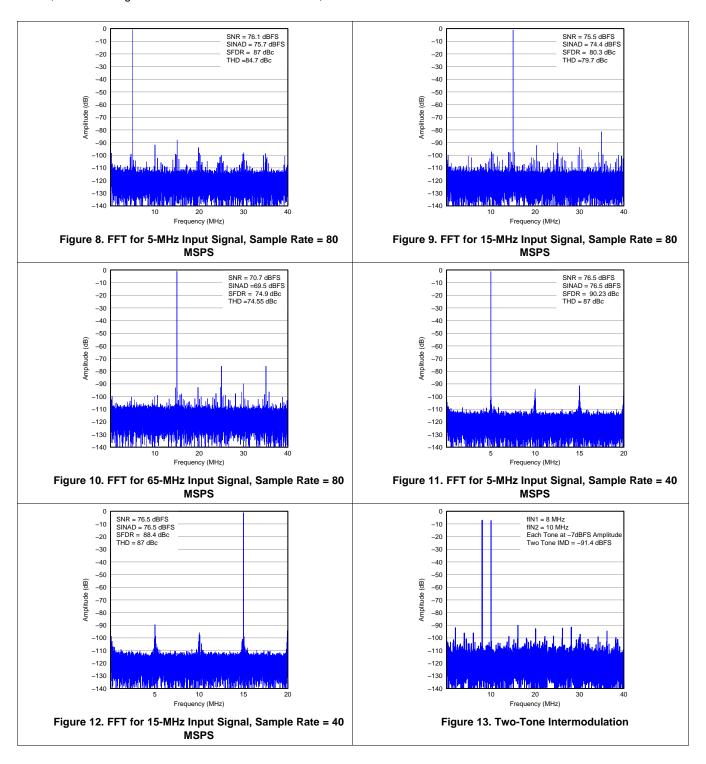

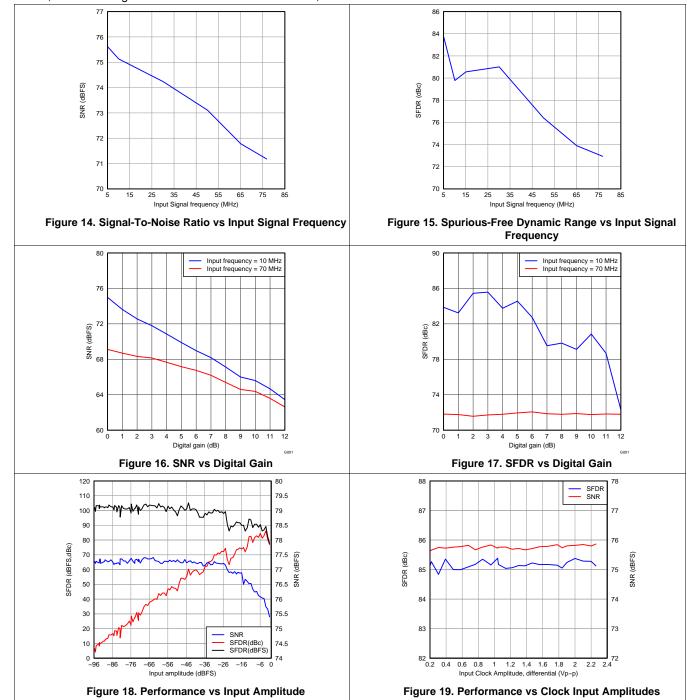

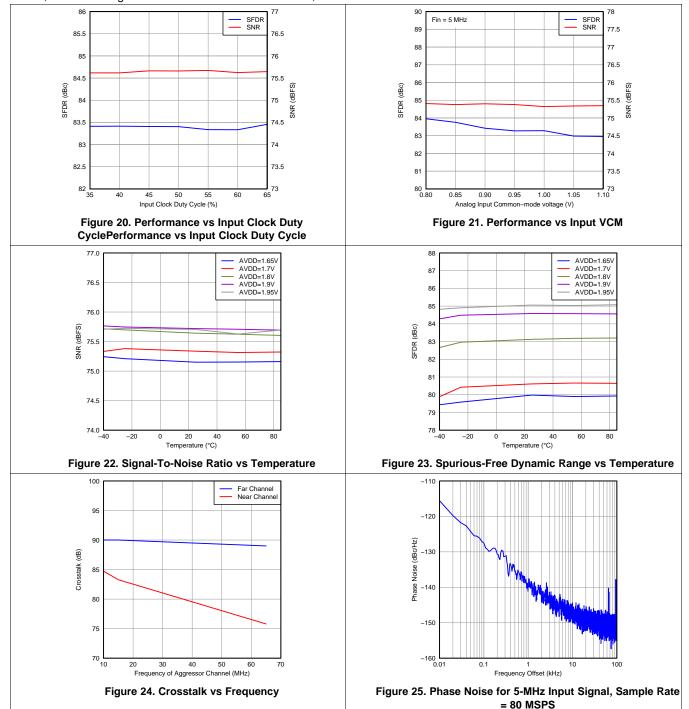

# 8.5 Electrical Characteristics Dynamic Performance

Typical values are at 25°C, AVDD = 1.8 V, LVDD = 1.8 V, 50% clock duty cycle, -1 dBFS differential analog input, Sample rate = 80 MSPS, ADC is configured in internal reference mode (unless otherwise noted). MIN and MAX values are across the full temperature range  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, AVDD = 1.8 V, LVDD = 1.8 V.

|                 | PARAMETERS                                       | TEST CONDITIONS                                                                        |               | MIN   | TYP  | MAX  | UNIT        |

|-----------------|--------------------------------------------------|----------------------------------------------------------------------------------------|---------------|-------|------|------|-------------|

| AC PERF         | ORMANCE                                          |                                                                                        |               |       |      |      |             |

|                 |                                                  | f <sub>in</sub> = 10 MHz, 65 MSPS                                                      |               |       | 75.6 |      | dBFS        |

|                 |                                                  | $f_{in} = 5 \text{ MHz}, T_A = 25^{\circ}\text{C}$                                     |               | 72.8  | 75.5 |      | dBFS        |

|                 |                                                  | f <sub>in</sub> = 5 MHz, Across temperatures                                           |               | 71.8  |      |      | dBFS        |

| SNR             | Signal-to-noise ratio                            | f <sub>in</sub> = 5 MHz, -60 dBFS Input signal amplitud                                | le            |       | 77.3 |      | dBFS        |

|                 |                                                  | $f_{in} = 5$ MHz, Decimation by two enabled                                            |               | 78.2  |      | dBFS |             |

|                 |                                                  | $f_{in} = 30 \text{ MHz}$                                                              |               |       | 74.2 |      | dBFS        |

|                 |                                                  | $f_{in} = 65 \text{ MHz}$                                                              |               |       | 71.7 |      | dBFS        |

|                 |                                                  | $f_{in} = 5 \text{ MHz}$                                                               |               |       | 74.8 |      | dBFS        |

| SINAD           | Signal-to-noise and distortion ratio             | $f_{in} = 30 \text{ MHz}$                                                              |               |       | 73.4 |      | dBFS        |

|                 |                                                  | $f_{in} = 65 \text{ MHz}$                                                              |               |       | 70   |      | dBFS        |

| ENOB            | Effective number of bits                         | $f_{in} = 5 \text{ MHz}$                                                               |               |       | 12.2 |      | Bits        |

| DNL             | Differential nonlinearity                        | $f_{in} = 5 \text{ MHz}$                                                               |               | -0.96 | ±0.5 | 1.7  | LSB         |

| INL             | Integral nonlinearity                            | $f_{in} = 5 \text{ MHz}$                                                               |               |       |      |      |             |

|                 |                                                  | $f_{in} = 5 \text{ MHz}$                                                               |               | 72    | 84   |      | dBc         |

| SFDR            | Spurious-free dynamic range                      | $f_{in} = 30 \text{ MHz}$                                                              |               |       | 81   |      | dBc         |

|                 |                                                  | f <sub>in</sub> = 65 MHz                                                               |               |       | 74   |      | dBc         |

|                 |                                                  | f <sub>in</sub> = 5 MHz                                                                |               | 70.5  | 82   |      | dBc         |

| THD             | Total harmonic distortion                        | $f_{in} = 30 \text{ MHz}$                                                              |               |       | 80   |      | dBc         |

|                 |                                                  | f <sub>in</sub> = 65 MHz                                                               |               |       | 73.5 |      | dBc         |

|                 |                                                  | f <sub>in</sub> = 5 MHz                                                                | 73            | 93    |      | dBc  |             |

| HD2             | Second-harmonic distortion                       | f <sub>in</sub> = 30 MHz                                                               |               |       | 88   |      | dBc         |

|                 |                                                  | f <sub>in</sub> = 65 MHz                                                               |               | 85    |      | dBc  |             |

|                 |                                                  | f <sub>in</sub> = 5 MHz                                                                |               | 72    | 84   |      | dBc         |

| HD3             | Third-harmonic distortion                        | f <sub>in</sub> = 30 MHz                                                               |               |       | 81   |      | dBc         |

|                 |                                                  | f <sub>in</sub> = 65 MHz                                                               |               |       | 74   |      | dBc         |

|                 |                                                  | f <sub>in</sub> = 5 MHz                                                                |               |       | 91   |      | dBc         |

|                 | Worse spur excluding HD2, HD3                    | f <sub>in</sub> = 30 MHz                                                               |               |       | 83   |      | dBc         |

|                 |                                                  | f <sub>in</sub> = 65 MHz                                                               |               |       | 76   |      | dBc         |

| IMD3            | Intermodualtion distortion                       | $f_{in} = 8 \text{ MHz at } -7 \text{ dBFS}, f_2 = 10 \text{ MHz at } -7 \text{ dBFS}$ | dBFS          |       | 84.5 |      | dBc         |

|                 | Overload recovery                                | Recovery to within 1% of full-scale for 6-dB sine wave input                           | overload with |       | 1    |      | Clock Cycle |

| VTALK           | Crass tells                                      | f <sub>in</sub> = 10 MHz, -1-dBFS signal applied on                                    | far channel   |       | 90   |      | dBc         |

| XTALK           | Cross-talk                                       | aggressor channel no signal applied on victim channel                                  | near channel  |       | 85   |      | dBc         |

|                 | Phase noise                                      | 5 MHz, 1-kHz off carrier                                                               |               |       | -138 |      | dBc/Hz      |

| ANALOG          | INPUT / OUTPUT                                   |                                                                                        |               |       |      |      |             |

|                 | Differential input voltage range (0-dB gain)     |                                                                                        |               |       | 2    |      | $V_{PP}$    |

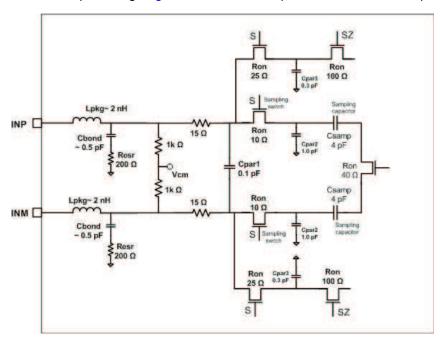

| R <sub>IN</sub> | Differential Input Resistance                    | At DC                                                                                  |               |       | 2    |      | kΩ          |

| C <sub>IN</sub> | Differential Input Capacitance                   | At DC                                                                                  |               |       | 3.2  |      | pF          |

|                 | Analog input bandwidth                           | With a $50-\Omega$ source impedance                                                    |               |       | 550  |      | MHz         |

|                 | Analog input common-mode current (per input pin) |                                                                                        |               |       | 1.6  |      | μA/MSPS     |

|                 | VCM common-mode output voltage                   |                                                                                        |               |       | 0.95 |      | V           |

|                 | VCM output current capability                    |                                                                                        |               |       | 5    |      | mA          |

# **Electrical Characteristics Dynamic Performance (continued)**

Typical values are at 25°C, AVDD = 1.8 V, LVDD = 1.8 V, 50% clock duty cycle, -1 dBFS differential analog input, Sample rate = 80 MSPS, ADC is configured in internal reference mode (unless otherwise noted). MIN and MAX values are across the full temperature range  $T_{MIN} = -40$ °C to  $T_{MAX} = 85$ °C, AVDD = 1.8 V, LVDD = 1.8 V.

|                      | PARAMETERS                                            | TEST CONDITIONS                                                                  | MIN | TYP    | MAX | UNIT    |

|----------------------|-------------------------------------------------------|----------------------------------------------------------------------------------|-----|--------|-----|---------|

| DC ACCU              | JRACY                                                 |                                                                                  |     |        |     |         |

|                      | Offset error                                          | Across devices and across channels within a device                               | -15 |        | 15  | mV      |

|                      | Temperature coefficient of offset error               |                                                                                  |     | < 0.01 |     | mV/ °C  |

| E <sub>(GREF)</sub>  | Gain error due to internal reference inaccuracy alone | Across devices                                                                   | -2  |        | 2   | %FS     |

| E <sub>(GCHAN)</sub> | Gain error of channel alone                           |                                                                                  |     | 0.5    |     | %FS     |

|                      | Temperature coefficient of E <sub>(GCHAN)</sub>       |                                                                                  |     | < 0.01 |     | %FS/ °C |

| POWER S              | SUPPLY                                                |                                                                                  | *   |        | ·   |         |

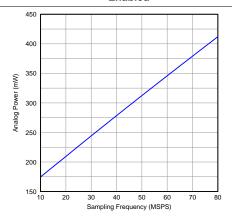

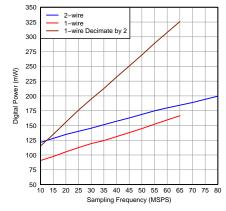

|                      |                                                       | 80 MSPS, 14 Bit, 2-wire LVDS                                                     |     | 77     |     | mW/CH   |

|                      |                                                       | 50 MSPS, 1 wire LVDS                                                             |     | 58     |     | mW/CH   |

|                      | Power consumption                                     | 40 MSPS, 14 Bit, 1-wire LVDS                                                     |     | 52     |     | mW/CH   |

|                      |                                                       | 10 MSPS, 14 Bit, 1-wire LVDS                                                     |     | 33     |     | mW/CH   |

|                      |                                                       | f <sub>in</sub> = 10 MHz, 80 MSPS, 14 Bit,<br>Decimation filter = 2, 1-wire LVDS |     | 100    |     | mW/CH   |

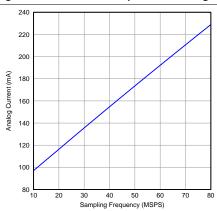

|                      |                                                       | 14 Bit, 80 MSPS                                                                  |     | 230    | 265 | mA      |

| AVDD                 |                                                       | 14 Bit, 65 MSPS                                                                  |     | 200    |     | mA      |

|                      |                                                       | 14 Bit, 40 MSPS                                                                  |     | 155    |     | mA      |

|                      |                                                       | 80 MSPS, 14 Bit, 2-wire LVDS <sup>(1)</sup>                                      |     | 111    | 122 | mA      |

|                      |                                                       | 50 MSPS, 14 Bit, 1-wire LVDS                                                     |     | 80     |     | mA      |

| LVDD                 |                                                       | 40 MSPS, 14 Bit, 1-wire LVDS                                                     |     | 73     |     | mA      |

|                      |                                                       | 80 MSPS, 1 Bit, Decimation filter = 2,<br>1-wire LVDS                            |     | 210    |     | mA      |

|                      | 5 1 "                                                 | Partial Power Down (80 MSPS, 2-wire)                                             |     | 175    |     | mW      |

|                      | Power-down power consumption                          | Complete Power Down                                                              |     |        | 60  | mW      |

|                      | Power supply modulation ratio                         | Carrier = 5 MHz, f <sub>(PSRR)</sub> = 10 kHz, 50 mVpp on AVDD                   |     | 35     |     | dB      |

|                      | Power supply rejection ratio                          | AC power supply rejection ratio f = 10 kHz                                       |     | 55     |     | dB      |

<sup>(1)</sup> The maximum limit used for the LVDD current at -40°C is 132 mA.

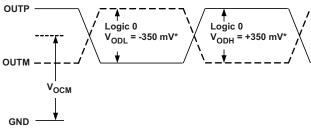

### 8.6 Digital Characteristics

The DC specifications refer to the condition where the digital outputs are not switching, but are permanently at a valid logic level 0 or 1. AVDD = 1.8 V, LVDD = 1.8 V

|                  | PARAMETERS                             | TEST CONDITIONS                                               | MIN  | TYP       | MAX  | UNIT |

|------------------|----------------------------------------|---------------------------------------------------------------|------|-----------|------|------|

| DIGITA           | L INPUTS/OUTPUTS                       |                                                               |      |           |      |      |

| V <sub>IH</sub>  | Logic high input voltage               | All digital inputs support 1.8-V and 3.3-V CMOS logic levels. | 1.3  |           |      | V    |

| $V_{IL}$         | Logic low input voltage                |                                                               |      |           | 0.4  | V    |

| I <sub>IH</sub>  | Logic high input current               | V <sub>HIGH</sub> = 1.8 V                                     |      | 6         |      | μΑ   |

| I <sub>IL</sub>  | Logic low input current                | V <sub>LOW</sub> = 0 V                                        |      | < 0.1     |      | μΑ   |

| V <sub>OH</sub>  | Logic high output voltage              |                                                               | A'   | VDD - 0.1 |      | V    |

| V <sub>OL</sub>  | Logic low output voltage               |                                                               |      | 0.2       |      | V    |

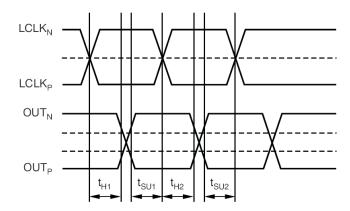

| LVDS             | OUTPUTS (see Figure 2)                 |                                                               |      |           |      |      |

| V <sub>ODH</sub> | High-level output differential voltage | 100-Ω external termination                                    | 245  | 350       | 405  | mV   |

| V <sub>ODL</sub> | Low-level output differential voltage  | 100- $\Omega$ external termination                            | -245 | -350      | -405 | mV   |

| V <sub>OCM</sub> | Output common-mode voltage             |                                                               | 900  | 1100      | 1300 | mV   |

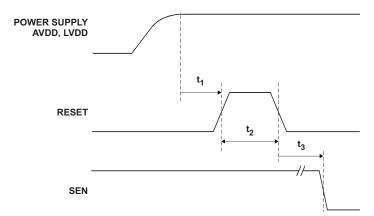

### 8.7 Timing Requirements

Typical values are at 25°C, AVDD = 1.8 V, LVDD = 1.8 V, sampling frequency = 80 MSPS, 14-bit, sine wave input clock = 1.5 Vpp clock amplitude,  $C_{LOAD}$  = 5 pF,  $R_{LOAD}$  = 100  $\Omega$ , unless otherwise noted. MIN and MAX values are across the full temperature range  $T_{MIN}$  = -40°C to  $T_{MAX}$  = 85°C, AVDD = 1.8 V, LVDD = 1.7 V to 1.9 V<sup>(1)(2)(3)</sup>

|                      |                                |                                                                                                                         | MIN                                                                                | TYP                                 | MAX                                                | UNIT            |

|----------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------|-----------------|

| t <sub>a</sub>       | Aperture delay                 | The delay in time between the rising edge of the input sampling clock and the actual time at which the sampling occurs  |                                                                                    | 4                                   |                                                    | ns              |

|                      | Aperture delay variation       | Across channels within the same device                                                                                  |                                                                                    | ±175                                |                                                    | ps              |

|                      |                                | Across devices at the same temperature and LVDD supply                                                                  |                                                                                    | 2.5                                 |                                                    | ns              |

| t <sub>j</sub>       | Aperture jitter RMS            |                                                                                                                         |                                                                                    | 320                                 |                                                    | fs rms          |

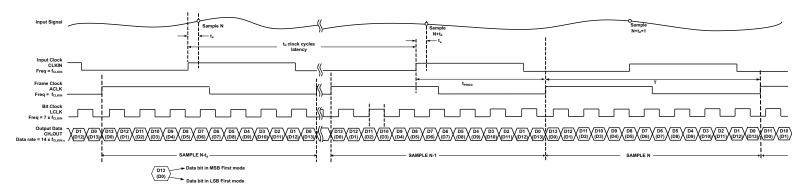

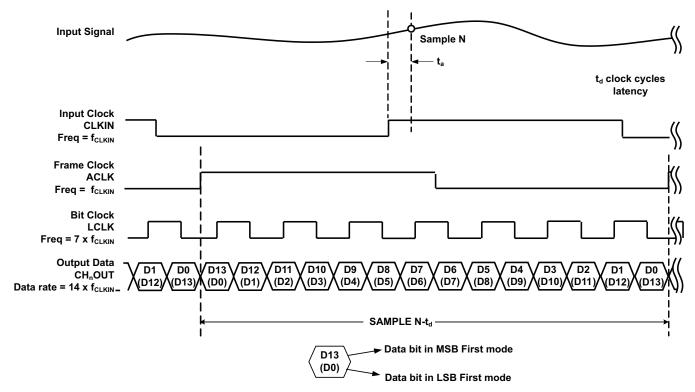

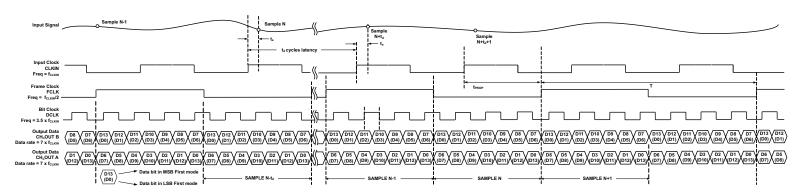

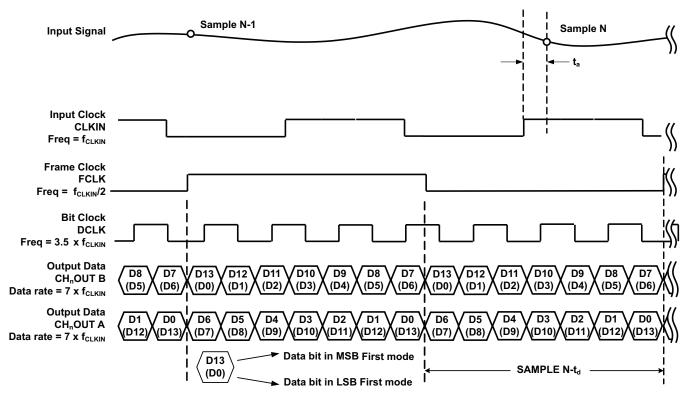

|                      | Data latency                   | 1-wire LVDS output interface                                                                                            |                                                                                    | 11                                  |                                                    | Clock<br>cycles |

| t <sub>d</sub>       | Data latericy                  | 2-wire LVDS output interface                                                                                            |                                                                                    | 15                                  |                                                    | Clock<br>cycles |

| t <sub>SU</sub>      | Data set-up time               | 80 MSPS, 2-wire LVDS, 7x-serialization                                                                                  | 0.34                                                                               | 0.57                                |                                                    | ns              |

| t <sub>H</sub>       | Data hold time                 | 80 MSPS, 2-wire LVDS, 7x-serialization                                                                                  | 0.55                                                                               | 0.8                                 |                                                    | ns              |

| t <sub>PROP</sub>    | Clock propagation delay        | Input clock rising edge (zero cross) to frame clock rising edge (zero cross)                                            | Sampling Front Interface, 7x<br>Filter Disabled<br>Different Sam<br>1-Wire Interfa | Serialization and LVDS pling Freque | - 2-Wire I, Digital Timing at Pencies — alization, |                 |

|                      | Variation of t <sub>PROP</sub> | Between two devices at same temperature and LVDD supply                                                                 |                                                                                    | ±0.75                               |                                                    | ns              |

|                      | LVDS bit clock duty cycle      |                                                                                                                         |                                                                                    | 48%                                 |                                                    |                 |

| t <sub>RISE</sub>    | Data rise time                 | Rise time is from $-100$ mV to $+100$ mV, $10 \le Fs \le 80$ MSPS                                                       |                                                                                    | 0.24                                |                                                    | ns              |

| t <sub>FALL</sub>    | Data fall time                 | Fall time is from +100 mV to −100 mV, 10 ≤ Fs ≤ 80 MSPS                                                                 |                                                                                    | 0.24                                |                                                    | ns              |

| t <sub>CLKRISE</sub> | Output clock rise time         | Rise time is from −100 mV to +100 mV, 10 ≤ Fs ≤ 80 MSPS                                                                 |                                                                                    | 0.20                                |                                                    | ns              |

| t <sub>CLKFALL</sub> | Output clock fall time         | Fall time is from +100 mV to −100 mV, 10 ≤ Fs ≤ 80 MSPS                                                                 |                                                                                    | 0.20                                |                                                    | ns              |

| t <sub>WAKE</sub>    | Wake-up Time                   | Time to valid data after coming out of COMPLETE POWER-DOWN mode                                                         |                                                                                    | 100                                 |                                                    | μs              |

|                      |                                | Time to valid data after coming out of PARTIAL POWER-<br>DOWN mode (with clock continuing to run during power-<br>down) |                                                                                    | 5                                   |                                                    | μs              |

<sup>(1)</sup> Timing parameters are ensured by design and characterization and not tested in production.

<sup>(2)</sup> Measurements are done with a transmission line of 100-Ω characteristic impedance between the device and the load. Set-up and hold time specifications take into account the effect of jitter on the output data and clock.

<sup>(3)</sup> Data valid refers to logic HIGH of 100 mV and logic LOW of -100 mV.

# 8.8 LVDS Timing at Different Sampling Frequencies — 2-Wire Interface, 7x-Serialization, Digital Filter Disabled

See (1)

| ADC CLK Frequency (MSPS) | Set-up                                                   | Time (t <sub>su</sub> ) | , ns | Hold '                                                             | Time (t <sub>H</sub> ), r | าร  | $t_{PROG} = (6 / 7) \times T + t_{delay}, ns^{(2)}$                                                             |     |     |  |