# **PRELIMINARY**

# HPC16083/HPC26083/HPC36083/HPC46083/ HPC16003/HPC26003/HPC36003/HPC46003 **High-Performance microControllers**

### General Description

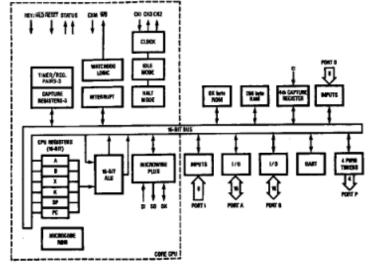

The HPC16083 and HPC16003 are members of the HPCTM family of High Performance microControllers. Each member of the family has the same core CPU with a unique memory and I/O configuration to suit specific applications. The HPC16083 has 8k bytes of on-chip ROM. The HPC16003 has no on-chip ROM and is intended for use with external direct memory. Each part is fabricated in National's advanced microCMOS technology. This process combined with an advanced architecture provides fast, flexible I/O control, efficient data manipulation, and high speed compu-

The HPC devices are complete microcomputers on a single chip. All system timing, internal logic, ROM, RAM, and I/O are provided on the chip to produce a cost effective solution for high performance applications. On-chip functions such as UART, up to eight 16-bit timers with 4 input capture registers, vectored interrupts, WATCHDOG™ logic and MICRO-WIRE/PLUS™ provide a high level of system integration. The ability to address up to 64k bytes of external memory enables the HPC to be used in powerful applications typically performed by microprocessors and expensive peripheral chips. The term "HPC16083" is used throughout this datasheet to refer to the HPC16083 and HPC16003 devices unless otherwise specified.

The microCMOS process results in very low current drain and enables the user to select the optimum speed/power product for his system. The IDLE and HALT modes provide further current savings. The HPC is available in 68-pin PLCC, LDCC, PGA and 80-Pin POFP packages.

#### Features

- HPC family—core features:

- 16-bit architecture, both byte and word

- 16-bit data bus, ALU, and registers

- --- 64k bytes of external direct memory addressing

- FAST-200 ns for fastest instruction when using 20.0 MHz clock, 134 ns at 30 MHz

- High code efficiency-most instructions are single byte

- 16 x 16 multiply and 32 x 16 divide

- Eight vectored interrupt sources

- Four 16-bit timer/counters with 4 synchronous outputs and WATCHDOG logic

- MICROWIRE/PLUS serial I/O interface

- CMOS—very low power with two power save modes: IDLE and HALT

- UART—full duplex, programmable baud rate

- Four additional 16-bit timer/counters with pulse width modulated outputs

- Four input capture registers

- 52 general purpose I/O lines (memory mapped)

- 8k bytes of ROM, 256 bytes of RAM on chip

- ROMless version available (HPC16003)

- Commercial (0°C to +70°C), industrial (-40°C to +85°C), automotive (-40°C to +105°C) and military (-55°C to +125°C) temperature ranges

For applications requiring more RAM and ROM see HPC16064 data sheet.

#### Block Diagram (HPC16083 with 8k ROM shown)

TL/00/8801-1

| <br> | <br> |  |

|------|------|--|

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

|      |      |  |

HPC16083/HPC26083/HPC36083/HPC46083/HPC16003/HPC26003/HPC36003/HPC46003

4

## Absolute Maximum Ratings

If Military/Aerospace specified devices are required. please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Total Allowable Source or Sink Current

100 mA

-65°C to +150°C

Lead Temperature (Soldering, 10 sec)

Storage Temperature Range

300°C

V<sub>CC</sub> with Respect to GND

-0.5V to 7.0V

All Other Pins

$(V_{CC} + 0.5)V$  to (GND - 0.5)V

Note: Absolute maximum ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications are not ensured when operating the device at absolute maximum ratings.

DC Electrical Characteristics  $V_{CC} = 5.0V \pm 10\%$  unless otherwise specified,  $T_A = 0^{\circ}C$  to  $+70^{\circ}C$  for HPC46083/HPC46003, -40°C to +85°C for HPC36083/HPC36003, -40°C to +105°C for HPC26083/HPC26003, -55°C to +125°C for HPC16083/HPC16003

| Symbol           | Parameter                                                                                                      | Test Conditions                                             | Min                   | Max                 | Units |

|------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------|---------------------|-------|

| lcc <sub>1</sub> | Supply Current                                                                                                 | V <sub>CC</sub> = 5.5V, f <sub>in</sub> = 30 MHz (Note 1)   |                       | 65                  | mA    |

|                  |                                                                                                                | V <sub>CC</sub> = 5.5V, f <sub>in</sub> = 20 MHz (Note 1)   |                       | 47                  | mA    |

|                  |                                                                                                                | V <sub>CC</sub> = 5.5V, f <sub>in</sub> = 2.0 MHz (Note 1)  |                       | 10                  | mA    |

| lcc <sub>2</sub> | IDLE Mode Current                                                                                              | V <sub>CC</sub> = 5.5V, f <sub>in</sub> = 30 MHz (Note 1)   |                       | 5.0                 | mA    |

|                  |                                                                                                                | V <sub>CC</sub> = 5.5V, f <sub>in</sub> = 20 MHz, (Note 1)  |                       | 3.0                 | mA    |

|                  |                                                                                                                | V <sub>CC</sub> = 5.5V, f <sub>in</sub> = 2.0 MHz, (Note 1) |                       | 1                   | mA    |

| loc <sub>3</sub> | HALT Mode Current                                                                                              | V <sub>CC</sub> = 5.5V, f <sub>in</sub> = 0 kHz, (Note 1)   |                       | 200                 | μА    |

|                  |                                                                                                                | $V_{CC} = 2.5V$ , $f_{in} = 0$ kHz, (Note 1)                |                       | 50                  | μА    |

|                  | LTAGE LEVELS FOR SCHMITT TRI                                                                                   | GGERED INPUTS RESET, NMI AND WO;                            | AND ALSO CK           |                     |       |

| V <sub>IH1</sub> | Logic High                                                                                                     |                                                             | 0.9 V <sub>CC</sub>   |                     | ٧     |

| V <sub>IL1</sub> | Logic Low                                                                                                      |                                                             |                       | 0.1 V <sub>CC</sub> | ٧     |

|                  | ER INPUTS                                                                                                      |                                                             |                       |                     |       |

| V <sub>IH2</sub> | Logic High                                                                                                     |                                                             | 0.7 V <sub>CC</sub>   |                     | ٧     |

| V <sub>IL2</sub> | Logic Low                                                                                                      |                                                             |                       | 0.2 V <sub>CC</sub> | ٧     |

| I <sub>Lt1</sub> | Input Leakage Current                                                                                          | VIN = 0 and VIN = VCC                                       |                       | ±2                  | μΑ    |

| 1 <sub>LI2</sub> | Input Leakage Current<br>RDY/HLD, EXUI                                                                         | V <sub>IN</sub> = 0                                         | -3                    | -50                 | μА    |

| IU3              | Input Leakage Current<br>B12                                                                                   | RESET - 0, VIN - VCC                                        | 0.5                   | 7                   | mA    |

| Cı               | Input Capacitance                                                                                              | (Note 2)                                                    |                       | 10                  | pF    |

| C <sub>10</sub>  | I/O Capacitance                                                                                                | (Note 2)                                                    |                       | 20                  | pF    |

| OUTPUT \         | OLTAGE LEVELS                                                                                                  |                                                             |                       |                     |       |

| V <sub>OH1</sub> | Logic High (CMOS)                                                                                              | I <sub>OH</sub> = -10 μA (Note 2)                           | V <sub>CC</sub> - 0.1 |                     | ٧     |

| V <sub>OL1</sub> | Logic Low (CMOS)                                                                                               | I <sub>OH</sub> = 10 μA (Note 2)                            |                       | 0.1                 | ٧     |

| V <sub>OH2</sub> | Port A/B Drive, CK2                                                                                            | I <sub>OH</sub> = -7 mA                                     | 2.4                   |                     | ٧     |

| V <sub>OL2</sub> | (A <sub>0</sub> -A <sub>15</sub> , B <sub>10</sub> , B <sub>11</sub> , B <sub>12</sub> , B <sub>15</sub> )     | I <sub>OL</sub> = 3 mA                                      |                       | 0.4                 | ٧     |

| V <sub>OH3</sub> | Other Port Pin Drive, WO (open                                                                                 | I <sub>OH</sub> = -1.6 mA (except WO)                       | 2.4                   |                     | ٧     |

| VOL3             | drain) (B <sub>0</sub> -B <sub>9</sub> , B <sub>13</sub> , B <sub>14</sub> , P <sub>0</sub> -P <sub>3</sub> )  | I <sub>OL</sub> = 0.5 mA                                    |                       | 0.4                 | ٧     |

| V <sub>OH4</sub> | ST1 and ST2 Drive                                                                                              | I <sub>OH</sub> = -6 mA                                     | 2.4                   |                     | v     |

| V <sub>OL4</sub> |                                                                                                                | I <sub>OL</sub> = 1.6 mA                                    |                       | 0.4                 | ٧     |

| V <sub>OH5</sub> | Port A/B Drive (A <sub>0</sub> -A <sub>15</sub> ,                                                              | I <sub>OH</sub> = -1 mA                                     | 2.4                   |                     | ٧     |

| V <sub>OL5</sub> | B <sub>10</sub> , B <sub>11</sub> , B <sub>12</sub> , B <sub>15</sub> ) when used as External Address/Data Bus | I <sub>OL</sub> = 3 mA                                      |                       | 0.4                 | ٧     |

| VRAM             | RAM Keep-Alive Voltage                                                                                         | (Note 3)                                                    | 2.5                   | Vcc                 | ٧     |

| loz              | TRI-STATE® Leakage Current                                                                                     | V <sub>IN</sub> = 0 and V <sub>IN</sub> = V <sub>CC</sub>   |                       | ±5                  | μА    |

Note 1:  $I_{CC_1}$ ,  $I_{CC_2}$ ,  $I_{CC_3}$  measured with no external drive ( $I_{CH}$  and  $I_{OL} = 0$ ,  $I_{IH}$  and  $I_{IL} = 0$ ).  $I_{CC_1}$  is measured with RESET =  $V_{SS}$ ,  $I_{CC_3}$  is measured with NMI =  $V_{CC}$ , CKI driven to  $V_{IH1}$  and  $V_{IL1}$ , with rise and fall times less than 10 ns.

Note 2: This is guaranteed by design and not tested.

Note 3: Test duration is 100 ms.

## 20 MHz

#### **AC Electrical Characteristics**

(See Notes 1 and 4 and Figure 1 thru Figure 5)  $V_{CC} = 5.0V \pm 10\%$  unless otherwise specified,  $T_A = 0^{\circ}C$  to  $+70^{\circ}C$  for HPC46083/HPC46003,  $-40^{\circ}C$  to  $+85^{\circ}C$  for HPC36083/HPC36003,  $-40^{\circ}C$  to  $+105^{\circ}C$  for HPC26083/HPC26003,  $-55^{\circ}C$  to + 125°C for HPC16083/HPC16003

|                                                                                             | Symbol and Formula                          | Parameter                                        | Min  | Max      | Units | Note     |

|---------------------------------------------------------------------------------------------|---------------------------------------------|--------------------------------------------------|------|----------|-------|----------|

|                                                                                             | fc                                          | CKI Operating Frequency                          | 2 ,  | 20       | MHz   |          |

|                                                                                             | $t_{C1} = 1/f_{C}$                          | CKI Clock Period                                 | 50   | 500      | ns    |          |

|                                                                                             | t <sub>CKIH</sub>                           | CKI High Time                                    | 22.5 |          | ns    |          |

|                                                                                             | t <sub>CKIL</sub>                           | CKI Low Time                                     | 22.5 |          | ns    |          |

|                                                                                             | $t_C = 2/f_C$                               | CPU Timing Cycle                                 | 100  |          | ns    |          |

| \$                                                                                          | $t_{WAIT} = t_{C}$                          | CPU Wait State Period                            | 100  |          | ns    |          |

| Clocks                                                                                      | <sup>t</sup> DC1C2R                         | Delay of CK2 Rising Edge after                   | 0    | 55       | ns    | (Note 1) |

| °                                                                                           |                                             | CKI Falling Edge Delay of CK2 Falling Edge after |      |          | 1     |          |

|                                                                                             | <sup>t</sup> DC1C2F                         | CK1 Falling Edge                                 | 0    | 55       | ns    | (Note 1) |

| H                                                                                           | 1 - 1 10                                    | External UART Clock Input Frequency              |      | 2.5**    | MHz   |          |

|                                                                                             | $f_U = f_C/8$                               | External MICROWIRE/PLUS                          |      |          |       |          |

| 1                                                                                           | fMW                                         | Clock Input Frequency                            |      | 1.25     | MHz   |          |

| _                                                                                           |                                             |                                                  | _    |          |       |          |

| Ē                                                                                           | $f_{XIN} = f_{C}/22$                        | External Timer Input Frequency                   |      | 0.91     | MHz   |          |

| Timers                                                                                      | $t_{XIN} = t_{C}$                           | Pulse Width for Timer Inputs                     | 100  |          | ns    |          |

|                                                                                             | tuws                                        | MICROWIRE Setup Time—Master                      | 100. |          | ns    |          |

| <u> </u>                                                                                    | ****                                        | —Slave                                           | 20   | <u> </u> |       |          |

| \<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\ | tuwn                                        | MICROWIRE Hold Time—Master                       | 20   |          | ns    | ĺ        |

| 윤군                                                                                          | OWN                                         | —Slave                                           | 50   |          |       |          |

| MICROWIRE/<br>PLUS                                                                          | tuwv                                        | MICROWIRE Output Valid Time-Master               |      | 50       | ns    |          |

| -                                                                                           | OWV                                         | —Slave                                           |      | 150      |       |          |

|                                                                                             | t <sub>SALE</sub> = 3/4 t <sub>C</sub> + 40 | HLD Falling Edge before ALE Rising Edge          | 115  |          | ns    |          |

| 호                                                                                           | $t_{HWP} = t_C + 10$                        | HLD Pulse Width                                  | 110  |          | ns    |          |

| <b>=</b>                                                                                    | $t_{HAE} = t_C + 100$                       | HLDA Falling Edge after HLD Falling Edge         | 1    | 200      | ns    | (Note 3) |

| E                                                                                           | $t_{HAD} = \frac{3}{4}t_{C} + 85$           | HLDA Rising Edge after HLD Rising Edge           |      | 160      | ns    |          |

| External Hold                                                                               | $t_{BF} = \frac{1}{2}t_{C} + 66$            | Bus Float after HLDA Falling Edge                |      | 116      | ns    | (Note 5) |

|                                                                                             | $t_{BE} = \frac{1}{2}t_{C} + 66$            | Bus Enable after HLDA Rising Edge                | 116  |          | ns    | (Note 5) |

|                                                                                             | tuas                                        | Address Setup Time to Falling Edge of URD        | 10   |          | ns    |          |

|                                                                                             | tuah                                        | Address Hold Time from Rising Edge of URD        | 10   |          | ns    | <b>_</b> |

|                                                                                             | t <sub>RPW</sub>                            | URD Pulse Width                                  | 100  |          | ns    | ļ        |

| 8                                                                                           | t <sub>OE</sub>                             | URD Falling Edge to Output Data Valid            | 0    | 60       | ns    |          |

|                                                                                             | top                                         | Rising Edge of URD to Output Data Invalid        | 5    | 35       | ns    | (Note 6) |

| III I                                                                                       | t <sub>DRDY</sub>                           | RDRDY Delay from Rising Edge of URD              | ļ    | 70       | ns    | <u> </u> |

| <b>-</b> [                                                                                  | twow                                        | UWR Pulse Width                                  | 40   |          | ns    |          |

|                                                                                             | tups                                        | Input Data Valid before Rising Edge of UWR       | 10   |          | ns    |          |

|                                                                                             | tuph                                        | Input Data Hold after Rising Edge of UWR         | 20   |          | ns    |          |

|                                                                                             | t <sub>A</sub>                              | WRRDY Delay from Rising Edge of UWR              |      | 70       | .ns   |          |

<sup>\*\*</sup>This maximum frequency is attainable provided that this external baud clock has a duty cycle such that the high period includes two (2) falling edges of the CK2 clock.

|  | <br> |  |

|--|------|--|

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |

|  |      |  |