SLAS722G - DECEMBER 2010 - REVISED MAY 2013

# MIXED SIGNAL MICROCONTROLLER

# FEATURES

- Low Supply Voltage Range: 1.8 V to 3.6 V

- **Ultra-Low Power Consumption**

- Active Mode: 220 µA at 1 MHz, 2.2 V

- Standby Mode: 0.5 µA

- Off Mode (RAM Retention): 0.1 µA

- **Five Power-Saving Modes**

- Ultra-Fast Wake-Up From Standby Mode in Less Than 1 µs

- 16-Bit RISC Architecture, 62.5-ns Instruction **Cycle Time**

- **Basic Clock Module Configurations**

- Internal Frequencies up to 16 MHz With Four Calibrated Frequencies

- Internal Very-Low-Power Low-Frequency (LF) Oscillator

- 32-kHz Crystal

- External Digital Clock Source

- One 16-Bit Timer A With Three ٠ Capture/Compare Registers

- Up to 16 Capacitive-Touch Enabled I/O Pins

- Universal Serial Interface (USI) Supporting SPI and I2C

- 10-Bit 200-ksps Analog-to-Digital (A/D) Converter With Internal Reference, Sampleand-Hold, and Autoscan (MSP430G2x52 Only)

- **On-Chip Comparator for Analog**

- **Brownout Detector**

- Serial Onboard Programming, ٠ No External Programming Voltage Needed, **Programmable Code Protection by Security** Fuse

- **On-Chip Emulation Logic With Spy-Bi-Wire** Interface

- Family Members are Summarized in Table 1

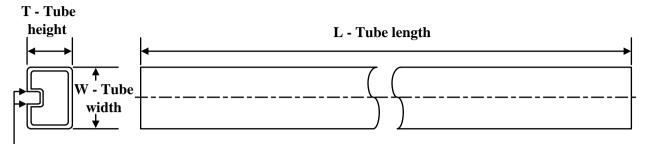

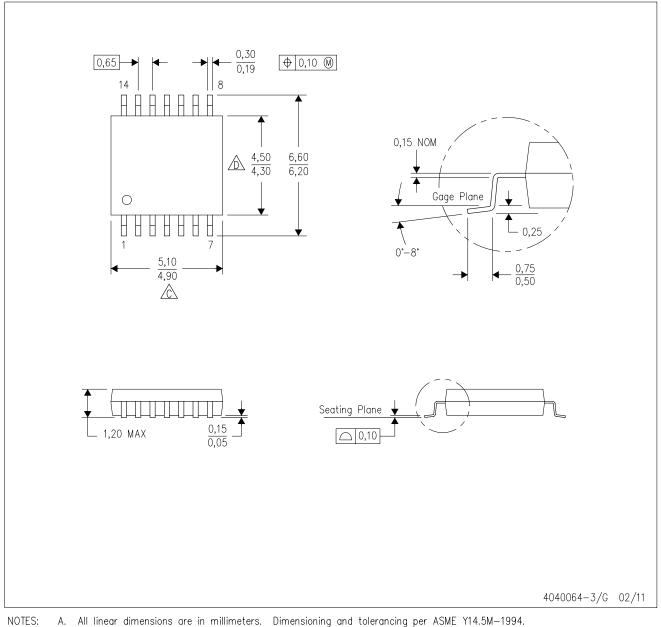

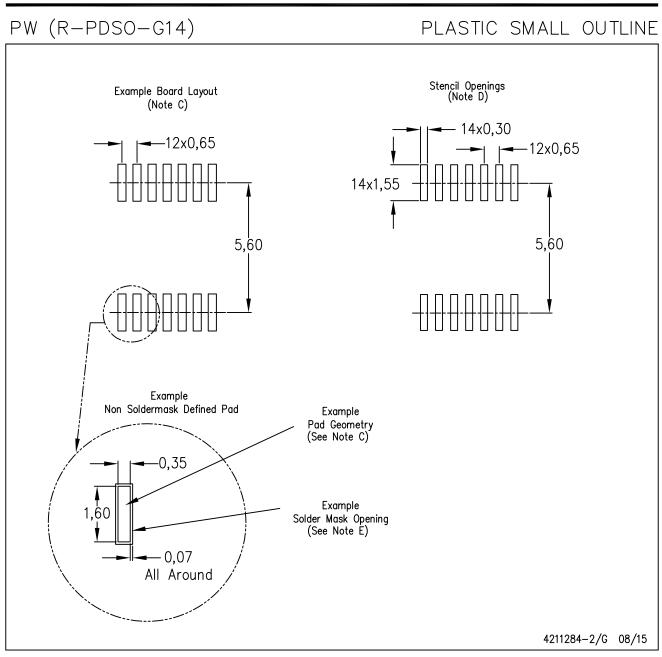

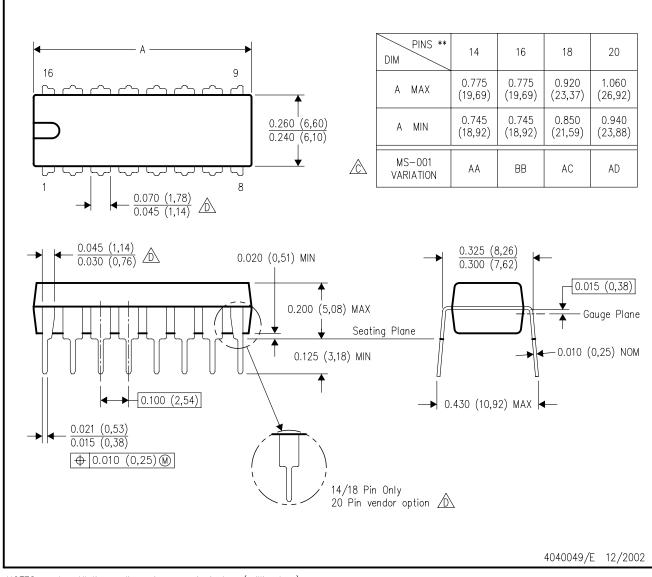

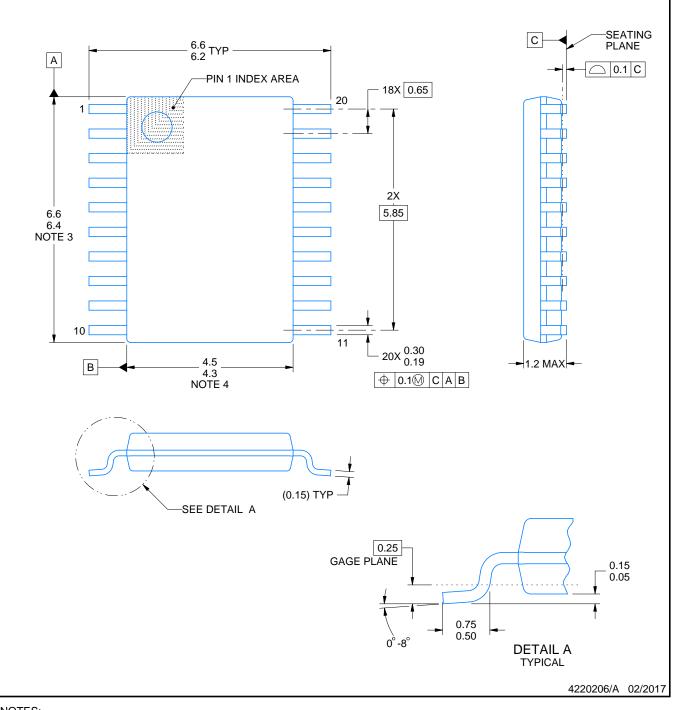

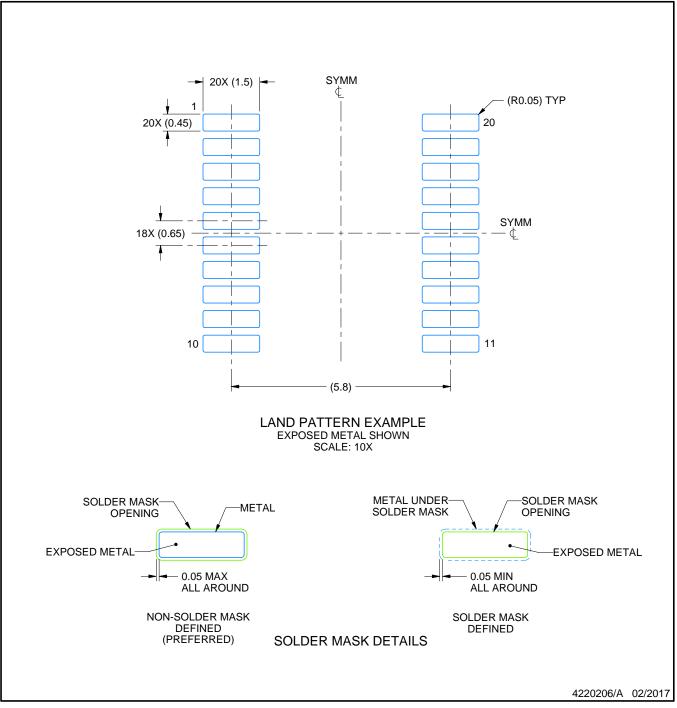

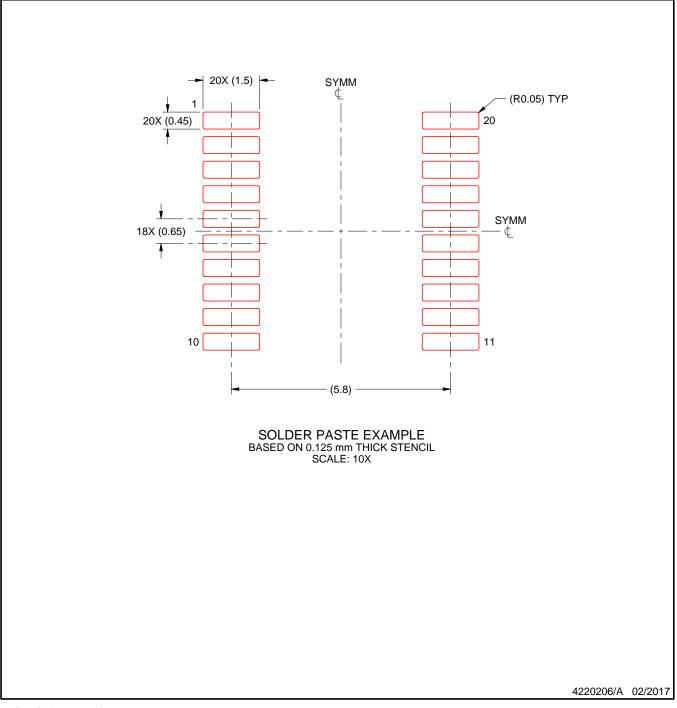

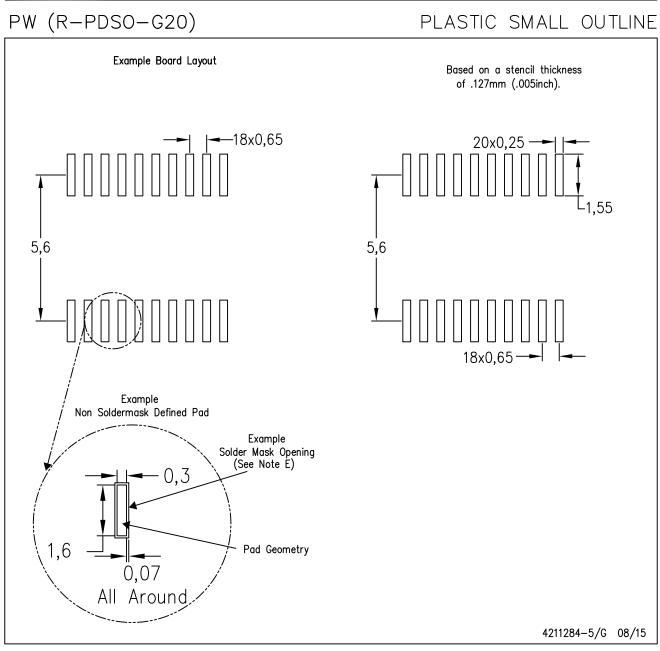

- **Package Options**

- TSSOP: 14 Pin, 20 Pin

- PDIP: 20 Pin

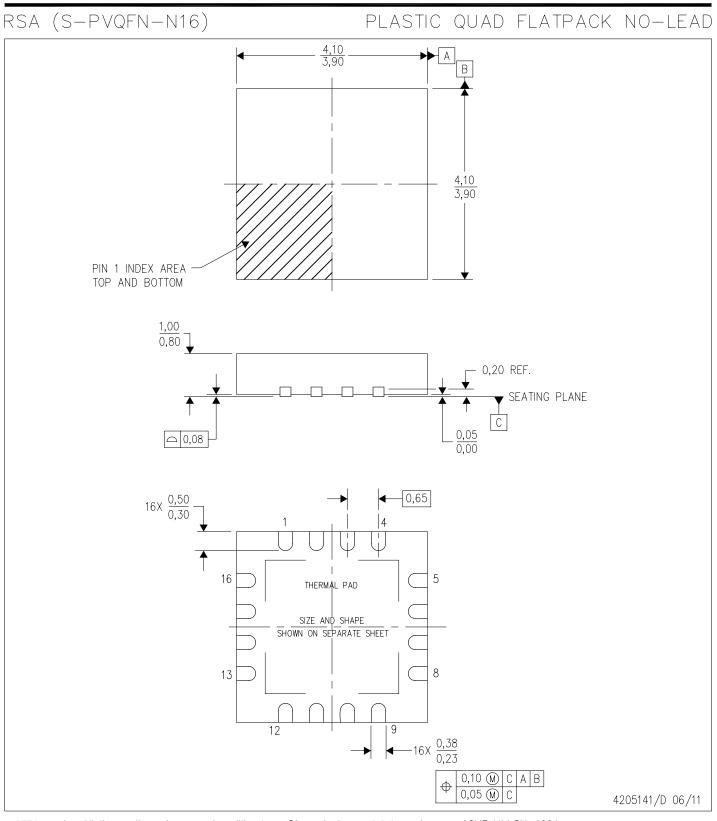

- QFN: 16 Pin

- For Complete Module Descriptions, See the MSP430x2xx Family User's Guide (SLAU144)

# DESCRIPTION

The Texas Instruments MSP430<sup>™</sup> family of ultra-low-power microcontrollers consist of several devices featuring different sets of peripherals targeted for various applications. The architecture, combined with five low-power modes, is optimized to achieve extended battery life in portable measurement applications. The device features a powerful 16-bit RISC CPU, 16-bit registers, and constant generators that contribute to maximum code efficiency. The digitally controlled oscillator (DCO) allows wake-up from low-power modes to active mode in less than 1 µs.

The MSP430G2x52 and MSP430G2x12 series of microcontrollers are ultra-low-power mixed signal microcontrollers with built-in 16-bit timers, and up to 16 I/O capacitive-touch enabled pins and built-in communication capability using the universal serial communication interface and have a versatile analog comparator. The MSP430G2x52 series have a 10-bit A/D converter. For configuration details see Table 1. Typical applications include low-cost sensor systems that capture analog signals, convert them to digital values, and then process the data for display or for transmission to a host system.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. MSP430 is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

www.ti.com

| Table 1. Available Options <sup>(1)</sup> |     |               |            |         |                   |                  |     |              |     |                                |

|-------------------------------------------|-----|---------------|------------|---------|-------------------|------------------|-----|--------------|-----|--------------------------------|

| Device                                    | EEM | Flash<br>(KB) | RAM<br>(B) | Timer_A | Comp_A<br>Channel | ADC10<br>Channel | USI | Clock        | I/O | Package<br>Type <sup>(2)</sup> |

| MSP430G2452IN20                           |     |               |            |         |                   |                  |     |              | 16  | 20-PDIP                        |

| MSP430G2452IPW20                          | 1   | 8             | 256        | 1x TA3  | 8                 | 8                | 1   |              | 16  | 20-TSSOP                       |

| MSP430G2452IRSA16                         | 1   | 8             | 256        | TX TA3  | 8                 |                  |     | LF, DCO, VLO | 10  | 16-QFN                         |

| MSP430G2452IPW14                          |     |               |            |         |                   |                  |     |              | 10  | 14-TSSOP                       |

| MSP430G2352IN20                           |     |               |            |         |                   |                  |     |              | 16  | 20-PDIP                        |

| MSP430G2352IPW20                          |     |               | 050        | 4       |                   | 0                |     |              | 16  | 20-TSSOP                       |

| MSP430G2352IRSA16                         | 1   | 4             | 256        | 1x TA3  | 8                 | 8                | 1   | LF, DCO, VLO | 10  | 16-QFN                         |

| MSP430G2352IPW14                          |     |               |            |         |                   |                  |     |              | 10  | 14-TSSOP                       |

| MSP430G2252IN20                           |     |               |            |         |                   |                  |     |              | 16  | 20-PDIP                        |

| MSP430G2252IPW20                          |     |               | 050        | 4       |                   | 8                | 1   | LF, DCO, VLO | 16  | 20-TSSOP                       |

| MSP430G2252IRSA16                         | 1   | 2             | 256        | 1x TA3  | 8                 |                  |     |              | 10  | 16-QFN                         |

| MSP430G2252IPW14                          |     |               |            |         |                   |                  |     |              | 10  | 14-TSSOP                       |

| MSP430G2152IN20                           |     |               |            |         |                   |                  |     |              | 16  | 20-PDIP                        |

| MSP430G2152IPW20                          | 1   |               | 128        | 4       | 8                 | 0                |     |              | 16  | 20-TSSOP                       |

| MSP430G2152IRSA16                         |     | 1             |            | 1x TA3  |                   | 8                | 1   | LF, DCO, VLO | 10  | 16-QFN                         |

| MSP430G2152IPW14                          |     |               |            |         |                   |                  |     |              | 10  | 14-TSSOP                       |

| MSP430G2412IN20                           |     |               |            |         |                   |                  |     |              | 16  | 20-PDIP                        |

| MSP430G2412IPW20                          |     |               | 256        | 1x TA3  | 8                 | -                | 1   | LF, DCO, VLO | 16  | 20-TSSOP                       |

| MSP430G2412IRSA16                         | 1   | 8             |            |         |                   |                  |     |              | 10  | 16-QFN                         |

| MSP430G2412IPW14                          |     |               |            |         |                   |                  |     |              | 10  | 14-TSSOP                       |

| MSP430G2312IN20                           |     |               |            |         |                   |                  |     |              | 16  | 20-PDIP                        |

| MSP430G2312IPW20                          |     |               | 050        |         | _                 |                  |     |              | 16  | 20-TSSOP                       |

| MSP430G2312IRSA16                         | 1   | 4             | 256        | 1x TA3  | 8                 | -                | 1   | LF, DCO, VLO | 10  | 16-QFN                         |

| MSP430G2312IPW14                          |     |               |            |         |                   |                  |     |              | 10  | 14-TSSOP                       |

| MSP430G2212IN20                           |     |               |            |         |                   |                  |     |              | 16  | 20-PDIP                        |

| MSP430G2212IPW20                          |     |               | 050        | 4 746   |                   |                  |     |              | 16  | 20-TSSOP                       |

| MSP430G2212IRSA16                         | 1   | 2             | 256        | 1x TA3  | 8                 | -                | 1   | LF, DCO, VLO | 10  | 16-QFN                         |

| MSP430G2212IPW14                          |     |               |            |         |                   |                  |     |              | 10  | 14-TSSOP                       |

| MSP430G2112IN20                           |     |               |            |         |                   |                  |     |              | 16  | 20-PDIP                        |

| MSP430G2112IPW20                          |     |               | 465        |         | -                 |                  |     | LF, DCO, VLO | 16  | 20-TSSOP                       |

| MSP430G2112IRSA16                         | 1   | 1             | 128        | 1x TA3  | 8                 | -                | 1   |              | 10  | 16-QFN                         |

| MSP430G2112IPW14                          |     |               |            |         |                   |                  |     |              | 10  | 14-TSSOP                       |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

(2) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

SLAS722G - DECEMBER 2010-REVISED MAY 2013

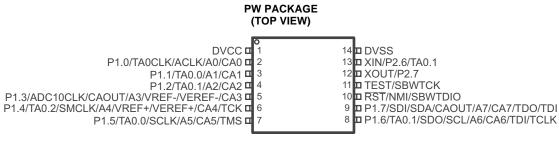

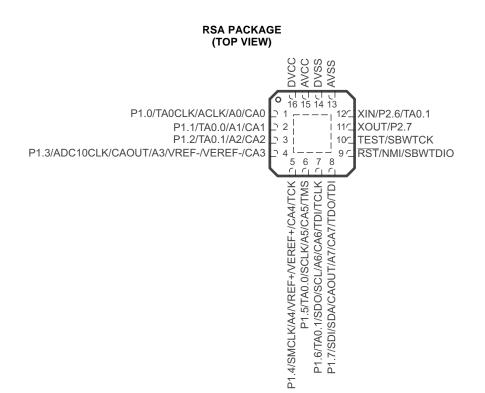

# **DEVICE PINOUTS**

NOTE: ADC10 pin functions are available only on MSP430G2x52.

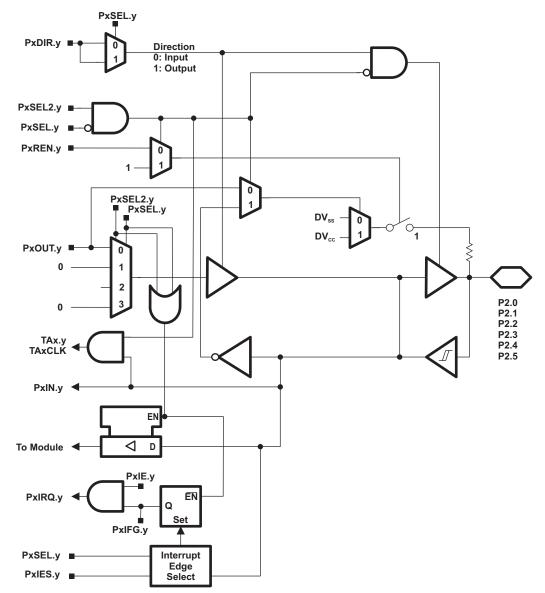

NOTE: The pulldown resistors of port pins P2.0, P2.1, P2.2, P2.3, P2.4, and P2.5 should be enabled by setting P2REN.x = 1.

NOTE: ADC10 pin functions are available only on MSP430G2x52.

NOTE: The pulldown resistors of port pins P2.0, P2.1, P2.2, P2.3, P2.4, and P2.5 should be enabled by setting P2REN.x = 1.

| N O                                        | PR PW PACKAGE<br>(TOP VIEW) |                                     |

|--------------------------------------------|-----------------------------|-------------------------------------|

| DVCC                                       | <b>o</b><br>1 20            | DVSS                                |

| P1.0/TA0CLK/ACLK/A0/CA0                    | 2 19                        | D XIN/P2.6/TA0.1                    |

| P1.1/TA0.0/A1/CA1 🞞                        | 3 18                        | DXOUT/P2.7                          |

| P1.2/TA0.1/A2/CA2 <b>II</b>                | 4 17                        | DTEST/SBWTCK                        |

| P1.3/ADC10CLK/CAOUT/VREF-/VEREF-/A3/CA3 I  | 5 16                        | <b>D</b> RST/NMI/SBWTDIO            |

| P1.4/TA0.2/SMCLK/A4/VREF+/VEREF+/CA4/TCK I | 6 15                        | D P1.7/SDI/SDA/CAOUT/A7/CA7/TDO/TDI |

| P1.5/TA0.0/SCLK/A5/CA5/TMS II              | 7 14                        | DP1.6/TA0.1/SDO/SCL/A6/CA6/TDI/TCLK |

| P2.0 <b>II</b>                             | 8 13                        | <b>D</b> P2.5                       |

| P2.1 <b>¤</b>                              | 9 12                        | 2 <b>D</b> P2.4                     |

| P2.2 <b>I</b>                              | 10 11                       | <b>□</b> P2.3                       |

NOTE: ADC10 pin functions are available only on MSP430G2x52.

www.ti.com

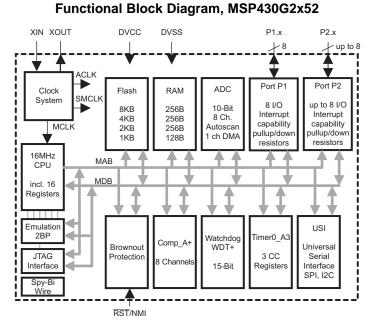

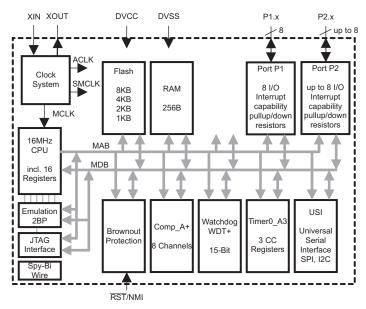

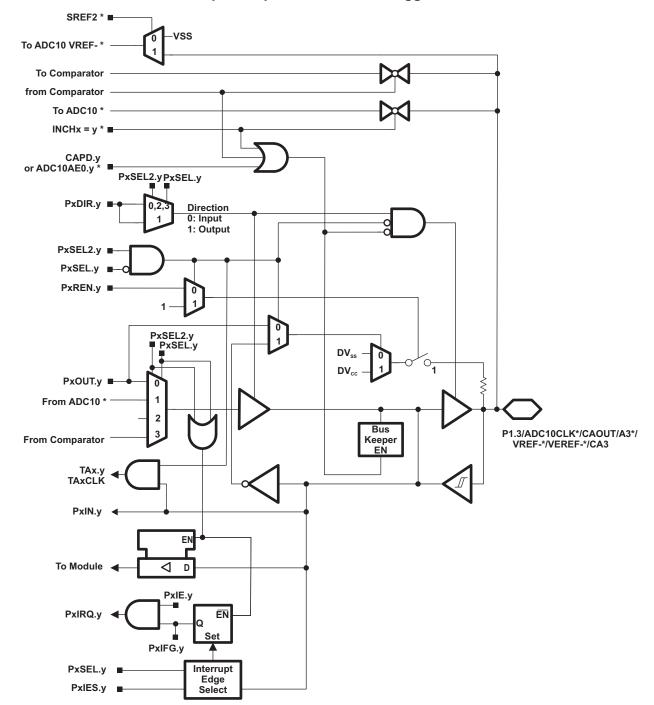

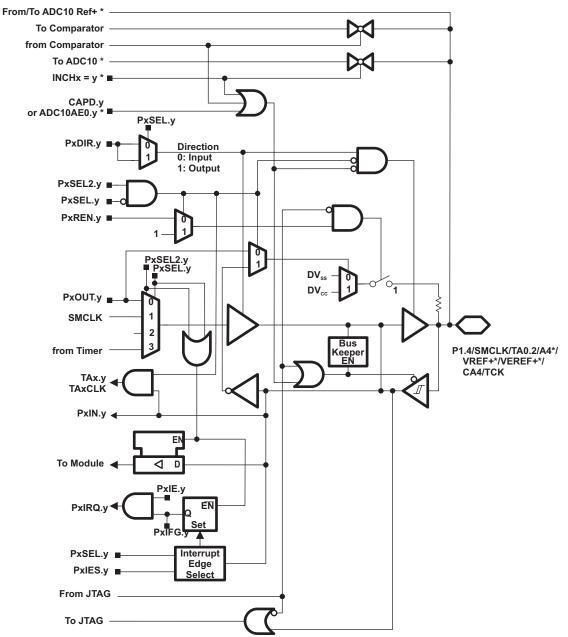

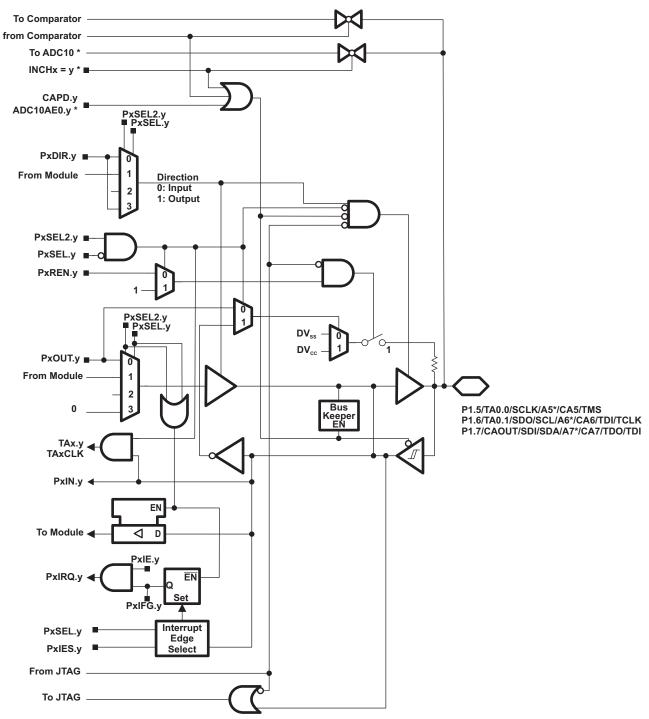

FUNCTIONAL BLOCK DIAGRAMS

# NOTE: Port P2. Two pins are available on the 14-pin and 16-pin package options. Eight pins are available on the 20-pin package options.

## Functional Block Diagram, MSP430G2x12

NOTE: Port P2. Two pins are available on the 14-pin and 16-pin package options. Eight pins are available on the 20-pin package options.

#### SLAS722G - DECEMBER 2010 - REVISED MAY 2013

# **TERMINAL FUNCTIONS**

## **Table 2. Terminal Functions**

| TERMINAL      |          |           |             |     |                                                                       |  |  |  |

|---------------|----------|-----------|-------------|-----|-----------------------------------------------------------------------|--|--|--|

|               |          | NO.       |             | I/O | DESCRIPTION                                                           |  |  |  |

| NAME          | 14<br>PW | 16<br>RSA | 20<br>N, PW |     |                                                                       |  |  |  |

| P1.0/         |          |           |             |     | General-purpose digital I/O pin                                       |  |  |  |

| TA0CLK/       |          |           |             |     | Timer0_A, clock signal TACLK input                                    |  |  |  |

| ACLK/         | 2        | 1         | 2           | I/O | ACLK signal output                                                    |  |  |  |

| A0/           |          |           |             |     | ADC10 analog input A0 <sup>(1)</sup>                                  |  |  |  |

| CA0           |          |           |             |     | Comparator_A+, CA0 input                                              |  |  |  |

| P1.1/         |          |           |             |     | General-purpose digital I/O pin                                       |  |  |  |

| TA0.0/        | 2        | 2         | 2           | 1/0 | Timer0_A, capture: CCI0A input, compare: Out0 output                  |  |  |  |

| A1/           | 3        | 2         | 3           | I/O | ADC10 analog input A1 <sup>(1)</sup>                                  |  |  |  |

| CA1           |          |           |             |     | Comparator_A+, CA1 input                                              |  |  |  |

| P1.2/         |          |           |             |     | General-purpose digital I/O pin                                       |  |  |  |

| TA0.1/        |          | 2         | 4           | 1/0 | Timer0_A, capture: CCI1A input, compare: Out1 output                  |  |  |  |

| A2/           | 4        | 3 4       |             | I/O | ADC10 analog input A2 <sup>(1)</sup>                                  |  |  |  |

| CA2           |          |           |             |     | Comparator_A+, CA2 input                                              |  |  |  |

| P1.3/         |          |           |             |     | General-purpose digital I/O pin                                       |  |  |  |

| ADC10CLK/     |          |           |             |     | ADC10, conversion clock output <sup>(1)</sup>                         |  |  |  |

| CAOUT/        | -        |           | -           | I/O | Comparator_A+, output                                                 |  |  |  |

| A3/           | 5        | 4         | 4 5         |     | ADC10 analog input A3 <sup>(1)</sup>                                  |  |  |  |

| VREF-/VEREF-/ |          |           |             |     | ADC10 negative reference voltage <sup>(1)</sup>                       |  |  |  |

| CA3           |          |           |             |     | Comparator_A+, CA3 input                                              |  |  |  |

| P1.4/         |          |           |             |     | General-purpose digital I/O pin                                       |  |  |  |

| SMCLK/        |          |           |             |     | SMCLK signal output                                                   |  |  |  |

| TA0.2/        |          |           |             |     | Timer0_A, capture: CCI2A input, compare: Out2 output                  |  |  |  |

| A4/           | 6        | 5         | 6           | I/O | ADC10 analog input A4 <sup>(1)</sup>                                  |  |  |  |

| VREF+/VEREF+/ |          |           |             |     | ADC10 positive reference voltage <sup>(1)</sup>                       |  |  |  |

| CA4/          |          |           |             |     | Comparator_A+, CA4 input                                              |  |  |  |

| тск           |          |           |             |     | JTAG test clock, input terminal for device programming and test       |  |  |  |

| P1.5/         |          |           |             |     | General-purpose digital I/O pin                                       |  |  |  |

| TA0.0/        |          |           |             |     | Timer0_A, compare: Out0 output                                        |  |  |  |

| SCLK/         | 7        | C         | 7           | 1/0 | USI: clk input in I2C mode; clk in/output in SPI mode                 |  |  |  |

| A5/           | 7        | 6         | 7           | I/O | ADC10 analog input A5 <sup>(1)</sup>                                  |  |  |  |

| CA5/          |          |           |             |     | Comparator_A+, CA5 input                                              |  |  |  |

| TMS           |          |           |             |     | JTAG test mode select, input terminal for device programming and test |  |  |  |

| P1.6/         |          |           |             |     | General-purpose digital I/O pin                                       |  |  |  |

| TA0.1/        |          |           |             |     | Timer0_A, compare: Out1 output                                        |  |  |  |

| SDO/          |          |           |             |     | USI: Data output in SPI mode                                          |  |  |  |

| SCL/          | 8        | 7         | 14          | I/O | USI: I2C clock in I2C mode                                            |  |  |  |

| A6/           |          |           |             |     | ADC10 analog input A6 <sup>(1)</sup>                                  |  |  |  |

| CA6/          |          |           |             |     | Comparator_A+, CA6 input                                              |  |  |  |

| TDI/TCLK      |          |           |             |     | JTAG test data input or test clock input during programming and test  |  |  |  |

Г

#### SLAS722G - DECEMBER 2010 - REVISED MAY 2013

| Table 2. | Terminal                               | Functions  | (continued) |

|----------|----------------------------------------|------------|-------------|

|          | i ci i i i i i i i i i i i i i i i i i | i unotiono | (oonunaca)  |

| TERMINAL               |          |     |    |     |                                                                                             |  |  |  |

|------------------------|----------|-----|----|-----|---------------------------------------------------------------------------------------------|--|--|--|

|                        |          | NO. |    |     | DESCRIPTION                                                                                 |  |  |  |

| NAME                   | 14<br>PW |     |    | I/O | DESCRIPTION                                                                                 |  |  |  |

| P1.7/                  |          |     |    |     | General-purpose digital I/O pin                                                             |  |  |  |

| CAOUT/                 |          |     |    |     | Comparator_A+, output                                                                       |  |  |  |

| SDI/                   |          |     |    |     | USI: Data input in SPI mode                                                                 |  |  |  |

| SDA/                   | 9        | 8   | 15 | I/O | USI: I2C data in I2C mode                                                                   |  |  |  |

| A7/                    |          |     |    |     | ADC10 analog input A7 <sup>(1)</sup>                                                        |  |  |  |

| CA7/                   |          |     |    |     | Comparator_A+, CA7 input                                                                    |  |  |  |

| TDO/TDI <sup>(2)</sup> |          |     |    |     | JTAG test data output terminal or test data input during programming and test               |  |  |  |

| P2.0                   | -        | -   | 8  | I/O | General-purpose digital I/O pin                                                             |  |  |  |

| P2.1                   | -        | -   | 9  | I/O | General-purpose digital I/O pin                                                             |  |  |  |

| P2.2                   | -        | -   | 10 | I/O | General-purpose digital I/O pin                                                             |  |  |  |

| P2.3                   | -        | -   | 11 | I/O | General-purpose digital I/O pin                                                             |  |  |  |

| P2.4                   | -        | -   | 12 | I/O | General-purpose digital I/O pin                                                             |  |  |  |

| P2.5                   | -        | -   | 13 | I/O | General-purpose digital I/O pin                                                             |  |  |  |

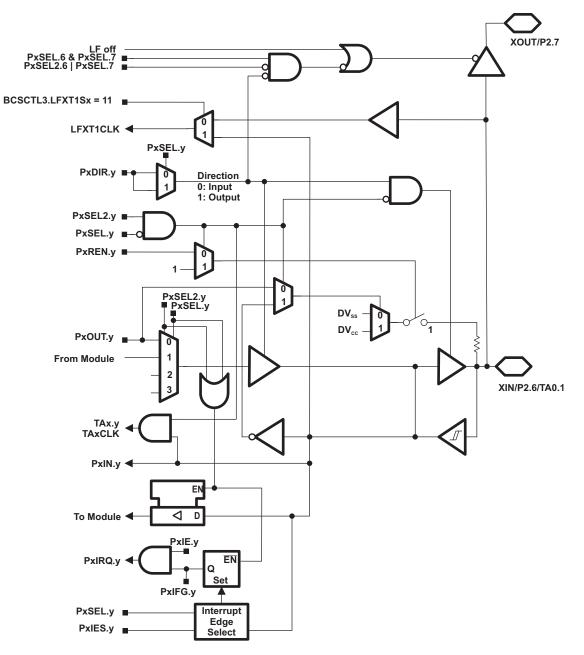

| XIN/                   |          |     |    |     | Input terminal of crystal oscillator                                                        |  |  |  |

| P2.6/                  | 13       | 12  | 19 | I/O | General-purpose digital I/O pin                                                             |  |  |  |

| TA0.1                  |          |     |    |     | Timer0_A, compare: Out1 output                                                              |  |  |  |

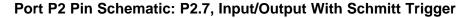

| XOUT/                  | 40       |     | 40 | I/O | Output terminal of crystal oscillator <sup>(3)</sup>                                        |  |  |  |

| P2.7                   | 12       | 11  | 18 | 1/0 | General-purpose digital I/O pin                                                             |  |  |  |

| RST/                   |          |     |    |     | Reset                                                                                       |  |  |  |

| NMI/                   | 10       | 9   | 16 | Ι   | Nonmaskable interrupt input                                                                 |  |  |  |

| SBWTDIO                |          |     |    |     | Spy-Bi-Wire test data input/output during programming and test                              |  |  |  |

| TEST/                  | 11       | 10  | 17 | I   | Selects test mode for JTAG pins on port 1. The device protection fuse is connected to TEST. |  |  |  |

| SBWTCK                 |          |     |    |     | Spy-Bi-Wire test clock input during programming and test                                    |  |  |  |

| DVCC                   | 1        | 16  | 1  | NA  | Supply voltage                                                                              |  |  |  |

| AVCC                   | -        | 15  | -  | NA  | Supply voltage                                                                              |  |  |  |

| DVSS                   | 14       | 14  | 20 | NA  | Ground reference                                                                            |  |  |  |

| AVSS                   | -        | 13  | -  | NA  | Ground reference                                                                            |  |  |  |

| NC                     | -        | -   | -  | NA  | Not connected                                                                               |  |  |  |

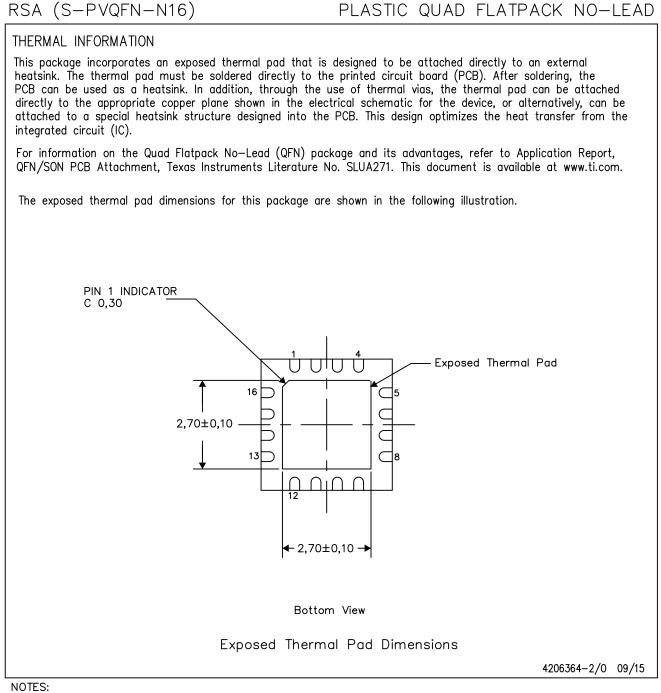

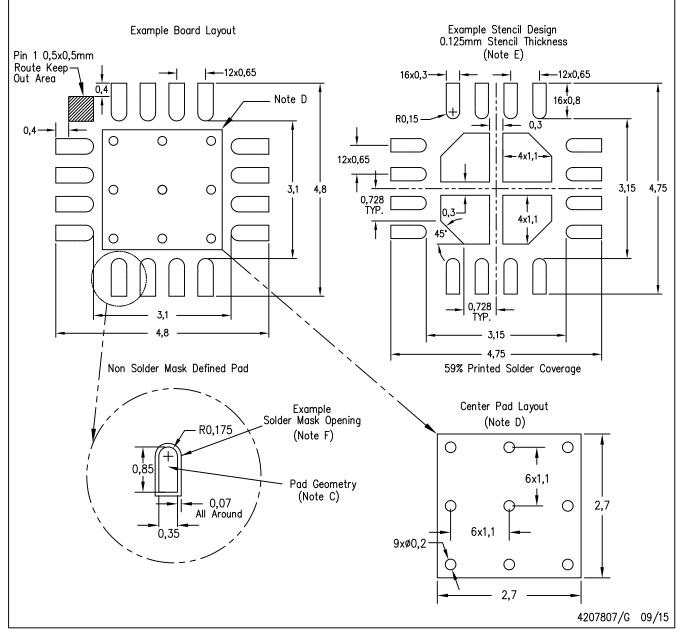

| QFN Pad                | -        | Pad | -  | NA  | QFN package pad connection to V <sub>SS</sub> recommended.                                  |  |  |  |

(2) (3)

TDO or TDI is selected via JTAG instruction. If XOUT/P2.7 is used as an input, excess current flows until P2SEL.7 is cleared. This is due to the oscillator output driver connection to this pad after reset.

www.ti.com

SLAS722G - DECEMBER 2010 - REVISED MAY 2013

# SHORT-FORM DESCRIPTION

## CPU

The MSP430 CPU has a 16-bit RISC architecture that is highly transparent to the application. All operations, other than program-flow instructions, are performed as register operations in conjunction with seven addressing modes for source operand and four addressing modes for destination operand.

The CPU is integrated with 16 registers that provide reduced instruction execution time. The register-toregister operation execution time is one cycle of the CPU clock.

Four of the registers, R0 to R3, are dedicated as program counter, stack pointer, status register, and constant generator, respectively. The remaining registers are general-purpose registers.

Peripherals are connected to the CPU using data, address, and control buses, and can be handled with all instructions.

The instruction set consists of the original 51 instructions with three formats and seven address modes and additional instructions for the expanded address range. Each instruction can operate on word and byte data.

#### Instruction Set

The instruction set consists of 51 instructions with three formats and seven address modes. Each instruction can operate on word and byte data. Table 3 shows examples of the three types of instruction formats; Table 4 shows the address modes.

| Program Counter          | PC/R0     |

|--------------------------|-----------|

| Stack Pointer            | SP/R1     |

| Status Register          | SR/CG1/R2 |

| Constant Generator       | CG2/R3    |

| General-Purpose Register | R4        |

| General-Purpose Register | R5        |

| General-Purpose Register | R6        |

| General-Purpose Register | R7        |

| General-Purpose Register | R8        |

| General-Purpose Register | R9        |

| General-Purpose Register | R10       |

| General-Purpose Register | R11       |

| General-Purpose Register | R12       |

| General-Purpose Register | R13       |

| General-Purpose Register | R14       |

| General-Purpose Register | R15       |

#### **Table 3. Instruction Word Formats**

| FORMAT                            | EXAMPLE   | OPERATION             |

|-----------------------------------|-----------|-----------------------|

| Dual operands, source-destination | ADD R4,R5 | R4 + R5> R5           |

| Single operands, destination only | CALL R8   | PC ->(TOS), R8-> PC   |

| Relative jump, un/conditional     | JNE       | Jump-on-equal bit = 0 |

#### Table 4. Address Mode Descriptions<sup>(1)</sup>

| ADDRESS MODE           | S            | D | SYNTAX          | EXAMPLE          | OPERATION                          |  |  |  |  |

|------------------------|--------------|---|-----------------|------------------|------------------------------------|--|--|--|--|

| Register               | $\checkmark$ | ~ | MOV Rs,Rd       | MOV R10,R11      | R10 – -> R11                       |  |  |  |  |

| Indexed                | ✓            | ~ | MOV X(Rn),Y(Rm) | MOV 2(R5),6(R6)  | M(2+R5)> M(6+R6)                   |  |  |  |  |

| Symbolic (PC relative) | ✓            | ~ | MOV EDE,TONI    |                  | M(EDE) – -> M(TONI)                |  |  |  |  |

| Absolute               | ✓            | ~ | MOV &MEM,&TCDAT |                  | M(MEM) – -> M(TCDAT)               |  |  |  |  |

| Indirect               | 1            |   | MOV @Rn,Y(Rm)   | MOV @R10,Tab(R6) | M(R10) – -> M(Tab+R6)              |  |  |  |  |

| Indirect autoincrement | 1            |   | MOV @Rn+,Rm     | MOV @R10+,R11    | M(R10) – -> R11<br>R10 + 2– -> R10 |  |  |  |  |

| Immediate              | 1            |   | MOV #X,TONI     | MOV #45,TONI     | #45 – -> M(TONI)                   |  |  |  |  |

(1) S = source, D = destination

# TEXAS INSTRUMENTS

www.ti.com

## **Operating Modes**

The MSP430 has one active mode and five software-selectable low-power modes of operation. An interrupt event can wake up the device from any of the low-power modes, service the request, and restore back to the low-power mode on return from the interrupt program.

The following six operating modes can be configured by software:

- Active mode (AM)

- All clocks are active

- Low-power mode 0 (LPM0)

- CPU is disabled

- ACLK and SMCLK remain active, MCLK is disabled

- Low-power mode 1 (LPM1)

- CPU is disabled

- ACLK and SMCLK remain active, MCLK is disabled

- DCO's dc generator is disabled if DCO not used in active mode

- Low-power mode 2 (LPM2)

- CPU is disabled

- MCLK and SMCLK are disabled

- DCO's dc generator remains enabled

- ACLK remains active

- Low-power mode 3 (LPM3)

- CPU is disabled

- MCLK and SMCLK are disabled

- DCO's dc generator is disabled

- ACLK remains active

- Low-power mode 4 (LPM4)

- CPU is disabled

- ACLK is disabled

- MCLK and SMCLK are disabled

- DCO's dc generator is disabled

- Crystal oscillator is stopped

## Interrupt Vector Addresses

The interrupt vectors and the power-up starting address are located in the address range 0FFFFh to 0FFC0h. The vector contains the 16-bit address of the appropriate interrupt handler instruction sequence.

If the reset vector (located at address 0FFFEh) contains 0FFFFh (for example, if flash is not programmed) the CPU goes into LPM4 immediately after power-up.

| INTERRUPT SOURCE                                                                                       | INTERRUPT FLAG                                    | SYSTEM<br>INTERRUPT                                | WORD<br>ADDRESS     | PRIORITY       |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------------------------------------------|---------------------|----------------|--|--|--|--|--|--|

| Power-Up<br>External Reset<br>Watchdog Timer+<br>Flash key violation<br>PC out-of-range <sup>(1)</sup> | PORIFG<br>RSTIFG<br>WDTIFG<br>KEYV <sup>(2)</sup> | Reset                                              | OFFFEh              | 31, highest    |  |  |  |  |  |  |

| NMI<br>Oscillator fault<br>Flash memory access violation                                               | NMIIFG<br>OFIFG<br>ACCVIFG <sup>(2)(3)</sup>      | (non)-maskable<br>(non)-maskable<br>(non)-maskable | 0FFFCh              | 30             |  |  |  |  |  |  |

|                                                                                                        |                                                   |                                                    | 0FFFAh              | 29             |  |  |  |  |  |  |

|                                                                                                        |                                                   |                                                    | 0FFF8h              | 28             |  |  |  |  |  |  |

| Comparator_A+                                                                                          | CAIFG <sup>(4)</sup>                              | maskable                                           | 0FFF6h              | 27             |  |  |  |  |  |  |

| Watchdog Timer+ WDTIFG                                                                                 |                                                   | maskable                                           | 0FFF4h              | 26             |  |  |  |  |  |  |

| Timer0_A3                                                                                              | TACCR0 CCIFG <sup>(4)</sup>                       | maskable                                           | 0FFF2h              | 25             |  |  |  |  |  |  |

| Timer0_A3                                                                                              | TACCR2 TACCR1 CCIFG. TAIFG <sup>(2)(4)</sup>      | maskable                                           | 0FFF0h              | 24             |  |  |  |  |  |  |

|                                                                                                        |                                                   |                                                    | 0FFEEh              | 23             |  |  |  |  |  |  |

|                                                                                                        |                                                   |                                                    | 0FFECh              | 22             |  |  |  |  |  |  |

| ADC10 <sup>(5)</sup>                                                                                   | ADC10IFG <sup>(4)(5)</sup>                        | maskable                                           | 0FFEAh              | 21             |  |  |  |  |  |  |

| USI                                                                                                    | USIIFG, USISTTIFG <sup>(2)(4)</sup>               | maskable                                           | 0FFE8h              | 20             |  |  |  |  |  |  |

| I/O Port P2 (up to eight flags)                                                                        | P2IFG.0 to P2IFG.7 <sup>(2)(4)</sup>              | maskable                                           | 0FFE6h              | 19             |  |  |  |  |  |  |

| I/O Port P1 (up to eight flags)                                                                        | P1IFG.0 to P1IFG.7 <sup>(2)(4)</sup>              | maskable                                           | 0FFE4h              | 18             |  |  |  |  |  |  |

|                                                                                                        |                                                   |                                                    | 0FFE2h              | 17             |  |  |  |  |  |  |

|                                                                                                        |                                                   |                                                    | 0FFE0h              | 16             |  |  |  |  |  |  |

| See <sup>(6)</sup>                                                                                     |                                                   |                                                    | 0FFDEh to<br>0FFC0h | 15 to 0, lowes |  |  |  |  |  |  |

#### Table 5. Interrupt Sources, Flags, and Vectors

(1) A reset is generated if the CPU tries to fetch instructions from within the module register memory address range (0h to 01FFh) or from within unused address ranges.

(2) Multiple source flags

(3) (non)-maskable: the individual interrupt-enable bit can disable an interrupt event, but the general interrupt enable cannot.

(4) Interrupt flags are located in the module.

(5) MSP430G2x52 only

(6) The interrupt vectors at addresses 0FFDEh to 0FFC0h are not used in this device and can be used for regular program code if necessary.

www.ti.com

# **Special Function Registers (SFRs)**

Most interrupt and module enable bits are collected into the lowest address space. Special function register bits not allocated to a functional purpose are not physically present in the device. Simple software access is provided with this arrangement.

| Legend | rw:       | Bit can be read and written.                            |

|--------|-----------|---------------------------------------------------------|

|        | rw-0,1:   | Bit can be read and written. It is reset or set by PUC. |

|        | rw-(0,1): | Bit can be read and written. It is reset or set by POR. |

|        |           | SFR bit is not present in device.                       |

## Table 6. Interrupt Enable Register 1 and 2

| Address | 7          | 6                                                                                                                                      | 5      | 4     | 3 | 2 | 1    | 0     |  |  |  |

|---------|------------|----------------------------------------------------------------------------------------------------------------------------------------|--------|-------|---|---|------|-------|--|--|--|

| 00h     |            |                                                                                                                                        | ACCVIE | NMIIE |   |   | OFIE | WDTIE |  |  |  |

|         |            |                                                                                                                                        | rw-0   | rw-0  |   |   | rw-0 | rw-0  |  |  |  |

| WDTIE   |            | Watchdog Timer interrupt enable. Inactive if watchdog mode is selected. Active if Watchdog Timer is configured in interval timer mode. |        |       |   |   |      |       |  |  |  |

| OFIE    | Oscillator | fault interrupt e                                                                                                                      | enable |       |   |   |      |       |  |  |  |

| NMIIE   | (Non)mas   | (Non)maskable interrupt enable                                                                                                         |        |       |   |   |      |       |  |  |  |

| ACCVIE  | Flash acc  | Flash access violation interrupt enable                                                                                                |        |       |   |   |      |       |  |  |  |

|         |            |                                                                                                                                        |        |       |   |   |      |       |  |  |  |

| Address | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|---|---|---|---|---|---|---|---|

| 01h     |   |   |   |   |   |   |   |   |

#### Table 7. Interrupt Flag Register 1 and 2

| Address | 7           | 6                                                                                                                                            | 5                                       | 4                              | 3                | 2              | 1                          | 0      |  |

|---------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------|------------------|----------------|----------------------------|--------|--|

| 02h     |             |                                                                                                                                              |                                         | NMIIFG                         | RSTIFG           | PORIFG         | OFIFG                      | WDTIFG |  |

|         |             |                                                                                                                                              |                                         | rw-0                           | rw-(0)           | rw-(1)         | rw-1                       | rw-(0) |  |

| WDTIFG  |             |                                                                                                                                              | verflow (in watch<br>or a reset conditi |                                |                  |                |                            |        |  |

| OFIFG   | Flag set or | n oscillator faul                                                                                                                            | t.                                      |                                |                  |                |                            |        |  |

| PORIFG  | Power-On    | Power-On Reset interrupt flag. Set on V <sub>CC</sub> power-up.                                                                              |                                         |                                |                  |                |                            |        |  |

| RSTIFG  | External re | eset interrupt fla                                                                                                                           | ag. Set on a res                        | et condition at $\overline{F}$ | RST/NMI pin in r | eset mode. Res | et on V <sub>CC</sub> powe | er-up. |  |

| NMIIFG  | Set via RS  | External reset interrupt flag. Set on a reset condition at RST/NMI pin in reset mode. Reset on V <sub>CC</sub> power-up. Set via RST/NMI pin |                                         |                                |                  |                |                            |        |  |

| Addross | 7           | 6                                                                                                                                            | F                                       | 4                              | 2                | 2              | 1                          | 0      |  |

| Address | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|---|---|---|---|---|---|---|---|

| 03h     |   |   |   |   |   |   |   |   |

**Memory Organization**

SLAS722G - DECEMBER 2010 - REVISED MAY 2013

www.ti.com

|                        |           |                            | lemory organization        |                            |                            |

|------------------------|-----------|----------------------------|----------------------------|----------------------------|----------------------------|

|                        |           | MSP430G2112<br>MSP430G2152 | MSP430G2212<br>MSP430G2252 | MSP430G2312<br>MSP430G2352 | MSP430G2412<br>MSP430G2452 |

| Memory                 | Size      | 1kB                        | 2kB                        | 4kB                        | 8kB                        |

| Main: interrupt vector | Flash     | 0xFFFF to 0xFFC0           | 0xFFFF to 0xFFC0           | 0xFFFF to 0xFFC0           | 0xFFFF to 0xFFC0           |

| Main: code memory      | Flash     | 0xFFFF to 0xFC00           | 0xFFFF to 0xF800           | 0xFFFF to 0xF000           | 0xFFFF to 0xE000           |

| Information memory     | Size      | 256 Byte                   | 256 Byte                   | 256 Byte                   | 256 Byte                   |

|                        | Flash     | 010FFh to 01000h           | 010FFh to 01000h           | 010FFh to 01000h           | 010FFh to 01000h           |

| RAM                    | Size      | 128 B                      | 256 B                      | 256 B                      | 256 B                      |

|                        |           | 0x027F to 0x0200           | 0x02FF to 0x0200           | 0x02FF to 0x0200           | 0x02FF to 0x0200           |

| Peripherals            | 16-bit    | 01FFh to 0100h             | 01FFh to 0100h             | 01FFh to 0100h             | 01FFh to 0100h             |

|                        | 8-bit     | 0FFh to 010h               | 0FFh to 010h               | 0FFh to 010h               | 0FFh to 010h               |

|                        | 8-bit SFR | 0Fh to 00h                 | 0Fh to 00h                 | 0Fh to 00h                 | 0Fh to 00h                 |

## Table 8. Memory Organization

# **Flash Memory**

The flash memory can be programmed via the Spy-Bi-Wire/JTAG port or in-system by the CPU. The CPU can perform single-byte and single-word writes to the flash memory. Features of the flash memory include:

- Flash memory has n segments of main memory and four segments of information memory (A to D) of 64 bytes each. Each segment in main memory is 512 bytes in size.

- Segments 0 to n may be erased in one step, or each segment may be individually erased.

- Segments A to D can be erased individually or as a group with segments 0 to n. Segments A to D are also called *information memory*.

- Segment A contains calibration data. After reset, segment A is protected against programming and erasing. It can be unlocked, but care should be taken not to erase this segment if the device-specific calibration data is required.

# Peripherals

Peripherals are connected to the CPU through data, address, and control buses and can be handled using all instructions. For complete module descriptions, see the *MSP430x2xx Family User's Guide* (SLAU144).

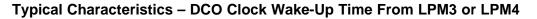

### **Oscillator and System Clock**

The clock system is supported by the basic clock module that includes support for a 32768-Hz watch crystal oscillator, an internal very-low-power low-frequency oscillator and an internal digitally controlled oscillator (DCO). The basic clock module is designed to meet the requirements of both low system cost and low power consumption. The internal DCO provides a fast turn-on clock source and stabilizes in less than 1  $\mu$ s. The basic clock module provides the following clock signals:

- Auxiliary clock (ACLK), sourced either from a 32768-Hz watch crystal or the internal LF oscillator.

- Main clock (MCLK), the system clock used by the CPU.

- Sub-Main clock (SMCLK), the sub-system clock used by the peripheral modules.

The DCO settings to calibrate the DCO output frequency are stored in the information memory segment A.

#### Calibration Data Stored in Information Memory Segment A

Calibration data is stored for both the DCO and for ADC10 organized in a tag-length-value structure.

|             | Table 5. Tags osca by the Abo ballbration Tags |             |                                                                             |  |  |  |  |

|-------------|------------------------------------------------|-------------|-----------------------------------------------------------------------------|--|--|--|--|

| NAME        | ADDRESS                                        | DESCRIPTION |                                                                             |  |  |  |  |

| TAG_DCO_30  | 0x10F6                                         | 0x01        | DCO frequency calibration at $V_{CC}$ = 3 V and $T_A$ = 30°C at calibration |  |  |  |  |

| TAG_ADC10_1 | 0x10DA                                         | 0x10        | ADC10_1 calibration tag                                                     |  |  |  |  |

| TAG_EMPTY   | -                                              | 0xFE        | Identifier for empty memory areas                                           |  |  |  |  |

## Table 9. Tags Used by the ADC Calibration Tags

#### Table 10. Labels Used by the ADC Calibration Tags

| LABEL                 | CONDITION AT CALIBRATION / DESCRIPTION                           | SIZE | ADDRESS<br>OFFSET |

|-----------------------|------------------------------------------------------------------|------|-------------------|

| CAL_ADC_25T85         | INCHx = 0x1010, REF2_5 = 1, T <sub>A</sub> = 85°C                | word | 0x0010            |

| CAL_ADC_25T30         | INCHx = 0x1010, REF2_5 = 1, T <sub>A</sub> = 30°C                | word | 0x000E            |

| CAL_ADC_25VREF_FACTOR | REF2_5 = 1, $T_A = 30^{\circ}C$ , $I_{(VREF+)} = 1$ mA           | word | 0x000C            |

| CAL_ADC_15T85         | INCHx = 0x1010, REF2_5 = 0, T <sub>A</sub> = 85°C                | word | 0x000A            |

| CAL_ADC_15T30         | INCHx = 0x1010, REF2_5 = 0, T <sub>A</sub> = 30°C                | word | 0x0008            |

| CAL_ADC_15VREF_FACTOR | REF2_5 = 0, $T_A = 30^{\circ}C$ , $I_{(VREF+)} = 0.5 \text{ mA}$ | word | 0x0006            |

| CAL_ADC_OFFSET        | External VREF = 1.5 V, f <sub>(ADC10CLK)</sub> = 5 MHz           | word | 0x0004            |

| CAL_ADC_GAIN_FACTOR   | External VREF = 1.5 V, f <sub>(ADC10CLK)</sub> = 5 MHz           | word | 0x0002            |

| CAL_BC1_1MHz          | -                                                                | byte | 0x0009            |

| CAL_DCO_1MHz          | -                                                                | byte | 0x00008           |

| CAL_BC1_8MHz          | -                                                                | byte | 0x0007            |

| CAL_DCO_8MHz          | -                                                                | byte | 0x0006            |

| CAL_BC1_12MHz         | -                                                                | byte | 0x0005            |

| CAL_DCO_12MHz         | -                                                                | byte | 0x0004            |

| CAL_BC1_16MHz         | -                                                                | byte | 0x0003            |

| CAL_DCO_16MHz         | -                                                                | byte | 0x0002            |

#### **Main DCO Characteristics**

- All ranges selected by RSELx overlap with RSELx + 1: RSELx = 0 overlaps RSELx = 1, ..., RSELx = 14 overlaps RSELx = 15.

- DCO control bits DCOx have a step size as defined by parameter S<sub>DCO</sub>.

- Modulation control bits MODx select how often f<sub>DCO(RSEL,DCO+1)</sub> is used within the period of 32 DCOCLK cycles. The frequency f<sub>DCO(RSEL,DCO)</sub> is used for the remaining cycles. The frequency is an average equal to: <sup>32 × f</sup><sub>DCO(RSEL,DCO)</sub> <sup>× f</sup><sub>DCO(RSEL,DCO+1)</sub>

$f_{average} = \frac{DOC(ROLE, DOC)}{MOD \times f_{DCO(RSEL, DCO)} + (32 - MOD) \times f_{DCO(RSEL, DCO+1)}}$

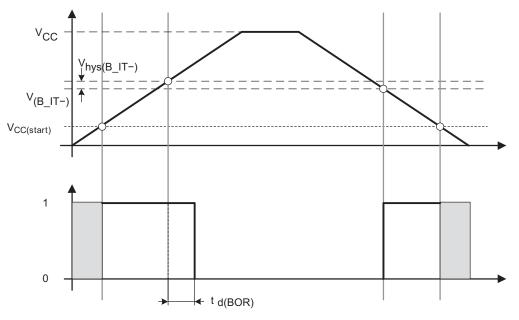

### Brownout

The brownout circuit is implemented to provide the proper internal reset signal to the device during power on and power off.

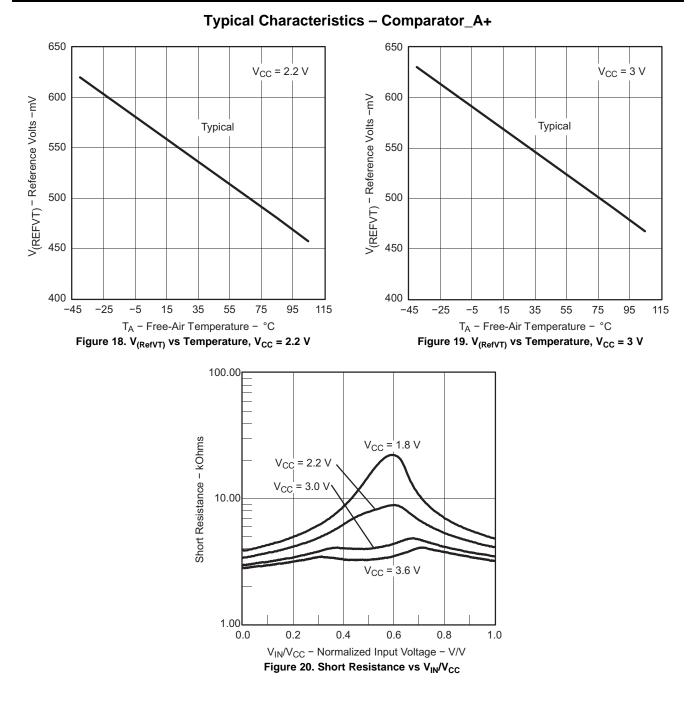

# **Digital I/O**

There are two 8-bit I/O ports implemented:

- All individual I/O bits are independently programmable.

- Any combination of input, output, and interrupt condition(port P1 and port P2 only) is possible.

- Edge-selectable interrupt input capability for all the eight bits of port P1 and port P2, if available.

- Read/write access to port-control registers is supported by all instructions.

- Each I/O has an individually programmable pullup/pulldown resistor.

- Each I/O has an individually programmable pin-oscillator enable bit to enable low-cost capacitive-touch detection.

#### WDT+ Watchdog Timer

The primary function of the watchdog timer (WDT+) module is to perform a controlled system restart after a software problem occurs. If the selected time interval expires, a system reset is generated. If the watchdog function is not needed in an application, the module can be disabled or configured as an interval timer and can generate interrupts at selected time intervals.

#### Timer0\_A3

Timer0\_A3 is a 16-bit timer/counter with three capture/compare registers. Timer0\_A3 can support multiple capture/compares, PWM outputs, and interval timing. Timer0\_A3 also has extensive interrupt capabilities. Interrupts may be generated from the counter on overflow conditions and from each of the capture/compare registers.

| INPU      | JT PIN NUME | BER    | DEVICE          | MODULE          | MODULE | MODULE           | OUTPUT PIN NUM |         | IBER    |        |        |        |

|-----------|-------------|--------|-----------------|-----------------|--------|------------------|----------------|---------|---------|--------|--------|--------|

| N20, PW20 | PW14        | RSA16  | INPUT<br>SIGNAL | INPUT<br>NAME   | BLOCK  | OUTPUT<br>SIGNAL | N20, PW20      | PW14    | RSA16   |        |        |        |

| P1.0-2    | P1.0-2      | P1.0-1 | TACLK           | TACLK           |        |                  |                |         |         |        |        |        |

|           |             |        | ACLK            | ACLK            | Timor  | NIA              |                |         |         |        |        |        |

|           |             |        | SMCLK           | SMCLK           | Timer  | NA               |                |         |         |        |        |        |

| PinOsc    | PinOsc      | PinOsc |                 | INCLK           |        |                  |                |         |         |        |        |        |

| P1.1-3    | P1.1-3      | P1.1-2 | TA0.0           | CCI0A           |        |                  | P1.1-3         | P1.1-3  | P1.1-2  |        |        |        |

|           |             |        | ACLK            | CCI0B           | CCR0   | 0000             | CCI0B          | CCI0B   | TAO     | P1.5-7 | P1.5-7 | P1.5-6 |

|           |             |        | V <sub>SS</sub> | GND             | CCRU   | TA0              |                |         |         |        |        |        |

|           |             |        | V <sub>CC</sub> | V <sub>CC</sub> |        |                  |                |         |         |        |        |        |

| P1.2-4    | P1.2-4      | P1.2-3 | TA0.1           | CCI1A           |        | TA1              | P1.2-4         | P1.2-4  | P1.2-3  |        |        |        |

|           |             |        | CAOUT           | CCI1B           | 0004   |                  | P1.6-14        | P1.6-8  | P1.6-7  |        |        |        |

|           |             |        | V <sub>SS</sub> | GND             | CCR1   |                  | P2.6-19        | P2.6-12 | P2.6-12 |        |        |        |

|           |             |        | V <sub>CC</sub> | V <sub>CC</sub> |        |                  |                |         |         |        |        |        |

| P1.4-6    | P1.4-6      | P1.4-5 | TA0.2           | CCI2A           | 00000  |                  | P1.4-6         | P1.4-6  | P1.4-5  |        |        |        |

| PinOsc    | PinOsc      | PinOsc | TA0.2           | CCI2B           |        |                  |                |         |         |        |        |        |

|           |             |        | V <sub>SS</sub> | GND             | CCR2   | TA2              |                |         |         |        |        |        |

|           |             |        | V <sub>CC</sub> | V <sub>CC</sub> |        |                  |                |         |         |        |        |        |

|  | Table 11. | Timer0 | A3 | Signal | Connections <sup>(1)</sup> |

|--|-----------|--------|----|--------|----------------------------|

|--|-----------|--------|----|--------|----------------------------|

(1) Only one pin-oscillator must be enabled at a time.

#### USI

The universal serial interface (USI) module is used for serial data communication and provides the basic hardware for synchronous communication protocols like SPI and I2C.

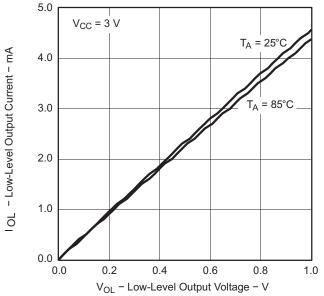

#### Comparator\_A+

The primary function of the Comparator\_A+module is to support precision slope analog-to-digital conversions, battery-voltage supervision, and monitoring of external analog signals.

### ADC10 (MSP430G2x52 only)

The ADC10 module supports fast, 10-bit analog-to-digital conversions. The module implements a 10-bit SAR core, sample select control, reference generator and data transfer controller, or DTC, for automatic conversion result handling, allowing ADC samples to be converted and stored without any CPU intervention.

## **Peripheral File Map**

| MODULE                           | REGISTER DESCRIPTION            | REGISTER<br>NAME | OFFSET |

|----------------------------------|---------------------------------|------------------|--------|

| ADC10 (MSP430G2x52 devices only) | ADC data transfer start address | ADC10SA          | 01BCh  |

|                                  | ADC memory                      | ADC10MEM         | 01B4h  |

|                                  | ADC control register 1          | ADC10CTL1        | 01B2h  |

|                                  | ADC control register 0          | ADC10CTL0        | 01B0h  |

| Timer0_A3                        | Capture/compare register        | TACCR2           | 0176h  |

|                                  | Capture/compare register        | TACCR1           | 0174h  |

|                                  | Capture/compare register        | TACCR0           | 0172h  |

|                                  | Timer_A register                | TAR              | 0170h  |

|                                  | Capture/compare control         | TACCTL2          | 0166h  |

|                                  | Capture/compare control         | TACCTL1          | 0164h  |

|                                  | Capture/compare control         | TACCTL0          | 0162h  |

|                                  | Timer_A control                 | TACTL            | 0160h  |

|                                  | Timer_A interrupt vector        | TAIV             | 012Eh  |

| Flash Memory                     | Flash control 3                 | FCTL3            | 012Ch  |

|                                  | Flash control 2                 | FCTL2            | 012Ah  |

|                                  | Flash control 1                 | FCTL1            | 0128h  |

| Watchdog Timer+                  | Watchdog/timer control          | WDTCTL           | 0120h  |

# Table 12. Peripherals With Word Access

SLAS722G - DECEMBER 2010 - REVISED MAY 2013

www.ti.com

# Table 13. Peripherals With Byte Access

| MODULE                           | REGISTER DESCRIPTION                 | REGISTER<br>NAME | OFFSET |

|----------------------------------|--------------------------------------|------------------|--------|

| ADC10 (MSP430G2x52 devices only) | Analog enable 1                      | ADC10AE1         | 04Bh   |

|                                  | Analog enable 0                      | ADC10AE0         | 04Ah   |

|                                  | ADC data transfer control register 1 | ADC10DTC1        | 049h   |

|                                  | ADC data transfer control register 0 | ADC10DTC0        | 048h   |

| USI                              | USI control 0                        | USICTL0          | 078h   |

|                                  | USI control 1                        | USICTL1          | 079h   |

|                                  | USI clock control                    | USICKCTL         | 07Ah   |

|                                  | USI bit counter                      | USICNT           | 07Bh   |

|                                  | USI shift register                   | USISR            | 07Ch   |

| Comparator_A+                    | Comparator_A+ port disable           | CAPD             | 05Bh   |

|                                  | Comparator_A+ control 2              | CACTL2           | 05Ah   |

|                                  | Comparator_A+ control 1              | CACTL1           | 059h   |

| Basic Clock System+              | Basic clock system control 3         | BCSCTL3          | 053h   |

|                                  | Basic clock system control 2         | BCSCTL2          | 058h   |

|                                  | Basic clock system control 1         | BCSCTL1          | 057h   |

|                                  | DCO clock frequency control          | DCOCTL           | 056h   |

| Port P2                          | Port P2 selection 2                  | P2SEL2           | 042h   |

|                                  | Port P2 resistor enable              | P2REN            | 02Fh   |

|                                  | Port P2 selection                    | P2SEL            | 02Eh   |

|                                  | Port P2 interrupt enable             | P2IE             | 02Dh   |

|                                  | Port P2 interrupt edge select        | P2IES            | 02Ch   |

|                                  | Port P2 interrupt flag               | P2IFG            | 02Bh   |

|                                  | Port P2 direction                    | P2DIR            | 02Ah   |

|                                  | Port P2 output                       | P2OUT            | 029h   |

|                                  | Port P2 input                        | P2IN             | 028h   |

| Port P1                          | Port P1 selection 2                  | P1SEL2           | 041h   |

|                                  | Port P1 resistor enable              | P1REN            | 027h   |

|                                  | Port P1 selection                    | P1SEL            | 026h   |

|                                  | Port P1 interrupt enable             | P1IE             | 025h   |

|                                  | Port P1 interrupt edge select        | P1IES            | 024h   |

|                                  | Port P1 interrupt flag               | P1IFG            | 023h   |

|                                  | Port P1 direction                    | P1DIR            | 022h   |

|                                  | Port P1 output                       | P1OUT            | 021h   |

|                                  | Port P1 input                        | P1IN             | 020h   |

| Special Function                 | SFR interrupt flag 2                 | IFG2             | 003h   |

| -                                | SFR interrupt flag 1                 | IFG1             | 002h   |

|                                  | SFR interrupt enable 2               | IE2              | 001h   |

|                                  | SFR interrupt enable 1               | IE1              | 000h   |

www.ti.com

## Absolute Maximum Ratings<sup>(1)</sup>

| Voltage applied at $V_{CC}$ to $V_{SS}$                    |                     | –0.3 V to 4.1 V                   |

|------------------------------------------------------------|---------------------|-----------------------------------|

| Voltage applied to any pin <sup>(2)</sup>                  |                     | -0.3 V to V <sub>CC</sub> + 0.3 V |

| Diode current at any device pin                            |                     | ±2 mA                             |

|                                                            | Unprogrammed device | –55°C to 150°C                    |

| Storage temperature range, T <sub>stg</sub> <sup>(3)</sup> | Programmed device   | –55°C to 150°C                    |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages referenced to V<sub>SS</sub>. The JTAG fuse-blow voltage, V<sub>FB</sub>, is allowed to exceed the absolute maximum rating. The voltage is applied to the TEST pin when blowing the JTAG fuse.

(3) Higher temperature may be applied during board soldering according to the current JEDEC J-STD-020 specification with peak reflow temperatures not higher than classified on the device label on the shipping boxes or reels.

# **Recommended Operating Conditions**

Typical values are specified at  $V_{CC}$  = 3.3 V and  $T_A$  = 25°C (unless otherwise noted)

|                     |                                                                                       |                                                     | MIN | NOM | MAX | UNIT |

|---------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------|-----|-----|-----|------|

| V                   | Supply veltage                                                                        | During program execution                            | 1.8 |     | 3.6 | V    |

| V <sub>CC</sub>     | Supply voltage                                                                        | During flash programming/erase                      | 2.2 |     | 3.6 | v    |

| V <sub>SS</sub>     | Supply voltage                                                                        |                                                     |     | 0   |     | V    |

| T <sub>A</sub>      | Operating free-air temperature                                                        |                                                     | -40 |     | 85  | °C   |

|                     |                                                                                       | V <sub>CC</sub> = 1.8 V,<br>Duty cycle = 50% ± 10%  | dc  |     | 6   |      |

| f <sub>SYSTEM</sub> | Processor frequency (maximum MCLK frequency using the USART module) <sup>(1)(2)</sup> | $V_{CC} = 2.7 \text{ V},$<br>Duty cycle = 50% ± 10% | dc  |     | 12  | MHz  |

|                     |                                                                                       | V <sub>CC</sub> = 3.3 V,<br>Duty cycle = 50% ± 10%  | dc  |     | 16  |      |

(1) The MSP430 CPU is clocked directly with MCLK. Both the high and low phase of MCLK must not exceed the pulse width of the specified maximum frequency.

(2) Modules might have a different maximum input clock specification. See the specification of the respective module in this data sheet.

Note: Minimum processor frequency is defined by system clock. Flash program or erase operations require a minimum V<sub>CC</sub> of 2.2 V.

# www.ti.com

# **Electrical Characteristics**

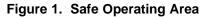

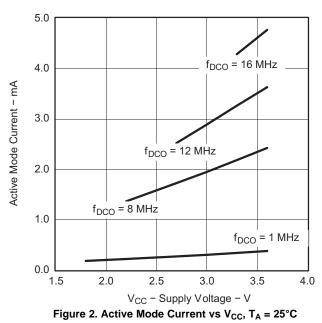

# Active Mode Supply Current Into V<sub>cc</sub> Excluding External Current

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)<sup>(1)(2)</sup>

| PARAMETER                                              | TEST CONDITIONS                                   | V <sub>cc</sub> | MIN | TYP | MAX               | UNIT |

|--------------------------------------------------------|---------------------------------------------------|-----------------|-----|-----|-------------------|------|

|                                                        | $f_{DCO} = f_{MCLK} = f_{SMCLK} = 1 \text{ MHz},$ | 2.2 V           |     | 220 |                   |      |

| Active mode (A<br>I <sub>AM,1MHz</sub> current (1 MHz) |                                                   | 3 V             |     | 320 | <b>MAX</b><br>400 | μΑ   |

(1)

All inputs are tied to 0 V or to  $V_{CC}$ . Outputs do not source or sink any current. The currents are characterized with a Micro Crystal CC4V-T1A SMD crystal with a load capacitance of 9 pF. The internal and external (2)load capacitance is chosen to closely match the required 9 pF.

# Typical Characteristics – Active Mode Supply Current (Into V<sub>cc</sub>)

#### SLAS722G - DECEMBER 2010 - REVISED MAY 2013

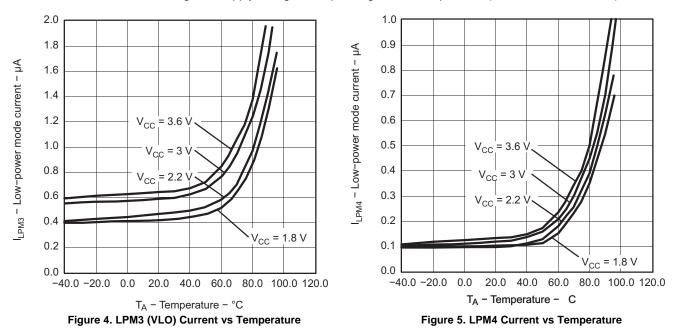

# Low-Power Mode Supply Currents (Into V<sub>cc</sub>) Excluding External Current

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)<sup>(1) (2)</sup>

| Р                       | ARAMETER                                          | TEST CONDITIONS                                                            | T <sub>A</sub> | V <sub>cc</sub> | MIN TYP | MAX | UNIT |

|-------------------------|---------------------------------------------------|----------------------------------------------------------------------------|----------------|-----------------|---------|-----|------|

| I <sub>LPM0,1MHz</sub>  | Low-power mode 0<br>(LPM0) current <sup>(3)</sup> |                                                                            | 25°C           | 2.2 V           | 55      |     | μΑ   |

| I <sub>LPM2</sub>       | Low-power mode 2<br>(LPM2) current <sup>(4)</sup> |                                                                            | 25°C           | 2.2 V           | 22      |     | μΑ   |

| I <sub>LPM3,LFXT1</sub> | Low-power mode 3<br>(LPM3) current <sup>(4)</sup> |                                                                            | 25°C           | 2.2 V           | 0.7     | 1.0 | μA   |

| I <sub>LPM3,VLO</sub>   | Low-power mode 3 current, (LPM3) <sup>(4)</sup>   |                                                                            | 25°C           | 2.2 V           | 0.5     | 0.7 | μA   |

|                         |                                                   | $f_{DCO} = f_{MCLK} = f_{SMCLK} = 0 MHz,$                                  | 25°C           |                 | 0.1     | 0.5 |      |

| I <sub>LPM4</sub>       | Low-power mode 4<br>(LPM4) current <sup>(5)</sup> | f <sub>ACLK</sub> = 0 Hz,<br>CPUOFF = 1, SCG0 = 1, SCG1 = 1,<br>OSCOFF = 1 | 85°C           | 2.2 V           | 0.8     | 1.5 | μA   |

(1) All inputs are tied to 0 V or to  $V_{CC}$ . Outputs do not source or sink any current.

(2) The currents are characterized with a Micro Crystal CC4V-T1A SMD crystal with a load capacitance of 9 pF.

(3) Current for brownout and WDT clocked by SMCLK included.

(4) Current for brownout and WDT clocked by ACLK included.

(5) Current for brownout included.

# **Typical Characteristics Low-Power Mode Supply Currents**

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

www.ti.com

# Schmitt-Trigger Inputs – Ports Px<sup>(1)</sup>

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                   | PARAMETER                                                       | TEST CONDITIONS                                                  | V <sub>cc</sub> | MIN                  | TYP | MAX                  | UNIT |

|-------------------|-----------------------------------------------------------------|------------------------------------------------------------------|-----------------|----------------------|-----|----------------------|------|

| V                 | Depitive going input threshold voltage                          |                                                                  |                 | 0.45 V <sub>CC</sub> |     | 0.75 V <sub>CC</sub> | V    |

| V <sub>IT+</sub>  | Positive-going input threshold voltage                          |                                                                  | 3 V             | 1.35                 |     | 2.25                 | v    |

| V                 | Negative going input threshold voltage                          |                                                                  |                 | 0.25 V <sub>CC</sub> |     | 0.55 V <sub>CC</sub> | Ň    |

| V <sub>IT-</sub>  | Negative-going input threshold voltage                          |                                                                  | 3 V             | 0.75                 |     | 1.65                 | V    |

| V <sub>hys</sub>  | Input voltage hysteresis (V <sub>IT+</sub> – V <sub>IT-</sub> ) |                                                                  | 3 V             | 0.3                  |     | 1                    | V    |

| R <sub>Pull</sub> | Pullup/pulldown resistor                                        | For pullup: $V_{IN} = V_{SS}$<br>For pulldown: $V_{IN} = V_{CC}$ | 3 V             | 20                   | 35  | 50                   | kΩ   |

| CI                | Input capacitance                                               | $V_{IN} = V_{SS} \text{ or } V_{CC}$                             |                 |                      | 5   |                      | pF   |

(1) An external signal sets the interrupt flag every time the minimum interrupt pulse width t<sub>(int)</sub> is met. It may be set even with trigger signals shorter than t<sub>(int)</sub>.

# Leakage Current – Ports Px

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                        | PARAMETER                      | TEST CONDITIONS | V <sub>cc</sub> | MIN MAX | UNIT |

|------------------------|--------------------------------|-----------------|-----------------|---------|------|

| I <sub>lkg(Px.x)</sub> | High-impedance leakage current | (1) (2)         | 3 V             | ±50     | nA   |

(1) The leakage current is measured with V<sub>SS</sub> or V<sub>CC</sub> applied to the corresponding pin(s), unless otherwise noted.

(2) The leakage of the digital port pins is measured individually. The port pin is selected for input, and the pullup/pulldown resistor is disabled.

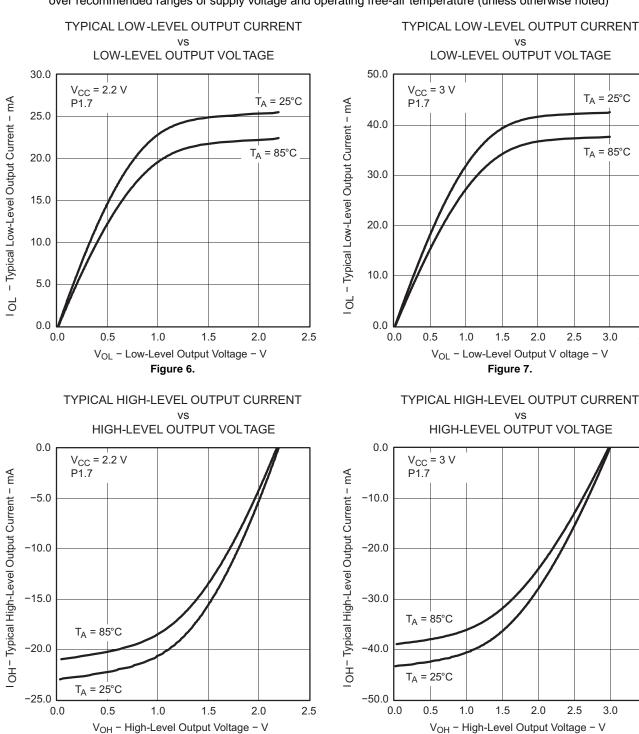

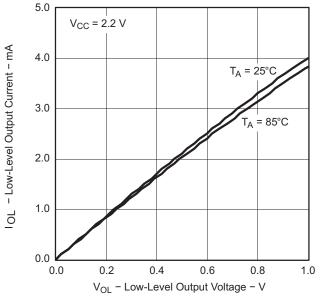

# **Outputs – Ports Px**

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                 | PARAMETER                 | TEST CONDITIONS                     | Vcc | MIN TYP               | MAX | UNIT |

|-----------------|---------------------------|-------------------------------------|-----|-----------------------|-----|------|

| V <sub>OH</sub> | High-level output voltage | $I_{(OHmax)} = -6 \text{ mA}^{(1)}$ | 3 V | V <sub>CC</sub> – 0.3 |     | V    |

| V <sub>OL</sub> | Low-level output voltage  | $I_{(OLmax)} = 6 \text{ mA}^{(1)}$  | 3 V | V <sub>SS</sub> + 0.3 |     | V    |

(1) The maximum total current, I<sub>(OHmax)</sub> and I<sub>(OLmax)</sub>, for all outputs combined should not exceed ±48 mA to hold the maximum voltage drop specified.

# **Output Frequency – Ports Px**

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                       | PARAMETER                         | TEST CONDITIONS                                                   | V <sub>cc</sub> | MIN | TYP | MAX | UNIT |

|-----------------------|-----------------------------------|-------------------------------------------------------------------|-----------------|-----|-----|-----|------|

| f <sub>Px.y</sub>     | Port output frequency (with load) | Px.y, $C_L = 20 \text{ pF}$ , $R_L = 1 \text{ k}\Omega^{(1)}$ (2) | 3 V             |     | 12  |     | MHz  |

| f <sub>Port_CLK</sub> | Clock output frequency            | Px.y, $C_L = 20 \text{ pF}^{(2)}$                                 | 3 V             |     | 16  |     | MHz  |

A resistive divider with two 0.5-kΩ resistors between V<sub>CC</sub> and V<sub>SS</sub> is used as load. The output is connected to the center tap of the divider.

(2) The output voltage reaches at least 10% and 90%  $V_{CC}$  at the specified toggle frequency.

# MSP430G2x52 MSP430G2x12

3.5

3.5

SLAS722G - DECEMBER 2010 - REVISED MAY 2013

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

Figure 8.

Figure 9.

Texas Instruments

SLAS722G - DECEMBER 2010 - REVISED MAY 2013

www.ti.com

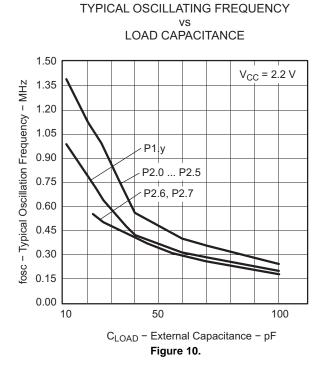

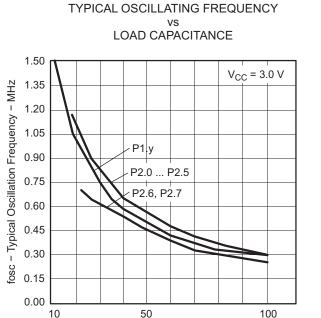

# **Pin-Oscillator Frequency – Ports Px**

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                      | PARAMETER                         | TEST CONDITIONS                                                    | $v_{cc}$ | MIN TYP | MAX | UNIT |  |

|----------------------|-----------------------------------|--------------------------------------------------------------------|----------|---------|-----|------|--|

| fa                   | Dort output opcillation from oppi | P1.y, $C_L = 10 \text{ pF}$ , $R_L = 100 \text{ k}\Omega^{(1)(2)}$ | 3 V      | 1400    |     | kHz  |  |

| fo <sub>P1.x</sub>   | Port output oscillation frequency | P1.y, $C_L = 20 \text{ pF}$ , $R_L = 100 \text{ k}\Omega^{(1)(2)}$ | 3 V      | 900     |     | KITZ |  |

| fa                   | Dort output opcillation from oppi | P2.0 to P2.5, $C_L$ = 10 pF, $R_L$ = 100 k $\Omega^{(1)(2)}$       | 3 V      | 1800    |     | kHz  |  |

| fo <sub>P2.x</sub>   | Port output oscillation frequency | P2.0 to P2.5, $C_L$ = 20 pF, $R_L$ = 100 k $\Omega^{(1)(2)}$       | 3 V      | 1000    |     | KITZ |  |

| fo <sub>P2.6/7</sub> | Port output oscillation frequency | P2.6 and P2.7, $C_L$ = 20 pF, $R_L$ = 100 $k\Omega^{(1)(2)}$       | 3 V      | 700     |     | kHz  |  |

A resistive divider with two 50-kΩ resistors between V<sub>CC</sub> and V<sub>SS</sub> is used as load. The output is connected to the center tap of the divider.

(2) The output voltage oscillates with a typical amplitude of 700 mV at the specified toggle frequency.

# Typical Characteristics – Pin-Oscillator Frequency

C<sub>LOAD</sub> – External Capacitance – pF Figure 11.

#### SLAS722G - DECEMBER 2010 - REVISED MAY 2013

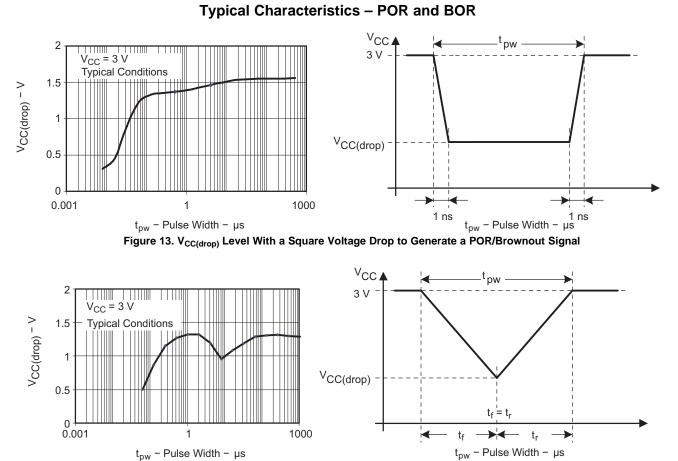

# POR, BOR<sup>(1)(2)</sup>

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                         | PARAMETER                                                         | TEST CONDITIONS              | V <sub>cc</sub> | MIN TYP M                  | ΙAΧ | UNIT |

|-------------------------|-------------------------------------------------------------------|------------------------------|-----------------|----------------------------|-----|------|

| V <sub>CC(start)</sub>  | See Figure 12                                                     | dV <sub>CC</sub> /dt ≤ 3 V/s |                 | 0.7 × V <sub>(B_IT-)</sub> |     | V    |