# 150 mA - ultra low noise - high PSRR linear voltage regulator IC

Datasheet - production data

#### **Features**

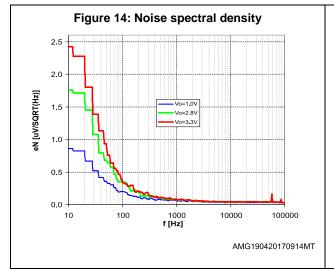

- Ultra low noise: 6.3 μV<sub>RMS</sub> from 10 Hz to 100 kHz

- Input voltage from 2.1 to 5.5 V

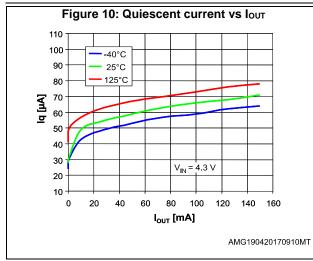

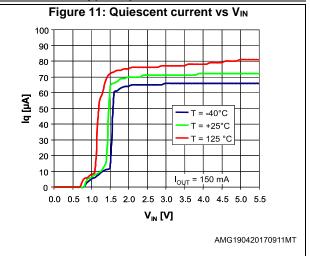

- Very low quiescent current (35 μA typ. at no load, 70 μA typ. at 150 mA load; 2 μA max. in off mode)

- Output voltage tolerance: ± 1% at 25 °C

- 150 mA guaranteed output current

- Wide range of output voltage from 0.8 V to 3.3 V with 100 mV step

- Logic-controlled electronic shutdown

- Compatible with ceramic capacitor (C<sub>OUT</sub> = 0.47 μF)

- No bypass capacitor is required

- Internal current and thermal limit

- Package DFN6 (2 x 2 mm)

- Temperature range: 40 °C to 125 °C

### **Description**

The LDLN015 is an ultra low noise linear regulator which provides 150 mA maximum current from an input voltage ranging from 2.1 V to 5.5 V with a typical dropout voltage of 86 mV. With its  $6.3 \mu V_{RMS}$  noise value in a band from 10 Hz to 100 kHz, the LDLN015 provides a very clean output suitable for ultra sensitive loads. It is stable with ceramic capacitors. High PSRR, low quiescent current and very low noise features make it suitable for low power battery powered applications. Power supply rejection is higher than 90 dB at low frequencies and starts to roll off at 10 kHz. The enable logic control function puts the LDLN015 into shutdown mode allowing a total current consumption lower than 1 µA. The device also includes a short-circuit constant current limiting and thermal protection. Typical applications are noise sensitive loads like ADC, VCO in mobile phones, and personal digital assistants (PDAs).

**Table 1: Device summary**

| Order code   | Output voltage (V) |

|--------------|--------------------|

| LDLN015PU10R | 1.0                |

| LDLN015PU12R | 1.2                |

| LDLN015PU15R | 1.5                |

| LDLN015PU18R | 1.8                |

| LDLN015PU25R | 2.5                |

| LDLN015PU28R | 2.8                |

| LDLN015PU30R | 3.0                |

| LDLN015PU33R | 3.3                |

May 2017 DocID022735 Rev 5 1/16

Contents LDLN015

## Contents

| 1 | Applica  | ntion diagram                       | 3  |

|---|----------|-------------------------------------|----|

| 2 | Pin con  | figuration                          | 4  |

| 3 | Maximu   | ım ratings                          | 5  |

| 4 | Electric | cal characteristics                 | 6  |

| 5 | Typical  | performance characteristics         | 8  |

| 6 | Packag   | e information                       | 12 |

|   | 6.1      | DFN6 (2 x 2 mm) package information | 12 |

|   | 6.2      | DFN6 (2 x 2 mm) packing information | 14 |

| 7 | Revisio  | n history                           | 15 |

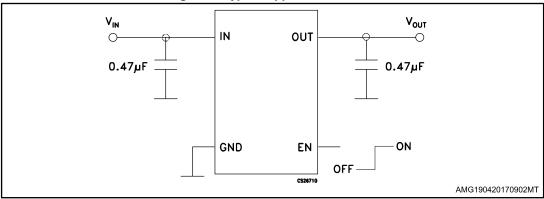

# 1 Application diagram

Figure 1: Block diagram

Figure 2: Typical application circuit

Pin configuration LDLN015

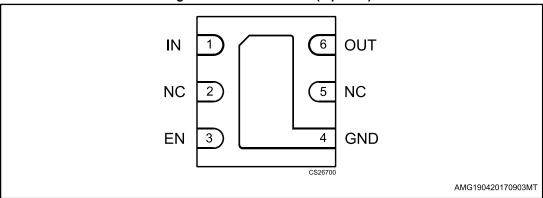

# 2 Pin configuration

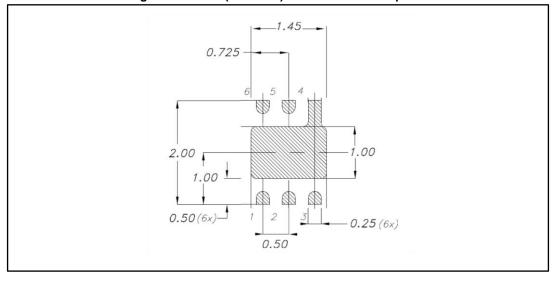

Figure 3: Pin connections (top view)

Table 2: Pin description

| Pin                                              | Symbol                                               | Name and function |  |

|--------------------------------------------------|------------------------------------------------------|-------------------|--|

| 1                                                | IN                                                   | Input voltage     |  |

| 2                                                | NC                                                   | Not connected     |  |

|                                                  |                                                      | Enable input.     |  |

| 3                                                | 3 EN Set V <sub>EN</sub> > 0.9 to turn on the device |                   |  |

| Set V <sub>EN</sub> < 0.4 to turn off the device |                                                      |                   |  |

| 4                                                | GND                                                  | Ground            |  |

| 5                                                | NC                                                   | Not connected     |  |

| 6                                                | OUT                                                  | Output voltage    |  |

Exposed pad is electrically connected to GND.

LDLN015 Maximum ratings

# 3 Maximum ratings

**Table 3: Absolute maximum ratings**

| Symbol           | Parameter                            | Value                              | Unit |

|------------------|--------------------------------------|------------------------------------|------|

| Vin              | DC input voltage                     | -0.3 to 7                          | V    |

| V <sub>OUT</sub> | DC output voltage                    | From -0.3 to 4.6                   | V    |

| V <sub>EN</sub>  | Enable input voltage                 | From -0.3 to V <sub>IN</sub> + 0.3 | V    |

| Іоит             | Output current                       | Internally limited                 | mA   |

| P <sub>D</sub>   | Power dissipation                    | Internally limited                 | mW   |

| T <sub>STG</sub> | Storage temperature range            | -65 to 150                         | °C   |

| Тор              | Operating junction temperature range | -40 to 125                         | °C   |

| ECD.             | Human body model                     | ±3                                 | kV   |

| ESD              | Machine model                        | ±300                               | V    |

Absolute maximum ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied.

Table 4: Thermal data

| Symbol             | Parameter                           | Value | Unit |

|--------------------|-------------------------------------|-------|------|

| R <sub>thJA</sub>  | Thermal resistance junction-ambient | 105   | °C/W |

| R <sub>th</sub> JC | Thermal resistance junction-case    | 20    | °C/W |

Electrical characteristics LDLN015

### 4 Electrical characteristics

$T_J$  = 25 °C,  $V_{IN}$  =  $V_{OUT(NOM)}$  + 1 V,  $C_{IN}$  =  $C_{OUT}$  = 0.47  $\mu F,\ I_{OUT}$  = 1 mA,  $V_{EN}$  =  $V_{IN},\ unless$  otherwise specified.

**Table 5: Electrical characteristics**

| Symbol                  | Parameter                                                                 | Test condition                                                                                                                         | Min. | Тур.     | Max.      | Unit              |

|-------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------|----------|-----------|-------------------|

| V <sub>IN</sub>         | Operating input voltage                                                   |                                                                                                                                        | 2.1  |          | 5.5       | V                 |

|                         |                                                                           | I <sub>OUT</sub> = 1 mA                                                                                                                | -1   |          | 1         |                   |

| Vоит                    | V <sub>OUT</sub> accuracy                                                 | -40 °C < T <sub>J</sub> < 125 °C,<br>I <sub>OUT</sub> = from 1 mA to 150 mA,<br>V <sub>IN</sub> = V <sub>OUT(NOM)</sub> + 1 V to 5.5 V | -2   |          | 2         | %                 |

| $\Delta V_{\text{OUT}}$ | Static line regulation                                                    | $V_{OUT}$ + 1 V $\leq$ V <sub>IN</sub> $\leq$ 5.5 V,<br>$I_{OUT}$ = 1 mA                                                               |      | 0.005    |           | %/V               |

| $\Delta V_{OUT}$        | Static load regulation                                                    | I <sub>OUT</sub> = 1 mA to 150 mA                                                                                                      |      | 0.001    |           | %/mA              |

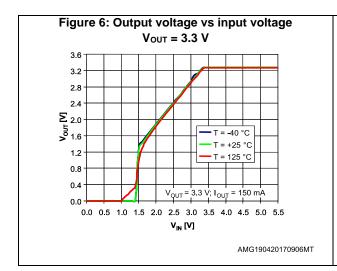

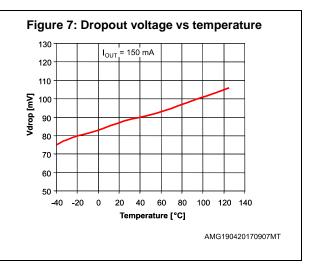

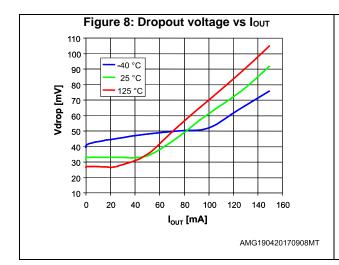

| VDROP                   | Dropout voltage (1)                                                       | I <sub>OUT</sub> = 150 mA,<br>V <sub>OUT</sub> > 1.9 V<br>-40 °C < T <sub>J</sub> < 125 °C                                             |      | 86       | 180       | mV                |

|                         |                                                                           | 10 Hz to 100 kHz,<br>Iout = 0 mA,<br>Vout = 1.0 V                                                                                      |      | 6.3      |           | .,                |

| en                      | Output noise voltage                                                      | 10 Hz to 100 kHz,<br>I <sub>OUT</sub> = 150 mA,<br>V <sub>OUT</sub> = 1.0 V                                                            |      | 9.9      |           | μV <sub>RMS</sub> |

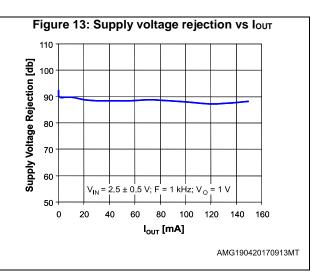

|                         | SVR Supply voltage rejection Vout = 1.0 V                                 | V <sub>IN</sub> = V <sub>OUTNOM</sub> + 1 V +/-V <sub>RIPPLE</sub> V <sub>RIPPLE</sub> = 0.5 V Freq. = 1 kHz I <sub>OUT</sub> = 10 mA  |      | 92       |           |                   |

| SVR                     |                                                                           | VIN = VOUTNOM + 1 V +/-VRIPPLE VRIPPLE = 0.5 V Freq. = 10 kHz IOUT = 10 mA                                                             |      | 89       |           | dB                |

|                         | VIN = VOUTNOM + 1 V+/-VRIPPLE VRIPPLE = 0.5 V Freq. = 100 kHz IOUT = 1 mA |                                                                                                                                        | 50   |          |           |                   |

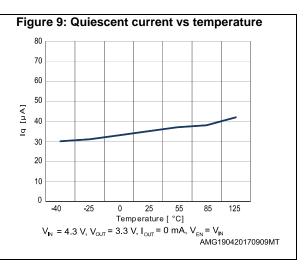

| lα                      | Quiescent current                                                         | IOUT = 0 mA,<br>-40 °C < TJ < 125 °C<br>IOUT = 150 mA,<br>-40 °C < TJ < 125 °C                                                         |      | 35<br>70 | 60<br>120 | μА                |

|                         |                                                                           | $V_{IN}$ input current in OFF mode $V_{EN} = \text{GND}$                                                                               |      | 0.002    | 2         |                   |

| I <sub>SC</sub>         | Short-circuit current                                                     | R <sub>L</sub> = 0<br>V <sub>IN</sub> = 2.0 V                                                                                          | 300  |          |           | mA                |

#### LDLN015 Electrical characteristics

| Symbol            | Parameter                | Test condition                                                        | Min. | Тур. | Max. | Unit |

|-------------------|--------------------------|-----------------------------------------------------------------------|------|------|------|------|

|                   | Enable input logic low   | V <sub>IN</sub> = 2.1 V to 5.5 V,<br>-40 °C < T <sub>J</sub> < 125 °C |      |      | 0.4  | V    |

| Ven               | Enable input logic high  | V <sub>IN</sub> = 2.1 V to 5.5 V,<br>-40 °C < T <sub>J</sub> < 125 °C | 0.9  |      |      | V    |

| I <sub>EN</sub>   | Enable pin input current | V <sub>EN</sub> = 5.5 V                                               |      | 0.1  | 100  | nΑ   |

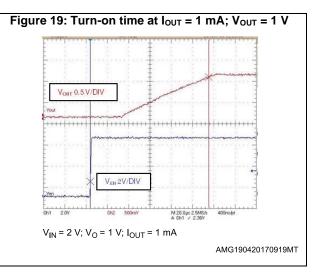

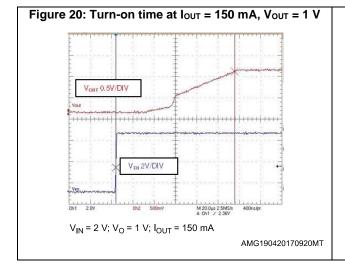

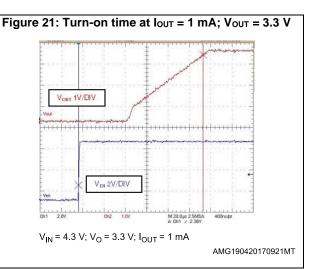

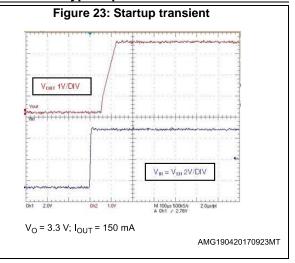

| Ton               | Turn-on time (2)         |                                                                       |      | 110  |      | μs   |

| Т                 | Thermal shutdown         |                                                                       |      | 166  |      | ٥°   |

| T <sub>SHDN</sub> | Hysteresis               |                                                                       |      | 10   |      |      |

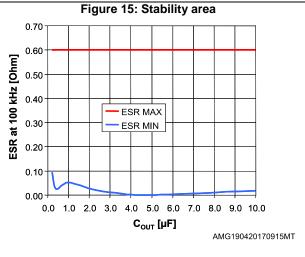

| Соит              | Output capacitor         | Capacitance (see Figure 15: "Stability area")                         | 0.33 |      | 4.7  | μF   |

#### Notes:

#### Note:

- For  $V_{OUT(NOM)} < 1.0 \text{ V}$ ,  $V_{IN} = 2 \text{ V}$

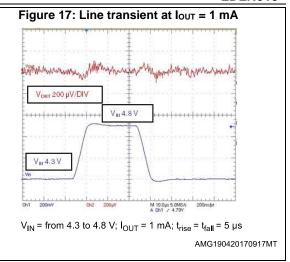

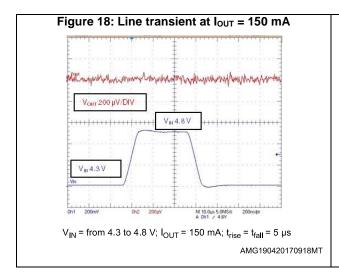

- All transient values are guaranteed by design, not production tested

<sup>&</sup>lt;sup>(1)</sup>Dropout voltage is the input-to-output voltage difference at which the output voltage is 100 mV below its nominal value. This specification does not apply for output voltages below 2 V.

$<sup>^{(2)}</sup>$ Turn-on time is time measured between the enable input just exceeding V<sub>EN</sub> high value and the output voltage just reaching 95% of its nominal value.

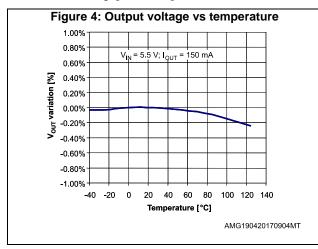

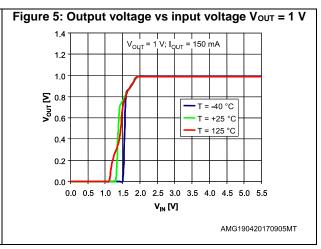

## 5 Typical performance characteristics

577

8/16

Figure 12: Supply voltage rejection vs frequency

100

100

100

1000

10000

100000

100000

100000

100000

100000

Package information LDLN015

## 6 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: **www.st.com**. ECOPACK® is an ST trademark.

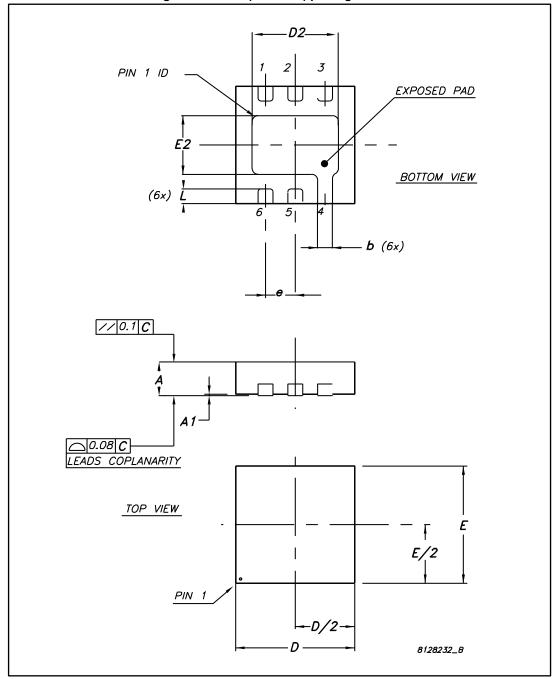

### 6.1 DFN6 (2 x 2 mm) package information

Figure 24: DFN6 (2 x 2 mm) package outline

Table 6: DFN6 (2 x 2 mm) mechanical data

| Dim  | mm   |      |      |  |

|------|------|------|------|--|

| Dim. | Min. | Тур. | Max. |  |

| А    | 0.51 | 0.55 | 0.60 |  |

| A1   | 0    | 0.02 | 0.05 |  |

| b    | 0.18 | 0.25 | 0.30 |  |

| D    |      | 2.00 |      |  |

| D2   | 1.30 | 1.45 | 1.55 |  |

| Е    |      | 2.00 |      |  |

| E2   | 0.85 | 1.00 | 1.10 |  |

| е    |      | 0.50 |      |  |

| L    | 0.15 | 0.25 | 0.35 |  |

Figure 25: DFN6 (2 x 2 mm) recommended footprint

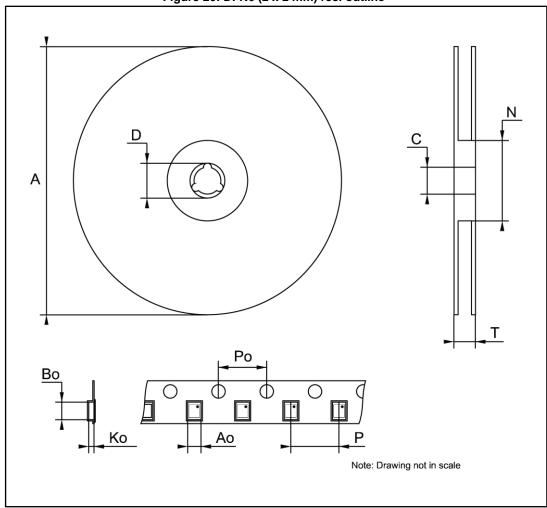

# 6.2 DFN6 (2 x 2 mm) packing information

Figure 26: DFN6 (2 x 2 mm) reel outline

Table 7: DFN6 (2 x 2 mm) tape and reel mechanical data

| rable 1. bi No (2 x 2 iiiii) tape and reel mechanical data |      |      |      |  |

|------------------------------------------------------------|------|------|------|--|

| Dim.                                                       |      | mm   |      |  |

|                                                            | Min. | Тур. | Max. |  |

| А                                                          |      |      | 180  |  |

| С                                                          | 12.8 |      | 13.2 |  |

| D                                                          | 20.2 |      |      |  |

| N                                                          | 60   |      |      |  |

| Т                                                          |      |      | 14.4 |  |

| A0                                                         |      | 2.4  |      |  |

| В0                                                         |      | 2.4  |      |  |

| K0                                                         |      | 1.3  |      |  |

| P0                                                         |      | 4    |      |  |

| Р                                                          |      | 4    |      |  |

LDLN015 Revision history

# 7 Revision history

**Table 8: Document revision history**

| Date        | Revision | Changes                                                                                                                                                                                                                                                                      |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-Jan-2012 | 1        | Initial release.                                                                                                                                                                                                                                                             |

| 15-Jan-2014 | 2        | Changed the LDLN015xx to LDLN015.  Updated the Description in cover page.  Updated Table 1: Device summary, Section 5: Typical performance characteristics and Section 6: Package information.  Added Section 6.2: DFN6 (2 x 2 mm) packing information.  Minor text changes. |

| 14-Jan-2015 | 3        | Updated the features in cover page.  Updated Table 5: Electrical characteristics and Figure 9: Quiescent current vs. temperature.  Minor text changes.                                                                                                                       |

| 26-Oct-2015 | 4        | Modified Section 6: Package information. Minor text changes.                                                                                                                                                                                                                 |

| 18-May-2017 | 5        | Updated Section 6.1: "DFN6 (2 x 2 mm) package information".  Minor text changes.                                                                                                                                                                                             |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics - All rights reserved