### STP410N4F7AG

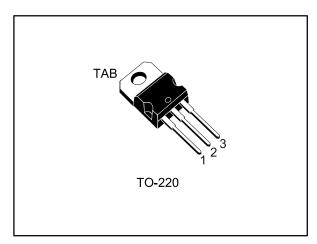

# Automotive-grade N-channel 40 V, 1.5 mΩ typ., 180 A STripFET™ F7 Power MOSFET in a TO-220 package

Datasheet - production data

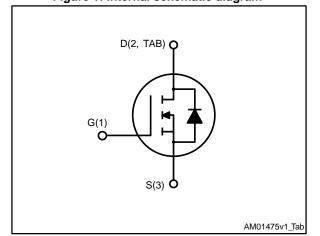

Figure 1: Internal schematic diagram

#### **Features**

| Order code   | V <sub>DS</sub> | R <sub>DS(on)</sub> max. | Ι <sub>D</sub> | Ртот  |

|--------------|-----------------|--------------------------|----------------|-------|

| STP410N4F7AG | 40 V            | 1.8 mΩ                   | 180 A          | 365 W |

- Designed for automotive applications and AEC-Q101 qualified

- Among the lowest R<sub>DS(on)</sub> on the market

- Excellent FoM (figure of merit)

- Low C<sub>rss</sub>/C<sub>iss</sub> ratio for EMI immunity

- High avalanche ruggedness

### **Applications**

Switching applications

### **Description**

This N-channel Power MOSFET utilizes STripFET™ F7 technology with an enhanced trench gate structure that results in very low onstate resistance, while also reducing internal capacitance and gate charge for faster and more efficient switching.

**Table 1: Device summary**

| Order code   | Marking | Package | Packing |

|--------------|---------|---------|---------|

| STP410N4F7AG | 410N4F7 | TO-220  | Tube    |

Contents STP410N4F7AG

### Contents

| 1 | Electric | cal ratings                         | 3  |

|---|----------|-------------------------------------|----|

| 2 | Electric | cal characteristics                 | 4  |

|   | 2.1      | Electrical characteristics (curves) | 6  |

| 3 | Test cir | ·cuits                              | 8  |

| 4 | Packag   | e information                       | 9  |

|   | 4.1      | TO-220 package information          | 10 |

| 5 | Revisio  | on history                          | 12 |

STP410N4F7AG Electrical ratings

# 1 Electrical ratings

Table 2: Absolute maximum ratings

| Symbol                         | Parameter                                                | Value     | Unit |  |

|--------------------------------|----------------------------------------------------------|-----------|------|--|

| V <sub>DS</sub>                | Drain-source voltage                                     | 40        | V    |  |

| $V_{GS}$                       | Gate-source voltage                                      | ±20       | ٧    |  |

| Ip <sup>(1)</sup>              | Drain current (continuous) at T <sub>case</sub> = 25 °C  | 180       | ۸    |  |

| ID <sup>17</sup>               | Drain current (continuous) at T <sub>case</sub> = 100 °C | 180       | Α    |  |

| I <sub>DM</sub> <sup>(2)</sup> | Drain current (pulsed)                                   | 720       | Α    |  |

| Ртот                           | Total dissipation at T <sub>case</sub> = 25 °C           | 365       | W    |  |

| E <sub>AS</sub> (3)            | Single pulse avalanche energy                            | 1.9       | J    |  |

| T <sub>stg</sub>               | Storage temperature range                                | 55 to 175 | °C   |  |

| Tj                             | Operating junction temperature range                     |           |      |  |

#### Notes:

Table 3: Thermal data

| Symbol                | Parameter                               | Value | Unit           |  |

|-----------------------|-----------------------------------------|-------|----------------|--|

| R <sub>thj-case</sub> | Thermal resistance junction-case        | 0.41  | 9 <b>C</b> AA4 |  |

| R <sub>thj-amb</sub>  | Thermal resistance junction-ambient max | 62.5  | °C/W           |  |

$<sup>^{(1)}</sup>$  Current is limited by package, the current capability of the silicon is 350 A at 25  $^{\circ}\text{C}.$

<sup>(2)</sup> Pulse width is limited by safe operating area.

$<sup>^{(3)}</sup>T_j \le 175~^{\circ}C, I_{av}=80A$

Electrical characteristics STP410N4F7AG

### 2 Electrical characteristics

(T<sub>case</sub> = 25 °C unless otherwise specified)

Table 4: Static

| Symbol              | Parameter                             | Test conditions                                                                  | Min. | Тур. | Max. | Unit |

|---------------------|---------------------------------------|----------------------------------------------------------------------------------|------|------|------|------|

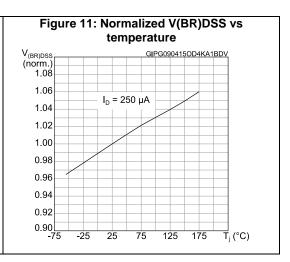

| $V_{(BR)DSS}$       | Drain-source breakdown voltage        | $V_{GS} = 0 \text{ V}, I_{D} = 250 \mu\text{A}$                                  | 40   |      |      | V    |

|                     | Zoro goto voltago drain               | $V_{GS} = 0 \text{ V}, V_{DS} = 40 \text{ V}$                                    |      |      | 10   |      |

| IDSS                | Zero gate voltage drain<br>current    | $V_{GS} = 0 \text{ V}, V_{DS} = 40 \text{ V},$ $T_{case} = 125 \text{ °C}^{(1)}$ |      |      | 100  | μΑ   |

| Igss                | Gate-body leakage current             | V <sub>DS</sub> = 0 V, V <sub>GS</sub> = 20 V                                    |      |      | 200  | nA   |

| V <sub>GS(th)</sub> | Gate threshold voltage                | $V_{DS} = V_{GS}$ , $I_D = 250 \mu A$                                            | 2.5  |      | 4.5  | V    |

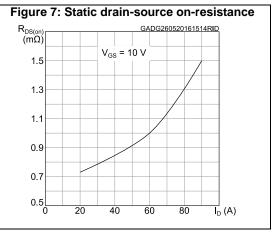

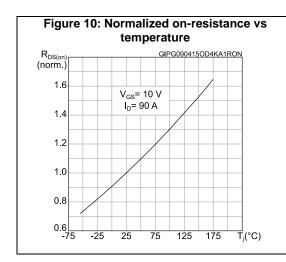

| R <sub>DS(on)</sub> | Static drain-source on-<br>resistance | V <sub>GS</sub> = 10 V, I <sub>D</sub> = 90 A                                    |      | 1.5  | 1.8  | mΩ   |

#### Notes:

Table 5: Dynamic

| Symbol           | Parameter                    | Test conditions                                                     | Min. | Тур.  | Max. | Unit |

|------------------|------------------------------|---------------------------------------------------------------------|------|-------|------|------|

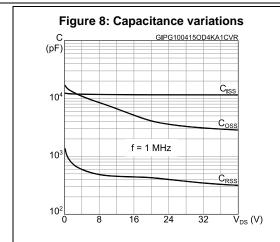

| Ciss             | Input capacitance            |                                                                     | -    | 11700 | ı    |      |

| Coss             | Output capacitance           | V <sub>DS</sub> = 25 V, f = 1 MHz, V <sub>GS</sub> = 0 V            | -    | 3500  | ı    | pF   |

| C <sub>rss</sub> | Reverse transfer capacitance | VBS = 20 V, 1 = 1 Winz, VBS = 0 V                                   | -    | 390   | ı    | Pi   |

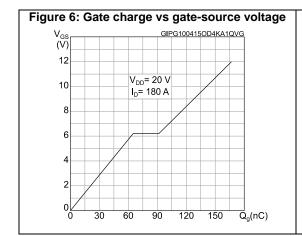

| $Q_g$            | Total gate charge            | $V_{DD} = 20 \text{ V}, I_D = 180 \text{ A}, V_{GS} = 10 \text{ V}$ | -    | 140   | ı    |      |

| Qgs              | Gate-source charge           | (see Figure 14: "Test circuit for                                   | -    | 65    |      | nC   |

| $Q_{\text{gd}}$  | Gate-drain charge            | gate charge behavior")                                              | -    | 27    | -    |      |

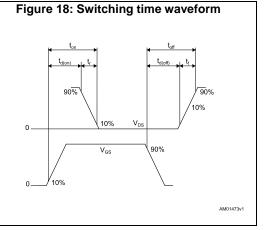

Table 6: Switching times

| Symbol              | Parameter           | Test conditions                                                                   | Min. | Тур. | Max. | Unit |

|---------------------|---------------------|-----------------------------------------------------------------------------------|------|------|------|------|

| t <sub>d(on)</sub>  | Turn-on delay time  | $V_{DD} = 20 \text{ V}, I_D = 90 \text{ A R}_G = 4.7 \Omega,$                     | -    | 35   | -    |      |

| tr                  | Rise time           | V <sub>GS</sub> = 10 V (see Figure 13: "Test circuit for resistive load switching | -    | 200  | -    |      |

| t <sub>d(off)</sub> | Turn-off delay time |                                                                                   | -    | 110  | -    | ns   |

| tf                  | Fall time           | times" and )                                                                      | -    | 44   | -    |      |

<sup>&</sup>lt;sup>(1)</sup>Defined by design, not subject to production test.

Table 7: Source-drain diode

| Symbol                         | Parameter                | Test conditions                                                                                         | Min. | Тур. | Max. | Unit |

|--------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------|------|------|------|------|

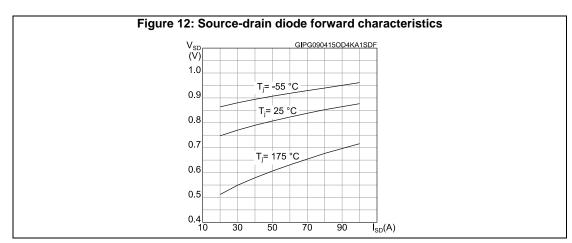

| I <sub>SD</sub> <sup>(1)</sup> | Source-drain current     |                                                                                                         | -    |      | 180  | Α    |

| V <sub>SD</sub> <sup>(2)</sup> | Forward on voltage       | V <sub>GS</sub> = 0 V, I <sub>SD</sub> = 90 A                                                           | -    |      | 1.3  | V    |

| t <sub>rr</sub>                | Reverse recovery time    | I <sub>SD</sub> = 180 A, di/dt = 100 A/μs,                                                              | 1    | 74.4 |      | ns   |

| Q <sub>rr</sub>                | Reverse recovery charge  | V <sub>DD</sub> = 32 V, T <sub>j</sub> = 25 °C (see <i>Figure 15</i> : "Test circuit for inductive load | 1    | 115  |      | nC   |

| I <sub>RRM</sub>               | Reverse recovery current | switching and diode recovery times")                                                                    | -    | 3.1  |      | Α    |

#### Notes:

$<sup>^{(1)}</sup>$  Current is limited by package, the current capability of the silicon is 350 A at 25  $^{\circ}$ C.

$<sup>^{(2)}</sup>$  Pulse test: pulse duration = 300  $\mu s,$  duty cycle 1.5%.

# 2.1 Electrical characteristics (curves)

Figure 2: Safe operating area GADG260520161425SOA Ι<sub>D</sub> (A) 10<sup>2</sup> t<sub>p</sub>= 100µs Operation in this area is limited by R<sub>DS(on)</sub> 10<sup>1</sup> t<sub>p</sub>= 1ms T <sub>j</sub>≤ 175 °C T<sub>c</sub>= 25 °C t<sub>p</sub>= 10ms single pulse 10°  $\bar{V}_{DS}(V)$ 10° 10<sup>1</sup>

Figure 3: Thermal impedance K GADG260520161440ZTH  $\delta$ =0.5 0.2 0.01 0.05 0.02 0.01 Single pulse  $Z_{n=k^*R_{npc}}^{-k^*R_{npc}}$   $\delta$ =b/T  $\delta$ =b/T  $\delta$ =10 $^{-1}$   $\delta$  10 $^{-2}$  10 $^{-1}$   $\delta$  (s)

Figure 4: Output characteristics

GADG260520161449OCH

(A)

V<sub>GS</sub> = 7, 8, 9, 10 V

250

V<sub>GS</sub> = 6 V

200

V<sub>GS</sub> = 5.5 V

150

0

1 2 3 4 5 V<sub>DS</sub> (V)

Figure 9: Normalized gate threshold voltage vs temperature

V<sub>GS(th)</sub>

(norm.)

1.2

1.0

I<sub>D</sub> = 250 µA

0.8

0.6

0.4

0.2

-75 -25 25 75 125 175 T<sub>j</sub> (°C)

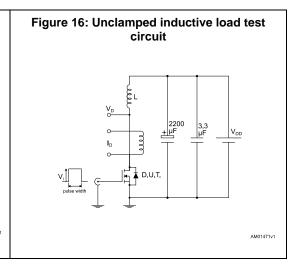

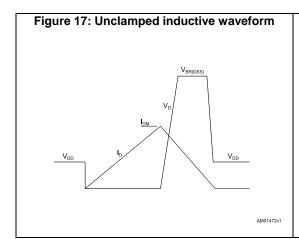

Test circuits STP410N4F7AG

### 3 Test circuits

Figure 13: Test circuit for resistive load switching times

Figure 14: Test circuit for gate charge behavior

12 V 47 kΩ 100 nF D.U.T.

Vos 1 1 kΩ 100 nF D.U.T.

AM01469v1

Figure 15: Test circuit for inductive load switching and diode recovery times

577

# 4 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: **www.st.com**. ECOPACK® is an ST trademark.

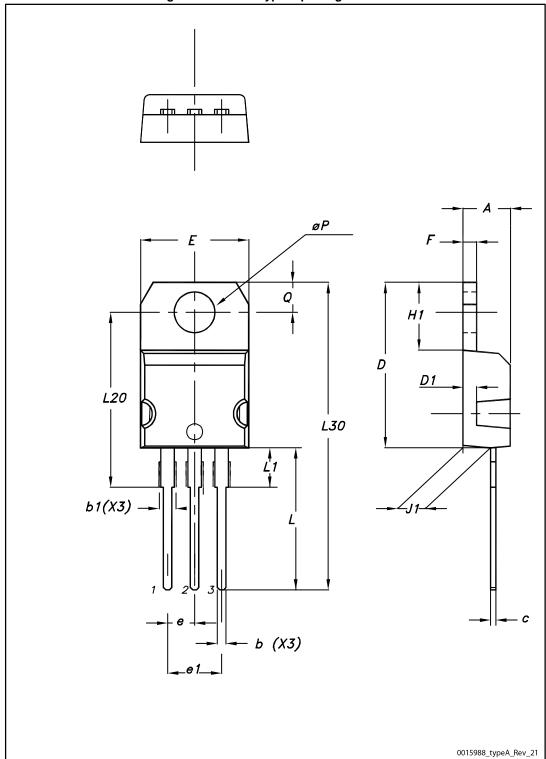

# 4.1 TO-220 package information

Figure 19: TO-220 type A package outline

Table 8: TO-220 type A mechanical data

| Dim  | mm    |       |       |

|------|-------|-------|-------|

| Dim. | Min.  | Тур.  | Max.  |

| А    | 4.40  |       | 4.60  |

| b    | 0.61  |       | 0.88  |

| b1   | 1.14  |       | 1.55  |

| С    | 0.48  |       | 0.70  |

| D    | 15.25 |       | 15.75 |

| D1   |       | 1.27  |       |

| E    | 10.00 |       | 10.40 |

| е    | 2.40  |       | 2.70  |

| e1   | 4.95  |       | 5.15  |

| F    | 1.23  |       | 1.32  |

| H1   | 6.20  |       | 6.60  |

| J1   | 2.40  |       | 2.72  |

| L    | 13.00 |       | 14.00 |

| L1   | 3.50  |       | 3.93  |

| L20  |       | 16.40 |       |

| L30  |       | 28.90 |       |

| øΡ   | 3.75  |       | 3.85  |

| Q    | 2.65  |       | 2.95  |

Revision history STP410N4F7AG

# 5 Revision history

**Table 9: Document revision history**

| Date        | Revision | Changes        |

|-------------|----------|----------------|

| 25-May-2016 | 1        | First release. |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics - All rights reserved